10月初,与AMD和Apple等公司合作的台湾芯片制造商台积电发表

了两项声明。 首先,该公司设法改进了其7纳米制程技术,并使用新技术制造了该芯片。 第二个-5纳米芯片将于2019年发布。 这些发展的前景描述如下。

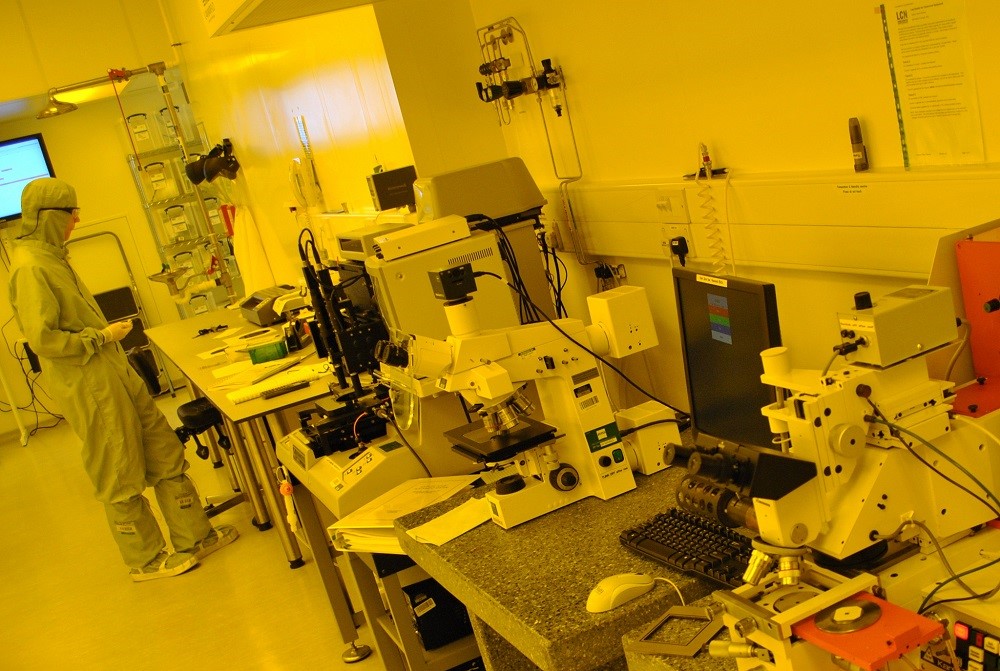

/照片UCL CC

/照片UCL CC7nm台积电制程技术

台积电在本月初印刷的芯片基于第二代7纳米制程技术,与前代产品相比已经发生了许多变化。

第一代台积电的7纳米工艺技术基于具有“深”紫外辐射的

DUV光刻技术。 在这种情况下

,将使用波长为193 nm的浸没式光刻和扫描仪。 公司于今年四月印刷了该技术中的第一款芯片。 台积电在五月份

开始为苹果生产7nm芯片。 A12 Bionic芯片系统

随附了新芯片。 她已经负责IT巨人的最新智能手机的工作:iPhone XR,XS和XS Max。

总共有来自两家公司的订单,包括Bitmain,NVIDIA和Qualcomm。 AMD还是台积电

的主要客户-Vega 20处理器和Epyc服务器CPU均基于7纳米工艺技术构建。

台积电本月早些时候报道,他们能够改进其7nm制程技术。 工程师使用“硬”紫外线(

EUV )中的光刻技术来开发芯片。 在这种情况下,波长小

二十倍且为13.5 nm 。 与第一代技术相比,改用EUV(连同对缺陷和其他过程进行建模和检测的方法的开发)已将制造电路的功耗

降低了 8%,并将晶体管的密度提高了20%。

到目前为止,仅使用EUV实现了芯片的四个非关键层。 首先,该公司希望掌握该技术,然后将其用于制造大量产品(而合适的设备的产量却很低)。

制造商没有透露谁成为第一个接收新芯片的客户,但是有一个假设是

苹果公司是相同的 。 该公司还在为汽车行业开发更新过程技术的专业版本。

什么时候等待5nm芯片

台积电计划于2019年开始冒险生产5nm芯片。 该公司使用EUV来创建5纳米微电路,但是使用这种光刻方法,将生产14层芯片,而不是4层。

届时,一家台湾公司计划突破EUV技术并提高产能。 该公司已经

宣布开始建造新工厂,在那里将生产芯片。 它将架设在台湾南部科学园内。

5nm芯片比7nm具有多个优势。 在相同的复杂度下,更新芯片中晶体管的密度

将提高 1.8倍,时钟频率将提高15%。 在这种情况下,5纳米处理器将比7纳米能耗低20%。 但是,在开始生产之前,公司需要解决许多困难。

首先是

缺乏开发工具。 5纳米制程技术所需的EDA设计套件将在今年11月准备就绪。 但是,仅在明年夏天准备好PCIe 4.0和USB 3.1单元的库。

另一个问题是开发成本高。 据专家介绍,使用7纳米技术在芯片上开发系统的

成本约为1.5亿美元。 在5nm制程技术的情况下,成本增加到2.5亿美元。 这意味着最终产品的价格将最终上涨,并且更少的客户公司将对使用这些芯片感兴趣。 因此,不能保证使用5纳米制程技术的微电路生产将获得回报。

其他公司情况如何?

在我们以前的一篇文章中,我们说

GlobalFoundries集成电路制造商由于财务困难而

停止了其7、5和3纳米工艺技术的开发。 取而代之的是,该组织改用14nm工艺并创建嵌入式存储设备。

/ photo Seb Mr CC / 22nm英特尔硅晶圆

/ photo Seb Mr CC / 22nm英特尔硅晶圆英特尔在开发新制造工艺的速度上也正在失去台积电。 该公司再次

推迟了 10纳米芯片的发布,并于9月宣布将

返回22纳米芯片(尽管已实施芯片组),以“减轻”生产能力。 但是,可以公平地说,就晶体管的密度和尺寸而言,台积电(TSMC)的7纳米和英特尔的10纳米

被认为是相同的设计标准。

到目前为止,三星

是台积电在7纳米和5纳米领域

的唯一竞争对手。 三星计划在明年上半年推出7纳米芯片。 根据5纳米三星设计标准的芯片也将在2019年开始生产,但是当它们开始销售时,仍然未知。

PS关于虚拟基础架构并与PD配合使用-在我们的

Telegram频道中 :