在我

有关使用赛普拉斯的UDB微控制器模块PSoC控制RGB LED的文章的评论中

,建议在文章开头简要介绍一下UDB是什么是很好的。 正如我已经在文章中指出的那样,我无法简短地介绍UDB,但是您可以简单地将公司文档传送给它,以使家用阅读器熟悉如此强大的工具来实现固件功能。

但是首先,让我们看一下PSoC的全部含义。 PSoC是赛普拉斯的一系列芯片组,用于实施片上系统。 不同的系列具有不同的处理器内核(对于PSoC 3,它是MCS-51;对于PSoC 4,它是Cortex M0;对于PSoC 5LP,它是Cortex M3;对于PSoC 6,它一次是两个:Cortex M0 +和Cortex M4)和一组可编程逻辑。 而且,这种逻辑不是纯数字的;那里有模拟的东西。 除了一组不同的ADC外,还有模拟开关。 您甚至可以通过模拟电路以编程方式连接支脚,但是,电路的电阻将以千克为单位。 PSoC内部有可以通过编程方式切换的运算放大器,这意味着您可以在其上构建不同的模拟模块。

顺便说一下,PSoC可以由2.7至5.5伏的任何电压供电。 也就是说,您无需考虑使用电池电源或USB电源的任何稳定器。

但是我纯粹是用一个红字写关于模拟事物的文章。 现在,我们将专注于数字事物。 大多数现代控制器具有功能强大的外围设备,可提供多种功能。 但是实际上,在每个特定的软件开发中,这些模块并未得到充分利用,而只是部分使用。 而且在PSoC中,与传统的FPGA逻辑类似,实现了程序逻辑,而不是一堆好的逻辑。 因此,通过将它们包括在所需的那些模式中,可以精确地实现在其上所需的那些块。 并且资源不应该花费在未使用的模式上,而将它们分配给实现某种自己的事物。

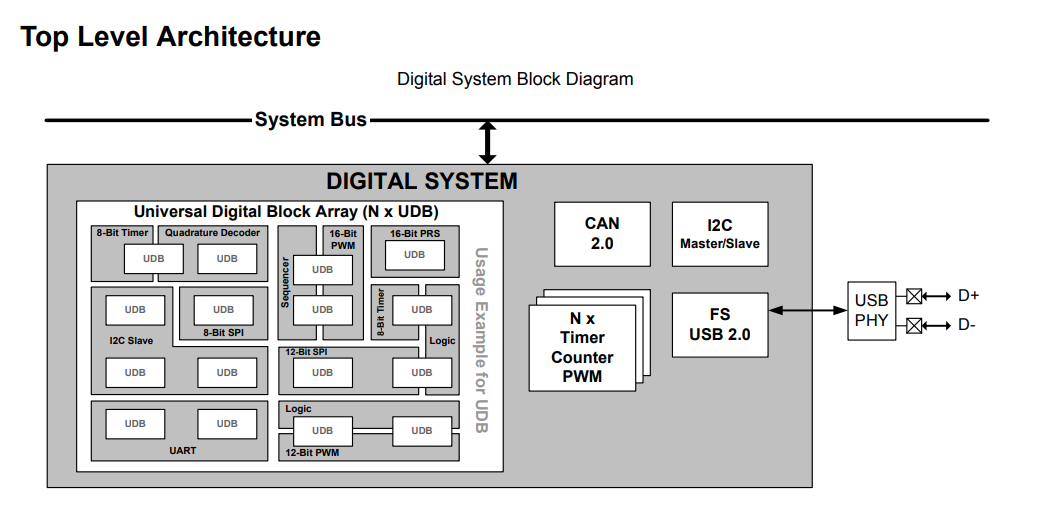

在这里经常会产生一些误解。 许多开发人员已经习惯了存在两种类型的可编程逻辑集成电路(FPGA):CPLD和FPGA。 因此,许多听说过PSoC的人都相信,存在一种可以在Veriolg中编程的CPLD盒。 实际上,是和否。 确实有一定数量的PLD(不带“ C”,只有PLD),您可以在Verilog上对其进行编程。 但是实际上,这些PLD是UDB模块的一部分。 而UDB是在PSoC中实现的可编程逻辑的主要元素。 该块是非常原始的,为开发人员提供了最广泛的机会。 考虑公司文档中的图,该图说明了使用UDB块的本质。

由于我以PSoC 5LP系列为例学习了所有内容,因此我将其文档翻译成本文。 但是,在开始之前,我先说说这些控制器的价格。 如果您去Ali Express看看他们的面包板,就会感到难过。 坦白地说,与STM32-DISCOVERY相比,它们仍然是什么,但与STM32F103C8T6原型相比,它们有点贵。 首先,这是由于公司实体模型始终没有一个,而是两个这样的控制器这一事实。 即使目标控制器和PSoC 4(后者通常不具有USB端口),JTAG功能也会在PSoC 5LP上实现。

但是将价格除以二,我们仍然可以得到它的价格高于STM32F103的价格,后者在处理器内核上相似。 但是,如果我们从外部甚至将最简单的CPLD添加到完全相同的STM32中,那么总价格将对PSoC有利。 并且,我们将在这两种情况的连接中添加一些遗漏的部分(PSoC内部具有所有连接)。 以及木板每平方厘米的价格。 因此,事实证明,如果您只需要使用处理器内核,则实际上不需要PSoC。 如果需要将某些功能带入固件或硬件级别,则需要PSoC。 在它上面,该系统将变得更便宜,更容易。

实际上,我有一个狂躁的想法,试图为我们的RTOS MAX内核提供硬件支持。 为此,我研究了开发用于Altera V SoC的Bare Metal应用程序的方法(可惜,事实证明,那里的体系结构功能可以降低操作系统的速度,但您不能加快它的速度-对硬件的单个请求会带来疯狂的延迟)。 为此,我开始精通PSoC。 我还没有达到内核超频(只有一般的想法),但是我真的很喜欢UDB编程的想法。 当然,我现在有兴趣将这种想法带给尽可能多的国内程序员。 因此,我们着手翻译UDB上赛普拉斯专有文档的相应部分。 章和附图的编号根据原始文件进行维护。

循环的一般内容“ UDB。 这是什么?

第1部分。简介。 请 (当前文章)

第2部分。数据路径。第3部分。数据路径FIFO。第4部分。数据路径ALU。第5部分。数据路径。 有用的小东西。第6部分。管理和状态模块。第7部分。时序和复位控制模块第8部分。处理UDBUDB。 这是什么 第一部分

21.通用数字模块

在本章中,我们将研究通用数字模块(UDB)如何实现可编程数字外设功能的开发。 UDB体系结构在配置的粒度和有效的实现之间取得了平衡。 UDB由类似于可编程逻辑矩阵(PLM,英文PLD)的非换向逻辑,结构化逻辑(操作机,以下称为数据路径)和灵活的跟踪方案组成。

21.1功能

- 为了获得最佳的灵活性,每个UDB都包含以下组件:

基于8位指令存储库,几个寄存器和FIFO缓冲区的基于ALU(算术和逻辑单元,ALU)的8位数据路径;

•两个PLD,每个PLD具有12个输入,八个连词(产品术语PT)和四个宏单元输出;

•管理和状态寄存器;

•时钟和复位模块。 - PSoC 5LP包含最大为24 UDB的阵列。

- UDB数组元素之间的灵活跟踪。

- UDB元素可以拆分或链接以创建更大的功能。

- 灵活实现多种数字功能,包括计时器,计数器,脉宽调制器(包括带有死区发生器的PWM),UART,I2C总线,SPI总线和CRC验证/生成。

21.2框图

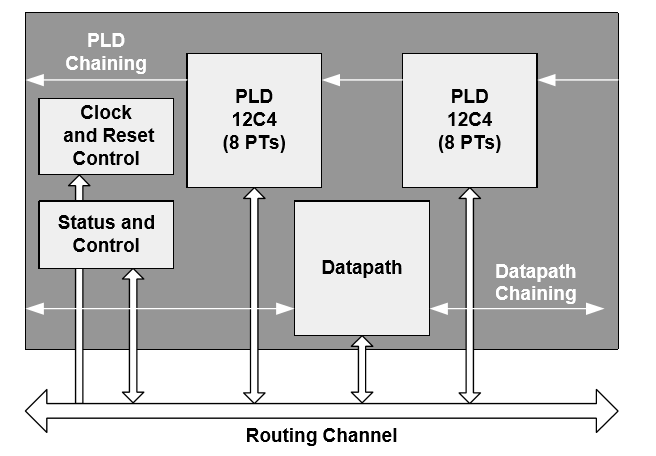

图21-1将UDB构造为包含两个基本逻辑块(PLD,数据路径)以及控制,状态,时钟和复位功能的结构。

图21-1。 UDB的框图。

图21-1。 UDB的框图。21.3工作原理

UDB的主要组件是:

- PLD(2)。 来自跟踪资源的数据被馈送到这些块的输入。 它们实现了组合逻辑和数据捕捉,从而允许您实现有限状态机,控制Datapath块的操作,配置输入条件和控制输出。

- 数据路径。 该模块包含动态可编程的ALU,四个寄存器,两个FIFO缓冲器,比较器和条件生成。

- 管理和状态(状态和控制)。 这些模块提供了用于中央处理器(CPU)的微程序交互以及与UDB操作同步的机制。 控制寄存器作用于内部元件,状态寄存器读取外部元件的状态。

- 时钟和复位控制 这些模块在UDB中提供时序选择和启用以及复位选择。

- 链接信号。 PLD和数据路径具有允许您将链中的相邻块链接在一起以创建更高位功能的信号。

- 追踪渠道 UDB通过可编程交换矩阵连接到跟踪通道,以在同一UDB内的块之间进行通信,并与阵列中的其他UDB进行通信。

- 系统总线接口(系统总线接口)。 每个UDB中的所有寄存器和RAM都投影到系统地址空间上,可以使用中央处理器或通过8位和16位形式的直接内存访问(英文直接内存访问,DMA)来访问它们。数据。

21.3.1。 ld

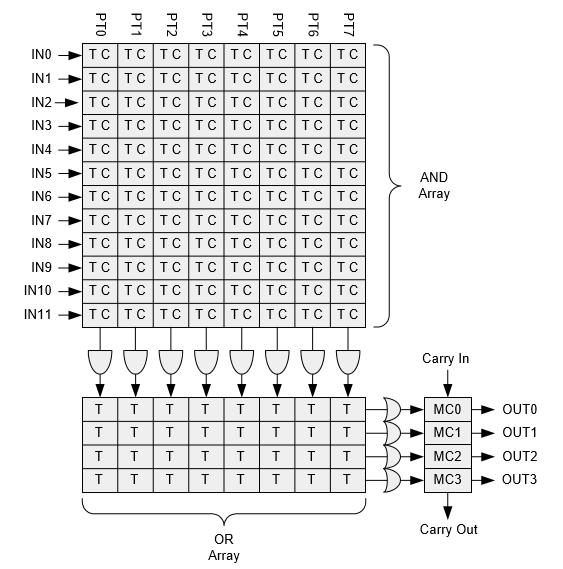

每个UDB有两个12C4 PLD。 图21-1中所示的PLD块可用于实现状态机,处理I / O数据以及创建表逻辑(例如,查找表,LUT)。 此外,可以将PLD配置为执行算术功能,设置数据路径序列并生成状态。 通用逻辑可以合成并投影到PLD块上。 本节概述了PLD体系结构。

PLD具有12个输入,这些输入将AND数组中的信息转换为8个连接项。 在每个连词中,您可以选择直接输入(true,T)或反向输入(complement,C)。 连词的输出进入“或”数组的输入。 12C4中的字母“ C”表示“或”项对于所有输入都是恒定的,并且每个“或”输入都可以通过编程方式访问任何连接词。 这种结构提供了最大的灵活性,并确保可以移动所有输入和输出。

图21-2。 PLD 12C4的结构。

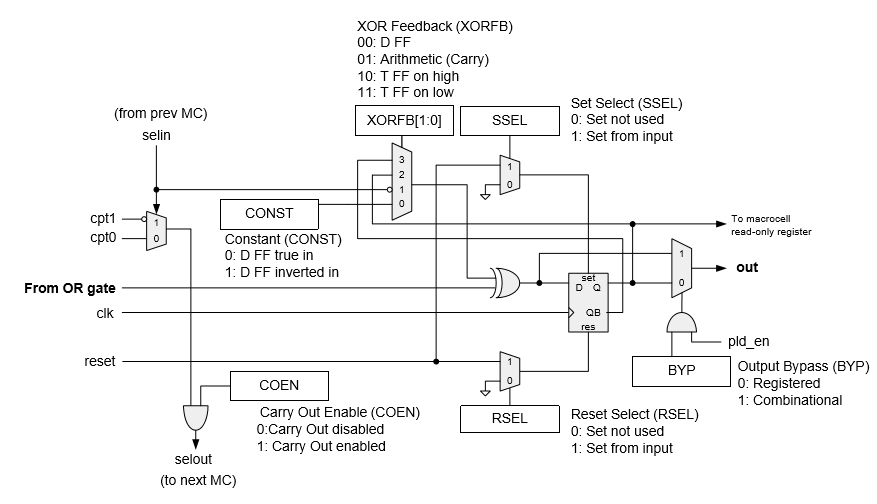

图21-2。 PLD 12C4的结构。21.3.1.1宏PLD

宏小区的架构如图21-3所示。 输出控制跟踪阵列,可以锁存或拉曼。 对于锁存,使用具有直接或反向输入的D触发器或具有高或低输入电平的T触发器。 输出触发器可以在初始化期间设置或重置,或者在正常操作期间通过来自跟踪通道的外部信号异步设置或重置。

图21-3。 宏单元架构。只读PLD宏单元寄存器

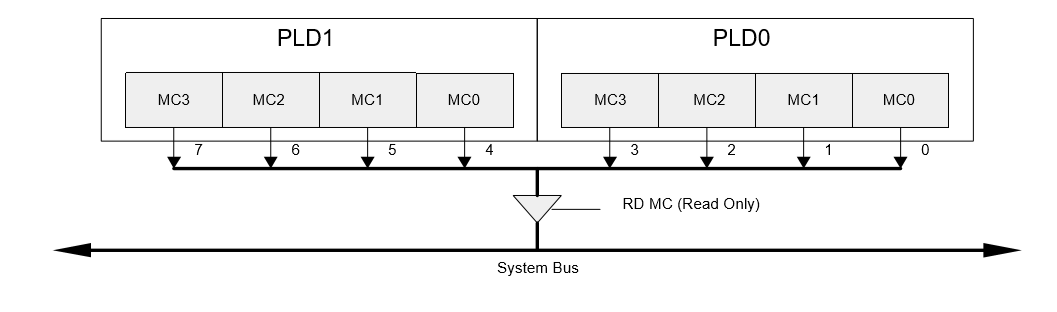

图21-3。 宏单元架构。只读PLD宏单元寄存器除了控制跟踪阵列以外,两个PLD的宏单元输出都以8位只读寄存器的形式投影到地址空间上,可以使用CPU或DMA对其进行访问。

图21-4。 只读PLD宏单元寄存器。

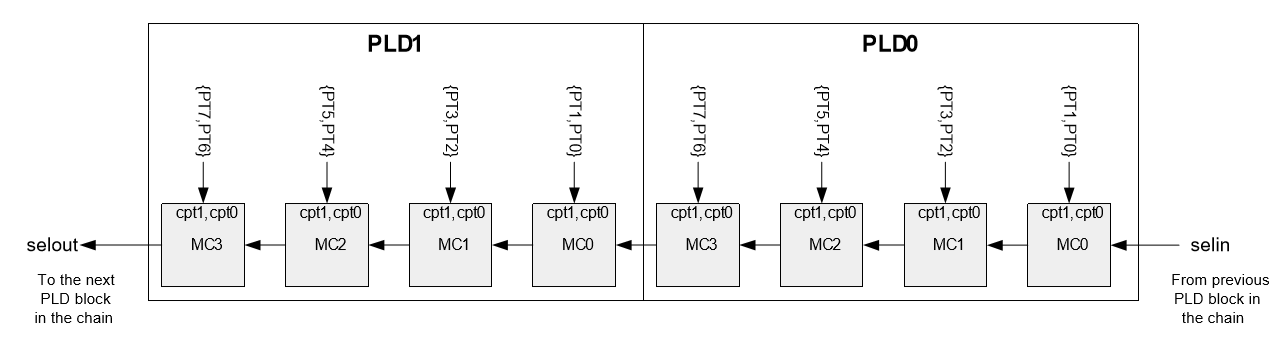

图21-4。 只读PLD宏单元寄存器。21.3.1.2连字链PLD

PLD在UDB寻址中捆绑在一起。 如图21-5所示,selin进位链的输入通过两个PLD中的每个宏单元从前一个UDB转发到电路,然后作为选择进位链的输出转发到下一个UDB。 为了支持有效放置算术函数,会生成特殊的连词(PT),将其与宏连字链一起在宏单元中使用。

图21-5。 PLD连字链和特殊的连词输入。

图21-5。 PLD连字链和特殊的连词输入。21.3.1.3 PLD配置

每个PLD以具有16位访问权限的RAM形式出现在CPU或DMA之前。 AND阵列具有12×8×2位或24个字节用于编程,而OR阵列具有4×8位或4个字节用于编程。 另外,每个宏单元具有一个配置字节,每个PLD总共32个配置字节。 由于每个UDB具有2个PLD,所以每个UDB的总配置为64字节。

下次,我们将考虑操作自动机(数据路径)。