我们将继续基于赛普拉斯文档来考虑UDB。 这次我们将详细研究可操作的自动机Datapath。

循环的一般内容“ UDB。 这是什么?

第1部分。简介。 请第2部分。数据路径。 (当前文章)

第3部分。数据路径FIFO。第4部分。数据路径ALU。第5部分。数据路径。 有用的小东西。第6部分。管理和状态模块。第7部分。时序和复位控制模块第8部分。处理UDB21.3.2操作机(数据路径)

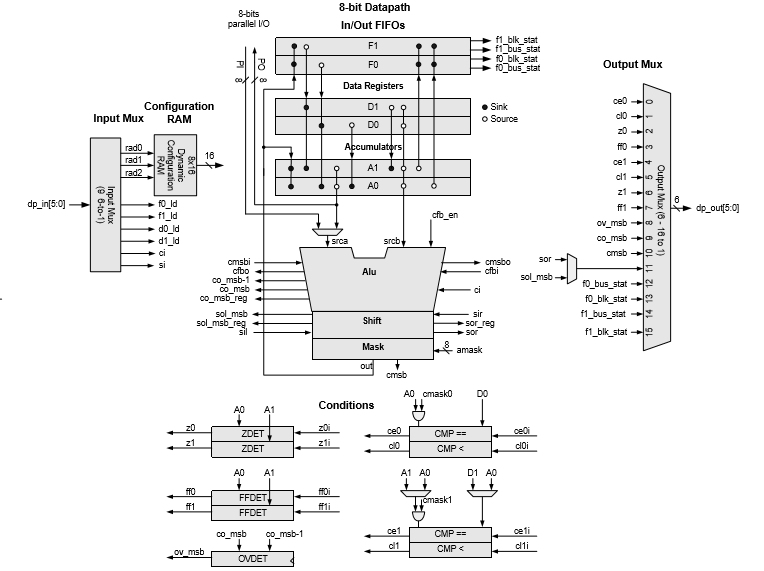

图21-6所示的数据路径包含一个8位单端ALU及其相关电路,用于比较和生成条件标志。 可以将相邻UDB的数据路径块链接在一起以增加位深度。 数据路径包括一个小的动态配置RAM,可以动态选择要在特定周期内执行的操作。

数据路径经过优化,可实现典型的嵌入式功能,例如定时器,计数器,PWM,PRS,CRC,移位寄存器和死区生成器。 添加加法和减法功能可支持数字delta-sigma操作。

图21-6。 顶级数据路径。

21.3.2.1概述

以下各章概述了数据路径的主要功能。

动态配置动态配置-在定序器的控制下,在每个周期中更改Datapath的工作和内部通信的能力。 这是通过配置存储器(配置RAM)实现的,该存储器存储八个唯一的配置。 该存储器的输入地址可以从连接到跟踪资源的任何模块转发,通常是从PLD逻辑,I / O引脚或其他数据路径转发。

铝ALU可以执行八种通用功能:递增,递减,加,减,还可以执行逻辑运算AND,OR,XOR和PASS。 功能的选择由每个周期的配置存储器决定。 ALU输出提供独立的移位操作(左,右,半字节置换)以及屏蔽操作。

条件构造每个数据路径具有两个按位屏蔽的比较器,可以将其配置为选择多个数据路径寄存器输入作为参数。 其他可识别条件可能是全零,全1和溢出。 这些条件构成了数据路径的主要输出,可以转发到数字跟踪线或其他功能的输入。

嵌入式CRC / PRSDatapath内置支持单周期CRC计算以及生成具有给定位深度和生成多项式的伪随机序列(英语伪随机序列,PRS)。 为了获得超过8位的位深度,可以在数据路径之间链接信号。 此功能是动态控制的,这意味着它可以与其他功能交替使用。

自定义高位数算术函数和移位函数的最高有效位(英语最高有效位,MSB)的编号可以通过编程设置。 这提供了对可变长度CRC / PRS功能的支持,并且与屏蔽ALU输出一起,允许实现任意长度的计时器,计数器和移位块。

FIFO输入/输出缓冲器每个数据路径都有两个4字节FIFO缓冲区,每个缓冲区都可以配置为用作输入缓冲区(CPU或DMA将数据写入FIFO,数据路径读取FIFO)或作为输出缓冲区(数据路径写入FIFO,以及CPU或DMA)从中读取)。 这些FIFO缓冲区生成的状态可以转发以与定序器,中断或DMA请求进行交互。

链式数据路径可以配置为将条件和信号链接到相邻的数据路径。 移位,传输,捕获和其他条件信号可以按链组合以创建更高位深度的算术函数,以及移位函数和CRC / PRS函数。

时分复用在过采样应用中或不需要高时钟速度的情况下,可以在两组寄存器和条件生成器之间有效分配Datapath中的一个ALU。 ALU和移位寄存器的输出被锁存,可以在后续周期中用作输入。 使用示例包括支持一个(8位)数据路径中的16位功能,或将CRC生成操作与数据移位操作交替使用。

数据路径输入数据路径具有四种类型的输入:配置,控制以及数据输入(串行和并行)。 配置输入选择动态配置的RAM地址。 控制输入从FIFO加载数据寄存器,并将电池输出下载到FIFO。 串行数据输入包括移位和进位输入。 并行数据输入端口允许您从跟踪资源接收多达8个数据位。

数据路径输出总共在Datapath中生成了16个信号。 其中一些是条件信号(例如,比较),另一些是状态信号(例如,FIFO状态),其余是数据信号(例如,移位寄存器输出)。 这16个信号被多路复用为6个数据路径输出,并路由到跟踪矩阵。 默认情况下,输出与时钟频率同步,这会以1个时钟周期的延迟创建流水线。 同样,它们的(输出)可以切换到异步(组合)模式(请参阅翻译说明)。

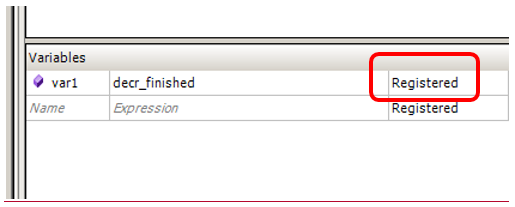

译者注我搜索了很长时间以了解数据路径输出的时间。 根据我的经验,所有内容都是异步的。 事实证明,这与其说是输出的状态,不如说是基于这些变量的编辑器设置。 这将迫使编辑器生成以下Verilog代码:

这将迫使编辑器生成以下Verilog代码:/* ==================== Assignment of Registered Variables ==================== */ always @ (posedge clock) begin : register_assignments var1 <= (decr_finished); end

如果切换到组合模式 代码将变成这样:

代码将变成这样: assign var1 = (decr_finished);

但这一切都适用于从数据路径输出生成的变量。 输出本身始终是异步的。 并且可以使用它们的名称(在此示例中为decr_finished )而无需输入其他变量。数据路径工作寄存器每个数据路径模块都有六个8位工作寄存器。 CPU或DMA具有对所有寄存器的读写访问权限。

表21-1在下一篇文章中,我们将开始处理FIFO。