我们将继续将赛普拉斯的专有文档转换为UDB模块。 而且,一切都非常吻合。 要继续

关于UDB的

实用文章,您将需要使用FIFO,并且在理论部分我们已经对它们进行了非常详细的描述。 因此,我们开始详细研究它们。

循环的一般内容是“ UDB。 这是什么?

第1部分。简介。 请第2部分。数据路径。第3部分。数据路径FIFO。 (当前文章)

第4部分。数据路径ALU。第5部分。数据路径。 有用的小东西。第6部分。管理和状态模块。第7部分。时序和复位控制模块第8部分。处理UDB21.3.2.2数据路径FIFO

FIFO模式和配置

每个FIFO缓冲区都有几种可用的操作模式和配置:

表21-2。 FIFO模式和配置。

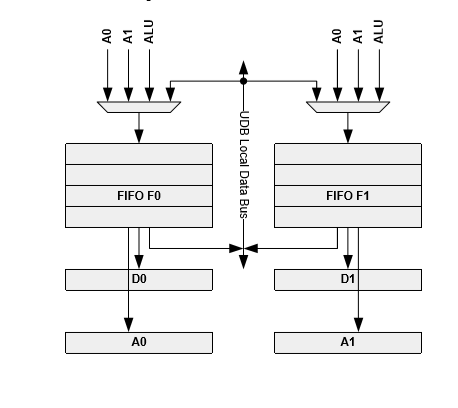

图21-7显示了FIFO对的可能配置选项,具体取决于为每个FIFO选择的输入/输出模式。 如果一个FIFO处于输入模式,而另一个FIFO处于输出模式,则得到RX / TX配置。 需要这种配置的典型示例是SPI总线控制器。

双捕获配置(两个FIFO配置为输出)提供对A0和A1对的独立捕获,或者对A0或A1寄存器的两个独立捕获。 最后,在

双缓冲模式下(均为输入),可以使用一个寄存器对或两个独立的寄存器进行加载或比较。

图21-7。 FIFO配置。

图21-8详细显示了FIFO的源和接收器。

图21-8。 FIFO源和接收器。

当FIFO在输入缓冲模式下工作时,源是系统总线,接收器是Dx和Ax寄存器。 在输出缓冲模式下工作时,源是Ax和ALU寄存器,接收器是系统总线。 多路复用器选择在UDB CFG15配置寄存器中静态设置,如F0_INSEL [1:0]或F1_INSEL [1:0]的表所示:

表21-3。 UDB配置寄存器中的一组FIFO多路复用器。

FIFO状态

每个FIFO生成两个状态信号“总线”和“块”,它们通过数据路径输出多路复用器传输到UDB跟踪资源。 总线状态可用于中断或请求对FIFO的DMA读/写。 “块”状态主要用于将FIFO状态传递给内部UDB实体。 状态位的用途取决于配置的方向(Fx_INSEL [1:0])和FIFO级别位。 在工作寄存器空间的辅助控制寄存器中设置FIFO级别位(Fx_LVL)。 下表显示了状态选项:

表21-4。 FIFO状态选项。

FIFO工作图

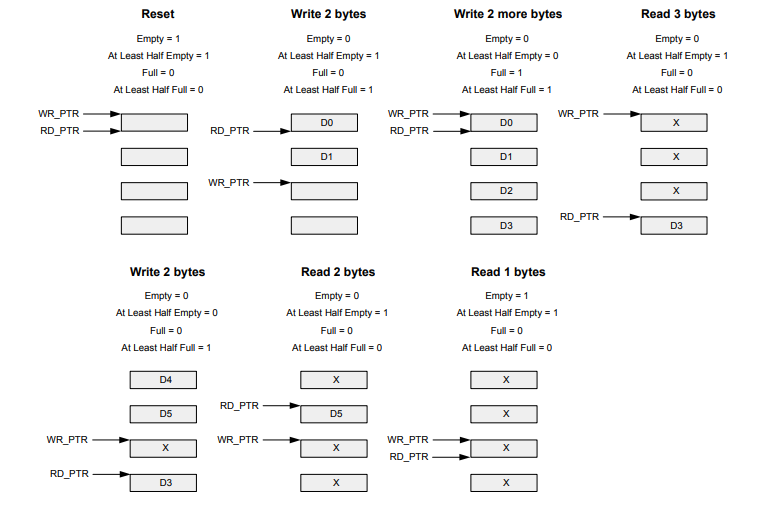

图21-9显示了典型的读写顺序,以及与这些操作相关的状态的产生。 在图中,读写发生在不同的时间,但是它们可以同时执行。

图21-9 FIFO接收器操作

FIFO快速模式(FIFO FAST)

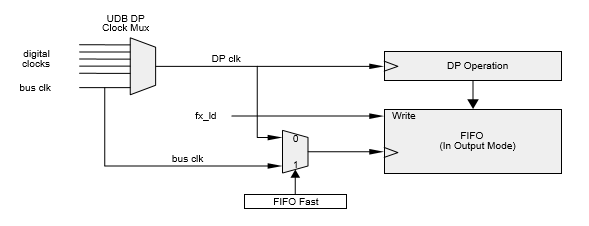

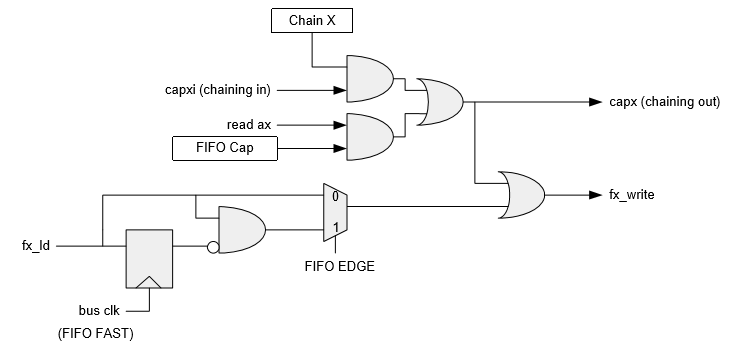

当FIFO处于输出缓冲模式时,FIFO引导操作通常使用所选数据路径的时钟频率为写信号提供时钟。 如图21-10所示,选择FIFO快速模式(FIFO FAST)时,可以选择此特定操作的总线频率。 当与“电

平/边沿=边沿”模式结合使用时,此操作可减少从电池到FIFO的从数据路径时钟周期到总线时钟周期的传输延迟,因为总线频率可能更高。 这允许CPU或DMA以最小的延迟读取接收到的FIFO结果。

如图21-10所示,无论当前的Datapath时钟如何,都会执行快速启动操作,但是,使用总线时钟速度会增加功耗。

图21-10。 FIFO快速配置接收器。

FIFO边沿/电平记录模式(差分/电平)

数据路径的FIFO中有两种记录模式。 在第一种模式下,数据从电池同步传输到FIFO。 该记录的控制信号(FX_LD)通常由状态机或与数据路径时钟同步的条件产生。 在输入负载控制信号为“ 1”的任何周期内都将执行对FIFO的写操作。 在第二种模式下,FIFO用于响应FX_LD信号的上升沿来捕获电池值。 在这种模式下,信号的信号格式是任意的(但是,其周期必须至少等于一个数据路径时钟周期)。 此模式的一个示例是使用外部脚的输入作为触发器来捕获电池电量。 此模式的局限性在于,在检测到另一个正差之前,输入参数必须至少一个周期返回值“ 0”。

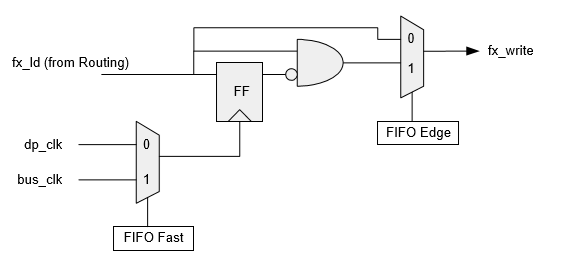

图21-11显示了FX_LD输入上的差分检测模式的实现。 UDB中两个FIFO的模式都由同一位控制,切换此选项。 注意,差分检测的时钟频率等于所选FIFO的频率。

图21-11。 内部FIFO记录接收器的差分检测。

FIFO软件捕获模式

一个共同而重要的要求是使CPU和DMA在正常操作期间可靠地读取电池的内容。 这是使用软件捕获完成的,并使用FIFO上限配置位使能。 该位适用于UDB中的两个FIFO,但仅在FIFO处于输出缓冲区模式时才有效。 使用软件捕获时,F0必须从A0读取,F1必须从A1读取。

如图21-12所示,读取电池将启动从电池写入FIFO的操作。 信号链接在一条链中,因此,同时读取一个特定字节可捕获链中所有UDB的电池值。 这使8位处理器可以成功地同时读取16位或更多位。 读取电池时返回的数据应被忽略,捕获的值可立即从FIFO中读取。

跟踪的FX_LD信号(产生FIFO负载)与程序捕获信号一起发送到OR项。 当同时使用硬件和软件捕获时,结果可能无法预测。 通常,这些功能应该互斥,但是,在以下情况下可以同时使用硬件和软件捕获:

- FIFO捕获时钟模式设置为FIFO FAST。

- FIFO记录模式设置为FIFO EDGE。

在上述条件下,硬件和软件捕获的工作原理相同,并且在任何总线时钟周期内,这些信号中的任何一个都可以触发捕获。

还建议在程序捕获开始之前清除程序代码(ACTL寄存器)中的目标FIFO。 因此,FIFO读和写指针将被设置为已知状态。

图21-12。 软件捕获配置。

译者注:

很长一段时间我都无法理解本节的含义。 然后很长一段时间,我确定该部分是为PSoC3编写的,其8位内核不能访问的字节数以上。 但是,当创建转换的第八部分时 ,事实证明,即使在PSoC5LP中,对于所有32位ARM处理器内核,也可以以八位或十六位模式访问工作的UDB寄存器。 从文档来看,仅此而已。 这就是所描述的功能派上用场的地方。

FIFO控制位

辅助控制寄存器可在正常操作期间用于控制FIFO,包含4位。

FIFO0 CLR和FIFO1 CLR位用于复位或清除FIFO。 当为这些位之一分配值“ 1”时,相关的FIFO被复位。 该位必须恢复为其原始值(0),FIFO才能继续工作。 如果该位值保持等于1,则将禁用相应的FIFO,并将其用作无状态的单字节缓冲区。 可以将数据写入FIFO,可以立即读取数据,并且可以随时覆盖。 仍可以使用FX INSEL配置位[1:0]设置数据方向。

FIFO0 LVL和FIFO1 LVL位确定FIFO将阻塞状态位

“总线”的电平 (总线读取或写入FIFO时)。 也就是说,

“总线”状态的状态取决于给定的方向,如下表所示。

表21-5。 FIFO电平控制位

FIFO异步操作

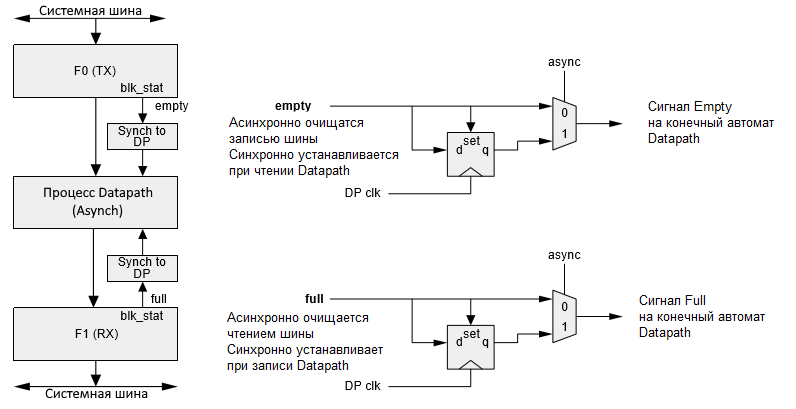

图21-13显示了异步FIFO操作的原理。 例如,假设F0在输入缓冲模式下工作,而F1在输出缓冲模式下工作,这是TX和RX寄存器的典型配置。

图21-13。 异步FIFO操作。

在TX端,数据路径状态机使用

Empty标志来确定是否有任何字节可用于接收。

Empty值是与Datapath状态机同步设置的,并且由于来自总线的写入而被异步清除。 清洗后,状态再次与数据路径状态机同步。

在RX端,RX状态机使用

Full来确定是否有空闲空间可写入FIFO。

Full值与Datapath状态机同步设置,由于总线读取而被异步清除。 清洗后,状态再次与数据路径状态机同步。

一个FIFO ASYNCH位用于启用该同步方法,激活后,该方法将应用于两个FIFO。

它仅适用于“

块”状态,因为假定

总线状态由中断过程自然同步。

表21-6。

块 FIFO状态同步选项。

操作期间FIFO溢出

为了安全地实现内部(数据路径)和外部(CPU或DMA)读写操作,应使用FIFO状态信号。 没有内置的清空和溢出条件保护。 如果FIFO已满,并且执行了后续写操作(溢出),则新数据将覆盖FIFO的开头(当前正在输出的数据是读取队列中的下一个)。 如果FIFO为空并且执行了后续读取(清空或耗尽),则读取值不确定。 FIFO指针保持准确,无论是否发生下溢和溢出。

FIFO时钟反转

每个FIFO都有一个控制位Fx CK INV,该位负责时钟FIFO的极性。关于时钟数据路径的极性。 默认情况下,FIFO与数据路径时钟具有相同的极性。 当该位为1时,FIFO相对于数据路径具有相反的极性。 这为双向交换数据(例如SPI)提供了协议支持。

动态FIFO控制

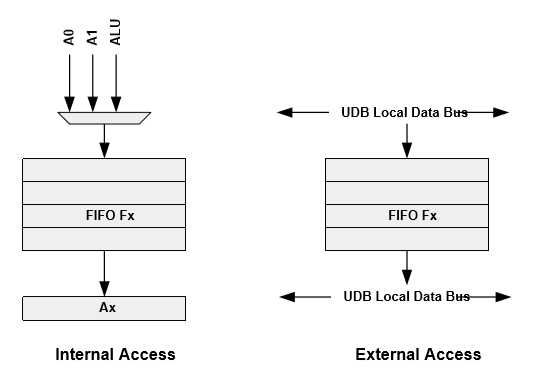

通常,FIFO是在输入缓冲模式或输出缓冲模式下静态配置的。 或者,每个FIFO可以配置为在动态控制方向(在外部信号的影响下)的模式下运行。 每个FIFO(Fx DYN)一个配置位负责激活此模式。 图21-14显示了FIFO动态模式下可用的配置。

图21-14。 动态FIFO模式。

在内部访问模式下,数据路径可以读写FIFO。 在此配置中,为了选择FIFO中的写操作源,必须将Fx INSEL位设置为1。Fx INSEL = 0(CPU总线源)在此模式下不正确,它只能采用值1、2或3(A0,A1或ALU) ) 值得注意的是,读取只能访问适当的电池,该模式下数据寄存器的方向不可用。

在外部访问模式下,CPU或DMA可以读取或写入FIFO。

通过转发来自Datapath的信号,配置可以在外部访问和内部访问之间动态切换。 为此,使用输入信号数据路径d0_load和d1_load。 值得注意的是,在动态控制模式下,从F0 / F1加载寄存器D0 / D1时,d0_load和d1_load无法正常使用。 Dx_load信号可以由任何跟踪信号(包括常量)触发。

考虑一个示例,其中从外部访问(dx_load == 1)开始,CPU或DMA可以将一个或多个字节的数据写入FIFO。 然后,当切换到内部访问(dx_load == 0)时,Datapath可以对数据执行操作。 之后,当切换到外部访问时,CPU或DMA可以读取计算结果。

由于Fx INSEL应始终为01、10或11(A0,A1或ALU),这对应于正常操作期间的“输出缓冲区模式”,因此FIFO状态信号具有以下定义(取决于Fx LVL参数):

表21-7。 FIFO状态。

由于数据路径和CPU都可以从FIFO中写入和读取,因此这些信号不再被视为块和总线状态。 blk_stat信号用于写入状态,而bus_stat信号用于读取状态

21.3.2.3 FIFO状态

有四个FIFO状态信号,每个FIFO有两个:fifo0_bus_stat,fifo0_blk_stat,fifo1_bus_stat和fifo1_blk_stat。这些信号的含义取决于特定FIFO的方向,该方向由静态配置确定。FIFO状态在21.3.2.2数据路径FIFO中有详细描述。在下一部分中,我们将继续分析算术逻辑单元(ALU)。