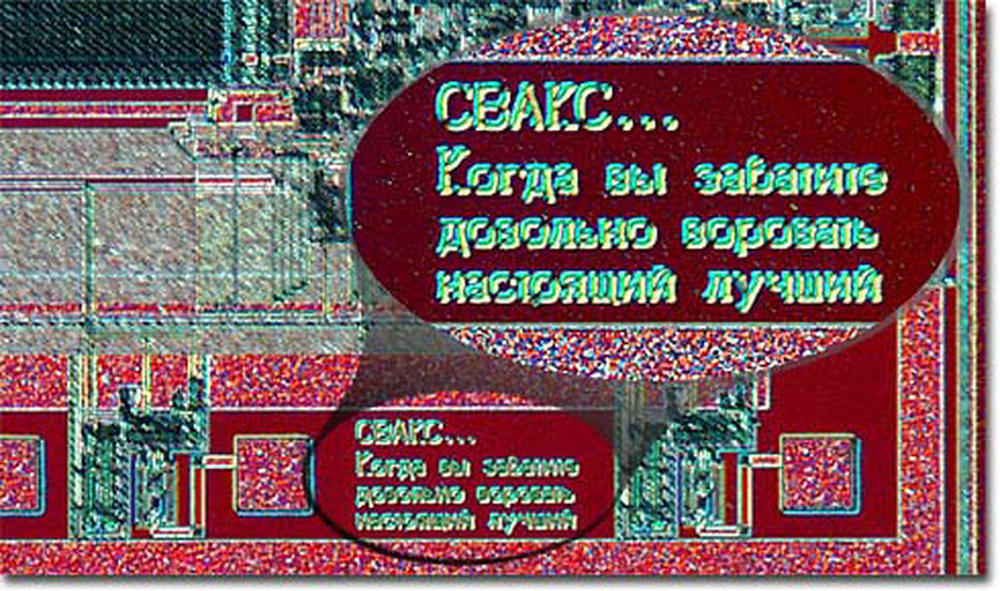

“ CVAX-当您相当抢手时,才是真正的最佳选择。”

“ CVAX-当您相当抢手时,才是真正的最佳选择。”美国工程师在微处理器拓扑中为苏联同事留下的铭文。

从微电子技术诞生的最初几年起,微芯片的逆向工程就一直困扰着制造商。 所有苏联电子产品都建立在一个点上,现在,它们在天帝国中所做的几乎是一样的,并且不仅在它上面,而且规模更大。 实际上,逆向工程在美国,欧盟和许多其他地方都是绝对合法的,其目标(我引用美国法律)的目的是“教,分析或评估在掩模工作或电路中执行的概念或技术”。

逆向工程最常见的法律用途是专利法院和许可法院。 工业间谍活动也很普遍,尤其是因为电路(尤其是模拟电路)通常是关键知识产权,并且很少获得专利-只是为了避免IP披露和作为控告人参加专利法院。 当然,在需要保护您的知识产权而无需申请专利的情况下,开发人员和制造商正在尝试提出防止复制其开发内容的方法。

保护微芯片免受逆向工程影响的另一个同样重要的领域是确保存储在存储器中的信息的安全性。 这样的信息既可以是FPGA固件(也就是开发人员的知识产权),也可以是例如银行卡的PIN码或安全闪存驱动器的加密密钥。 我们对周围世界的信任越有价值,在处理系统的所有级别上保护此信息就越重要,硬件级别也不例外。

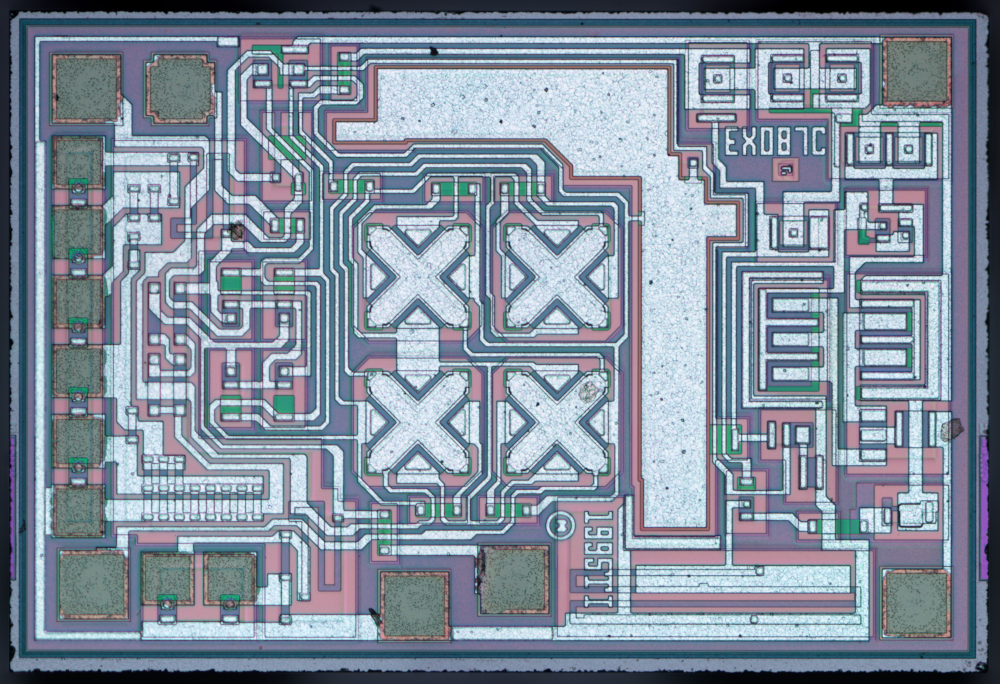

第一件事:重要的事情要理解。 谈到逆向工程和防止数据复制,必须理解,不存在绝对稳定的保护方法,而真正的目的就是使过程变得如此漫长和/或昂贵,以至于在经济上不可行。许多年前,逆向工程师或微电子海盗的工作比现在容易得多。 例如,看这张照片(感谢

BarsMonster的快乐童年和美好的照片):对技术有基本了解后,从其中恢复电路

大约需要几个小时。

图2. OPA134PA运算放大器的拓扑快照。 资料来源-zeptobars.com顺便说一下,这里有一个由Ken Shirriff从BarsMonster的照片制造的TL431芯片的逆向工程示例。 这是俄语翻译。 如果您对业余逆向工程这个话题感兴趣,那么Ken的博客中有很多很酷的东西。此处 (小心,交通情况!)是1979年Zilog Z80-CTC芯片的逆向工程报告,该报告发布后不久。 现在,这是一个独特的历史文件,然后才是具有巨大商业价值的信息(可能是在针对特殊应用的微电路的认证过程中)(通过多次参考军事标准得出)。

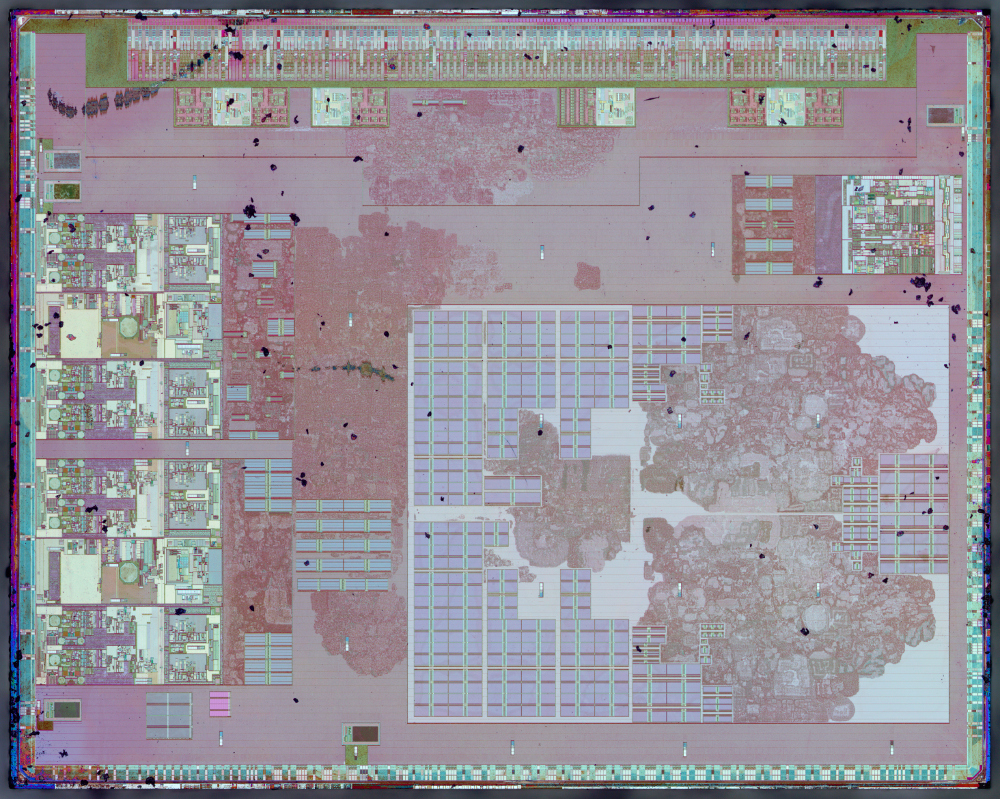

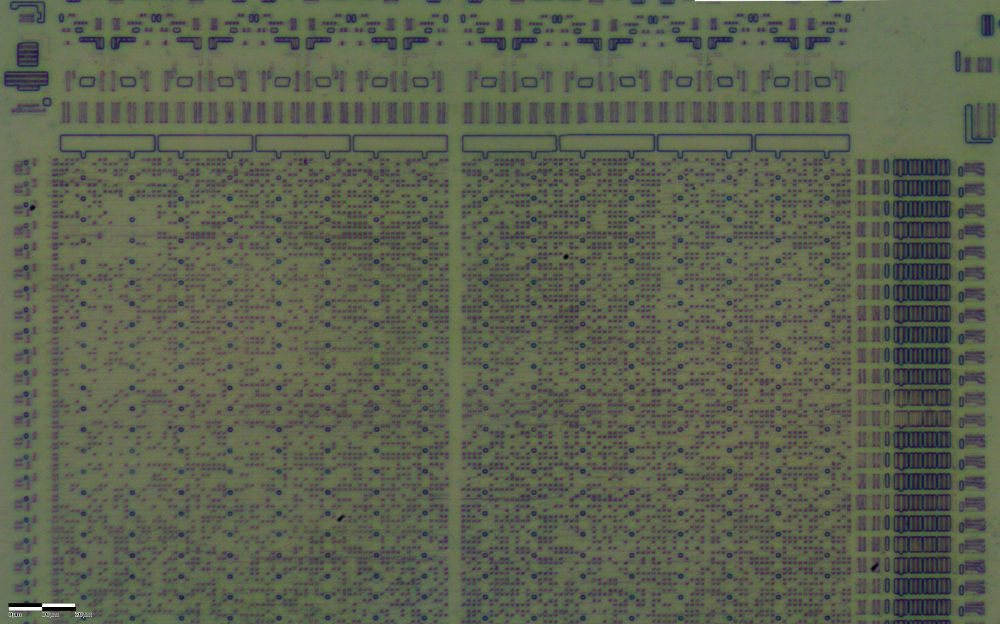

图2. OPA134PA运算放大器的拓扑快照。 资料来源-zeptobars.com顺便说一下,这里有一个由Ken Shirriff从BarsMonster的照片制造的TL431芯片的逆向工程示例。 这是俄语翻译。 如果您对业余逆向工程这个话题感兴趣,那么Ken的博客中有很多很酷的东西。此处 (小心,交通情况!)是1979年Zilog Z80-CTC芯片的逆向工程报告,该报告发布后不久。 现在,这是一个独特的历史文件,然后才是具有巨大商业价值的信息(可能是在针对特殊应用的微电路的认证过程中)(通过多次参考军事标准得出)。但是我们生活在2019年,而不是1979年,现在即使要实现高度自动化的流程,要恢复一个全新的英特尔微处理器的完整方案也要花费数月甚至数年的时间(更不用说这样的事实了:即使以可接受的分辨率删除具有设计标准的拓扑14 -10-7 nm是非常困难的任务)。 什么是英特尔? 根据上图和贝加尔-T1处理器,根据非常流行且相对负担得起的28 nm制造工艺,比较放大器的反向工程或分析工作量。 如此大的产品进行完全反向工程的情况极为罕见,通常需要关注一些特定且相对较小的模块。 例如,找出它们是否违反了您的专利,或者将您的决定与竞争对手的产品进行比较,并试图理解其优劣之处。 或者,找出来,芯片开发人员自己实现了该功能或该功能,或者借用了您的IP块。

图3.贝加尔湖T1处理器的拓扑快照。 资料来源-zeptobars.com

图3.贝加尔湖T1处理器的拓扑快照。 资料来源-zeptobars.com在这里,我们继续进行逆向工程史上的下一个重要部分。 在远古时代,整个芯片是由一家公司从头到尾开发的,有时甚至是由很小的团队或像鲍勃·维德拉(Bob Widlar)这样的才华横溢的人开发的。 现代微电路充满了IP块,其买卖是一个巨大的市场,当然,它也具有版权控制,工业间谍活动和盗版。 因此,不仅从最终产品的开发者的角度来看,而且从IP开发者的角度来看,防止产品被未经授权的复制的问题成为可能,并且有必要,IP开发者也可以是盗版者。

在黑客入侵的情况下,入侵者的内部结构通常对接收数据不感兴趣,并且进行了部分逆向工程(如果有的话),以便通过直接连接或使用其他方法来发现漏洞并利用这些漏洞。 开发人员防止黑客入侵的任务是防止使用潜在的漏洞,并在必要时破坏试图入侵的敏感数据。

表演者

首先,让我们找出谁可以保护芯片的设计。 从概念到应用的链中涉及以下实体,它们具有对微电路内容信息的不同访问类型。

- IP块开发人员。 它具有所有信息,所有必需的文件,测量方法等。 等

- 芯片开发商。 对于软IP,Verilog / VHDL具有一个阻止代码;对于硬IP,它可以具有拓扑或黑盒。 如果设备中有任何可编程或软件部分,它也可以访问它们。

- 工厂工厂 可以访问GDSII拓扑文件,但不能访问芯片的软件相关部分(例如PROM固件)。

- 包装和测试生产。 它可以访问该芯片,还可以测试一次性可编程存储器的方法和固件卡。 很少有人会故意针对它们进行防御,但它们应该在列表中,因为某些适合工厂保护的方法对他们不利。

- 竞争对手/饼干。 它只能访问成品和用户文档。

在最简单的情况下,芯片设计者(2)希望保护自己免受竞争对手(5)的复制,或者要制造具有受保护存储器的芯片,以防止未经授权的读取。 在一个稍微复杂的例子中,IP开发人员(1)希望确保该开发人员遵守许可协议的芯片(2)。 还可能发生的情况是,芯片(2)的开发人员不信任工厂(3),并怀疑它可能在夜班期间制造假冒产品。

一段时间前,我详细介绍了集成电路中的IP ,因此不再赘述。 还有一些关于IP开发人员如何保护其知识产权的信息。 简而言之,为了保护拓扑结构,工厂通常以第三方的身份参与其中,而买方则无法正确接收拓扑结构,并且使用类似于任何其他代码的混淆技术来保护Verilog代码。工具类

存在哪些微芯片分析工具? 第一级是一点点酸,首先打开微电路的外壳,然后一层又一层地去除,再用带照相机的普通光学显微镜去除。 它价格便宜,易于使用,而且对于使用最新技术制成的简单电路的分析,这已经足够了。

对于较大的方案,有特殊的CAD系统,它允许一种或另一种方式自动从拓扑恢复数据-为逆向工程师提供了比图形编辑器中绘制线更方便的工作界面。 所有现代数字电路都是从库中构建的,这也简化了自动化,在对库元素进行反向工程以组装电路之后,时间(或可用的处理能力)也成为问题。

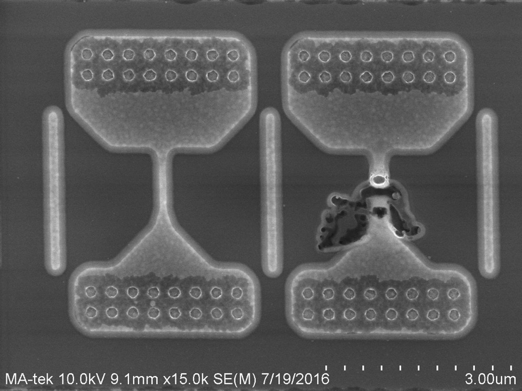

业余爱好者无法进入的下一个级别是扫描电子显微镜(SEM),它在专业实验室中却不存在。 它使用聚焦的电子束而不是光束。 SEM分辨率可以高达1 nm,甚至更低一些,足以分析任何现代集成电路。

FIB是SEM的类似物,仅使用重离子束而不是电子束。 实际上,FIB是聚焦离子束。 FIB和SEM之间的主要区别在于,借助它的帮助,您不仅可以分析微电路,还可以对其进行修改,例如,进行切割(以查看微电路的横截面或去除碎片)或喷涂材料(以在此处建立连接)哪里没有)。 FIB被微电路的开发人员和制造商广泛地用于测试样品,因为使用它来校正错误需要花费大量时间,但是与重新开始实验批次相比,FIB仍然更快,更便宜。 对于逆向工程人员来说,这也是一种独特的方法,可以达到根据开发人员的意图不应使用的晶体部分。 而且,在设计防止黑客入侵的芯片时,也必须牢记这一点。

图4.使用FIB制成的微电路的横截面。 来源-SERESSA-2015 (请注意,链接中的pdf流量很大)。

图4.使用FIB制成的微电路的横截面。 来源-SERESSA-2015 (请注意,链接中的pdf流量很大)。 图5.通过FIB修改芯片制成,更改了多个连接。

图5.通过FIB修改芯片制成,更改了多个连接。反向工程师的另一个必不可少的工具是一组激光器。 风扇可以使用强大的激光器,通过它们可以打开塑料盒中的微电路并获得进入晶体的通道。 对于专业激光器,取决于波长,微电路设计的某些部分可能是透明的,而其他部分则不是透明的。 例如,这允许您使用激光来准确地打开钝化层和绝缘层,以便以后可以方便地加入金属线,而不必冒与相邻金属线短路的风险。 其他参数将允许您切割金属或烧毁单个晶体管。 第三是通过切换缓存单元或某种逻辑线在晶体管中感应电流。 后一种选择普遍用作廉价的模拟重电荷粒子效应的方法,但是原则上,工作的微电路中的故障可能会损害其中包含的信息。 例如,重写寄存器文件中的某些标志或稍微纠正随机数生成器的操作可能会很有趣。

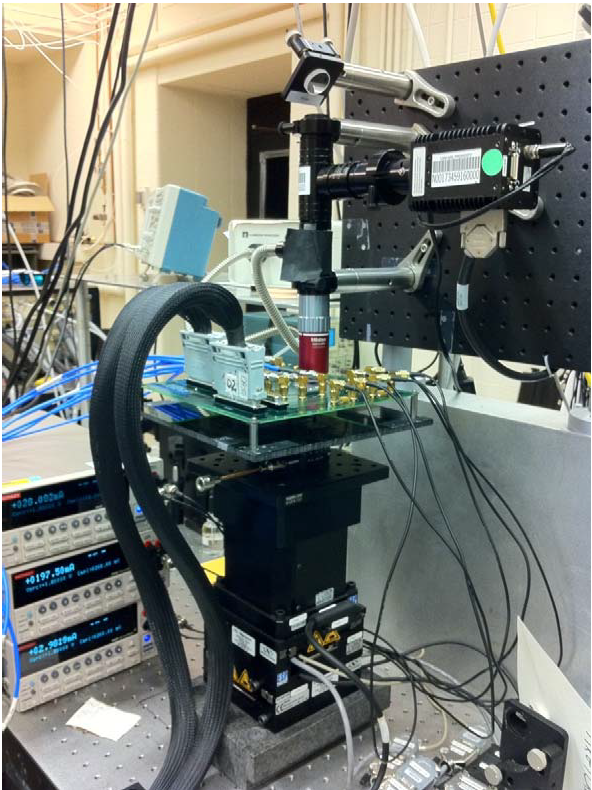

图6.激光器外观,用于研究单个故障对微电路的影响。 资料来源-SERESSA-2015。

图6.激光器外观,用于研究单个故障对微电路的影响。 资料来源-SERESSA-2015。 图7.使用激光卡获得的微电路一部分对单个故障和失败的敏感性示例。 资料来源-SERESSA-2015。

图7.使用激光卡获得的微电路一部分对单个故障和失败的敏感性示例。 资料来源-SERESSA-2015。在高级逆向工程实验室中,您可以找到许多其他有趣的工具。 例如,通过将一小片铌酸锂放在相应的线路上并再次用激光照射,可以实时监控高达几十兆赫兹的数字信号。

案例1:不相干的工厂

不信任您制造晶体的工厂的原因可能是什么? 当然,在理想的世界中,您不会参与您不信任的工厂,但有时出于商业考虑,您不得不承担风险。 可以通过两种主要方法将其最小化:

- 所谓的拆分制造,或者以简单的方式在两个工厂中生产。 但是不是并行的(通常是这样做的,以最大程度地减少因意外情况导致的缺货风险),而是并行运行在一个工厂中,而在另一工厂中。 对于该过程中的所有参与者而言,这是相当不方便的(当然并不是每个工厂都同意这一点),但这将迫使不可靠的工厂至少扭转其余的芯片设计,并自行制造缺失的掩模。 (理想情况下,应该使游戏不值得一试)。 这种方法的主要缺点是芯片的上层是金属化的,逆向工程非常简单。 但是,分体制造与金属中的某些技术诀窍相结合才能真正有效,而这种技术诀窍是不可靠的工厂无法复制的。 例如,如果您选择的第二家工厂能够在上层金属化层中制造非易失性存储器(MRAM,忆阻器或类似的东西),那么整个设计将失去其意义。

- 如果您没有任何技术知识,那么简单可靠的方法就是无需进一步编程就可以使芯片毫无意义。 可编程块可以使用配置存储器独立地制成,也可以以基于嵌入式FPGA的块的形式制成(市场上有这种IP)。 配置存储器作为一种保护方式,使您可以确保工厂不会绕过您的芯片而直接生产芯片。 但是您可以读取配置存储器,对吗? 是的,但是配置内存的存在迫使工厂变得不可靠,而不是一种简单的方式来增加产量,从而与所有其他攻击者一样进行反向工程。

另外,我注意到,上述两种不受不可靠工厂保护的方法都有助于防止未经授权的复制,但它们并不能避免在狭窄的圈子中流行的“书签”。 此外,我将进一步讨论如何自己标记拓扑。

案例2:内存保护

芯片中可编程块和配置存储器的存在是任何数字和模拟现代设计中几乎不可缺少的属性。 随着设计标准的降低,参数在芯片之间的传播增加,而数字调谐是克服该问题的最简单,最可靠的方法。 而且数字电路(例如微控制器)通常直接将数据存储在芯片上,并且可以具有多层存储结构,其中不同部分具有不同级别的访问和保护。 因此,首先使用我们已经必须增加安全性和抗裂性的工具似乎是合乎逻辑的,其次,要仔细考虑要使用哪种类型的内存。

具有金属连接的固件 (掩码ROM)。 通常,看起来好像两条金属线之间存在或不存在接触,这种情况很少出现-就像它们之间是否存在晶体管。 橡树中最多的一种是用于基础矩阵晶体(BMC)中-正如您可能认为的,不仅用于古代国防工业,而且还用于相当现代的解决方案中,例如,至强处理器内部的辅助芯片。 另外,使用这样的存储器,制造了微电路家族(主要是微控制器),因为通过改变一个掩模在工厂中刷新存储器比在板上或盒中生产的每个晶体的通用固件便宜。 Mask ROM可以在显微镜下轻松读取并进行精确蚀刻。 在家里,您可以处理。

图8.假FTDI FT232RL芯片上具有金属互连的ROM固件。 资料来源-zeptobars.com

图8.假FTDI FT232RL芯片上具有金属互连的ROM固件。 资料来源-zeptobars.com

此处还应注意,不仅可以通过金属之间的接触层来闪存,而且还可以通过是否存在金属(易于光学读取),是否存在掺杂(易于光学读取)或例如受掺杂水平控制的晶体管阈值电压(差)来进行闪存存储。光学阅读)。 因此,原则上,如果您真的想隐藏其内容,则掩码ROM不会丢失所有内容。

烧尽的跳线上的内存 (保险丝ROM)。 它允许进行一次记录(包括用户在完成的设备上的记录)和无限次的读数,它的制造和编程非常简单,因此适用于各种配置存储器和固件。

图9.熔丝ROM的两种状态。 资料来源-semiengineering.com

图9.熔丝ROM的两种状态。 资料来源-semiengineering.com如您所见,普通的可熔跳线(Fuse)的状态在显微镜下非常容易看到,也就是说,根本无法保护自己免于用它打开晶体。 好了,除了其他所有功能之外,经典的烧断跳线还非常大(几平方微米),因此不适合大量内存使用。

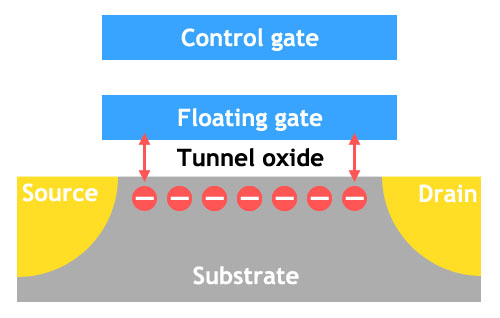

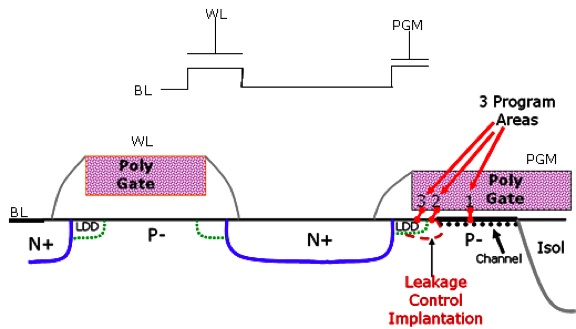

闪存以及基于浮栅晶体管的

其他EPROM和EEPROM选项 。

图10. Flash记录方案。 资料来源-techreport.com

图10. Flash记录方案。 资料来源-techreport.com这种存储器的工作原理非常简单:“浮置”栅极位于电介质的厚层中。 可以通过隧穿向其施加高电压,从而在此快门中放置电荷。 然后,如果不施加高电压,电荷可以在“浮动”快门中存储很长时间。

那么安全性呢?

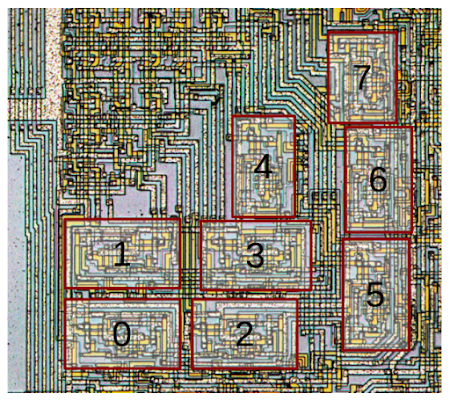

好消息是,用显微镜无法看到EEPROM的状态。不好吗一次有几个。第一个坏消息是EEPROM不仅被高压擦除,而且还由于暴露于紫外线辐射而被擦除(旧计时器可能还记得石英玻璃芯片)。同时,如果您用显微镜仔细查看拓扑,则很可能可以用不透明的材料覆盖整个内存,除了包括读取保护和曝光后的芯片在内的那几个位。道德:在项目中使用EEPROM时,请在其顶部覆盖金属。而且,不仅希望有一个坚固的辐射屏蔽层,而且还要有一些有效的线条,以使屏蔽层不能被精确地蚀刻。但是,这里也隐藏了伏击(这也是第二个坏消息),因为原则上可以从下面突出显示微电路或其各个部分。这并不容易,因为很可能需要从外壳中取出芯片,并且例如,蚀刻衬底的底部,但是可能的。这种技术在测试单芯片微电路方面很受欢迎,因为金属化对于紫外线和激光都不透明,而硅基板几乎是透明的,问题是如果需要局部曝光,如何正确地聚焦辐射束。作为替代选项,您可以配置保护的开/关位,以使其擦除打开保护而不关闭保护。第三个坏消息是,有些传感器可以在擦除操作后读取浮栅或其残余中的电荷。此外,为了电读取存储器,通常不需要向芯片供电,也就是说,不存在开启内置信息破坏机制的风险。姆兰尽管相对较少,但是也值得我们关注。像闪光灯一样,不能从光学角度考虑它。当然,不能用紫外线擦除MRAM,但是存在具有足够高分辨率的磁场传感器,可以使上部金属凹陷,并一点一点地读取存储器。好消息吗潜在的攻击者不太可能迅速而廉价地找到它们。通常,从安全性的角度来看,MRAM是闪存的很好的替代品,但到目前为止,它还没有广泛使用,只是以无晶圆厂公司可用的技术进入了批量生产。如今,反熔丝ROM被认为是受逆向工程保护最多的存储器。。顾名思义,它代表了已烧制跳线的一定对立面,即在未编程状态下具有高电阻,而在已编程状态下具有低电阻。如何实现的?随着栅极的击穿,晶体管的电介质具有高压。击穿区域是如此之小,以至于在显微镜上方或FIB的截面上都不可见,但它也提供了良好且可靠的电阻变化数个数量级,这足以以常规方式可靠地读取存储状态。然而,可以通过直接连接到存储晶体管的栅极和源极来读取这种存储单元。连续的电池的行为就像电容器,缝合的电池的行为就像电阻。 图11.反熔丝存储器的单元部分。显示了晶体管可能击穿的几个区域。这会使阅读方案复杂化。当然,除了对单元格进行目视检查外,还有其他方法可以找到存储器的内容。最简单的方法是使用FIB直接连接到相应的读取线,并将需要发送的任何控制信号发送给它们,以读取正常方式下无法访问的信息。以前,您可以通过物理断开通向内存相应位的线来禁用读取保护。如何保护自己呢?正确设计了芯片的拓扑,并可能已经在其中集成了一些其他功能。这是赛普拉斯如何执行此操作的示例:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.通常这样做是这样的:存储器从上方被一排接地线和电源线覆盖,所有信号线严格位于其下方。在这种情况下,必须注意确保电源线彼此不重复(也就是说,当切断其中的任何一条时,微电路的一部分停止工作),另一方面,以确保它们各自为大量的存储位服务,并且在电源线中插入电流表无法让我们通过读取模式下的消耗来估计存储器的状态(这在大多数类型的存储器中因不同的逻辑状态而异)。通过这样组织芯片的上层,攻击者将很难打开金属化层的一部分以连接到他需要的位置。即使在焊盘和电源的网格中,也要布置额外的保护线,以便在为芯片供电时断开它们(或它们与电源或接地的短路),就可以完全擦除受保护的存储器的内容(或者,如上文所述,物理损坏)芯片)。这样的保护线位于陆地和电力线旁边,极大地使攻击者的工作复杂化,因为按照当前技术流程的标准,FIB的操作需要有形的位置。此外,由于显微镜形成的切口呈圆锥形,因此要连接的层越低,需要清洁的区域就越大。但是实际上,攻击者常常不需要内存内容的确切值,将排序的选项数量减少几个数量级可能就足够了。例如,如果一个存储单元在读取逻辑单元X时消耗了一个逻辑零,而在读取逻辑零100 * X时消耗了,那么当读取一个这样的存储器的字节时,根据存储的内容,我们将得到不同的消耗:0-800 * X1,2,4, ...,64,128-701 * X 3,6,7,...,160,192-602 * X....255-8 * X总共,如果我们不触摸内存,则需要256次尝试来选择其中包含的密码。而且,如果我们知道读取模式下的消耗为701 * X,则只有8个。方便,不是吗?解决此问题的最简单方法是将数据以值的形式存储,并将其取反到相邻单元格中。那么在读取模式下消耗的任何数量的内存将不取决于存储的信息。是的,它需要两倍的内存,但是安全性对我们很重要,对吗?

图11.反熔丝存储器的单元部分。显示了晶体管可能击穿的几个区域。这会使阅读方案复杂化。当然,除了对单元格进行目视检查外,还有其他方法可以找到存储器的内容。最简单的方法是使用FIB直接连接到相应的读取线,并将需要发送的任何控制信号发送给它们,以读取正常方式下无法访问的信息。以前,您可以通过物理断开通向内存相应位的线来禁用读取保护。如何保护自己呢?正确设计了芯片的拓扑,并可能已经在其中集成了一些其他功能。这是赛普拉斯如何执行此操作的示例:It is possible to configure the nvSRAM to provide password protected access. In this configuration, instead of performing the normal power up recall sequence on power up, the part waits for the user to enter a 5-byte password followed by an End Password Entry soft sequence. The End Password Entry soft sequence is a specific seven-address read sequence. If you enter the correct password, the part completes the boot up sequence and is ready for the normal nvSRAM operations. If you enter the incorrect password three times or you do not enter the right password within a specified period of time, the part locks up or fills the SRAM memory with random data, as the application requirement may be. The part can be configured to additionally destroy the functionality and cause physical damage to the chip.通常这样做是这样的:存储器从上方被一排接地线和电源线覆盖,所有信号线严格位于其下方。在这种情况下,必须注意确保电源线彼此不重复(也就是说,当切断其中的任何一条时,微电路的一部分停止工作),另一方面,以确保它们各自为大量的存储位服务,并且在电源线中插入电流表无法让我们通过读取模式下的消耗来估计存储器的状态(这在大多数类型的存储器中因不同的逻辑状态而异)。通过这样组织芯片的上层,攻击者将很难打开金属化层的一部分以连接到他需要的位置。即使在焊盘和电源的网格中,也要布置额外的保护线,以便在为芯片供电时断开它们(或它们与电源或接地的短路),就可以完全擦除受保护的存储器的内容(或者,如上文所述,物理损坏)芯片)。这样的保护线位于陆地和电力线旁边,极大地使攻击者的工作复杂化,因为按照当前技术流程的标准,FIB的操作需要有形的位置。此外,由于显微镜形成的切口呈圆锥形,因此要连接的层越低,需要清洁的区域就越大。但是实际上,攻击者常常不需要内存内容的确切值,将排序的选项数量减少几个数量级可能就足够了。例如,如果一个存储单元在读取逻辑单元X时消耗了一个逻辑零,而在读取逻辑零100 * X时消耗了,那么当读取一个这样的存储器的字节时,根据存储的内容,我们将得到不同的消耗:0-800 * X1,2,4, ...,64,128-701 * X 3,6,7,...,160,192-602 * X....255-8 * X总共,如果我们不触摸内存,则需要256次尝试来选择其中包含的密码。而且,如果我们知道读取模式下的消耗为701 * X,则只有8个。方便,不是吗?解决此问题的最简单方法是将数据以值的形式存储,并将其取反到相邻单元格中。那么在读取模式下消耗的任何数量的内存将不取决于存储的信息。是的,它需要两倍的内存,但是安全性对我们很重要,对吗?案例3:无记忆

但是,如果您的芯片不包含配置内存或仅包含一些没有隐藏意义的位,该怎么办。 怎么了 因此,它便宜得多(不是通过减少用于光刻的掩模的成本,而是通过简化封装和测试的过程来降低成本),对于大多数简单的芯片来说,价格是一个重要的竞争优势。

说到测试。 拒绝晶片上的晶体和闪存配置存储器的过程通常是外包的,特别是对于小公司而言,这是因为合适的设备通常对于初创企业来说是负担不起的,因此必须确保质量。 因此,如果第三方生产是最新的测试方法,并且具有配置内存固件,那么最好完全信任这些人。 或具有不受配置存储器限制的其他防止逆向工程的方法。

那么,如果配置内存不是保护的选项,或者配置内存不足,该怎么办?

光学显微镜和SEM的主要缺点是很难区分硅的掺杂类型。 也就是说,可以看到合金的存在,但是看不到合金的类型。 因此,在分析拓扑和电路提取时,会从上下文中还原掺杂的类型以及电路的隐含逻辑(n沟道晶体管接地,p沟道晶体管电源等)。 绘制了微电路的拓扑,使其与最直观的最可能的选项不重合之后,您可以很好地破坏逆向工程师的血液。 特别是如果您使用伪装成相同的几种不同方案。 有了一些技巧,您不仅可以使电路分析复杂化,还可以使设备(或者至少是模型化的,但如果生产出来的话更有趣)使用恢复的拓扑来做特定的事情,从短路接地到向所有输出发出淫秽的文字。 顺便说一句,错误地盗窃设计的确定性行为不仅可以将示波器烧成海盗,而且还可以使沮丧的用户在以后找您时,可以清楚地向他们证明他们购买了假的。

图12.用显微镜无法区分的三个结构的截面。 左边的是pMOSFET,中间的是短路,右边的是反向偏置二极管(间隙)。

图12.用显微镜无法区分的三个结构的截面。 左边的是pMOSFET,中间的是短路,右边的是反向偏置二极管(间隙)。 图13.用显微镜无法区分的三个数字图书馆单元的拓扑。 左边的是逆变器,中间的是输入和输出的直接连接,右边的是输出的逻辑单元。

图13.用显微镜无法区分的三个数字图书馆单元的拓扑。 左边的是逆变器,中间的是输入和输出的直接连接,右边的是输出的逻辑单元。上图中的每个单元看起来几乎都像最普通的逆变器,但实际上它可以是逻辑零或逻辑单元的逆变器,转发器或生成器。 只有我们用于从输入和输出扩散的触点发出我们的“反相器”。 但是,如果放弃它们,我们将无法与标准电路完全区别开来,只是无法实现输入和输出连接(但是我们可以为此使用两个逆变器)。 但是,由于能够使用同一单元来对信号进行反相或不反相的功能,与攻击者的战斗就更加有趣了,因为没有什么复杂的方法可以处理诸如时钟或开/关电路中的额外反相器之类的陌生设计问题。

尽管没有,但它确实发生了。 构造良好的手形拓扑通常很容易阅读。 肯·席里夫(Ken Schirriff)已经提到的博客就是一个很好的

例子 。

图14. Intel 8008芯片的算术逻辑单元(ALU),显示了单独的数字。

图14. Intel 8008芯片的算术逻辑单元(ALU),显示了单独的数字。在ALU Intel 8008的拓扑上,八个完全相同的电路完全可见-按位数。 了解这是ALU,您可以轻松地还原拓扑方案。 如果其中某些元素为假,这会使您的工作有些复杂,但仅此而已。 所有这些都是因为拓扑非常适合组成部分之间接口的基本概念。 为了使攻击者大为困惑,以至于他放弃进行逆向工程的尝试,必须使拓扑结构不可预测且不可重复。 最简单的方法不是手动制作任何块,而是使用CAD生成芯片的整个网表。 尽管在创建拓扑方面(与人工相比)节省了大量时间,但自动跟踪器仍可以出色地完成元素的直观排列并在完全疯狂的位置进行创建。 而且设计越大,其拓扑就整体上就越综合,逆向工程就越困难。

但这是最简单的方法。 还有更多有趣的选项。 例如,在实现任意逻辑功能的同时,将一组变色龙细胞用作一组逻辑零和一个用于多路复用器输入的发生器。 实际上,这就是FPGA,LUT(查找表)的元素的排列方式。

图15.三输入LUT的实现。 来源

图15.三输入LUT的实现。 来源通过将几个这样的LUT放置在电路的不同位置,并将一些信号传递到“内存单元”的输入,我们将立即解决几个问题:

- 如果我们的策略仍未解决,那么我们将能够设置反向工程电路的行为。 选项-任何,仅受您的想象力限制。

- 使用来自其他模块的任意信号作为生成逻辑零和1的单元的“输入”,会使设计在视觉上分离为模块的过程变得复杂。

- 即使逆向工程师意识到我们正在使用这种受保护的LUT,他也将不得不根据拓扑对许多选项进行分类以恢复电路的功能,从而即使相对较少的受保护单元也可以使逆向工程不必要地耗时。 我最喜欢的是在这样的LUT上组装一个状态机,以控制微电路从一种工作模式转换到另一种工作模式。

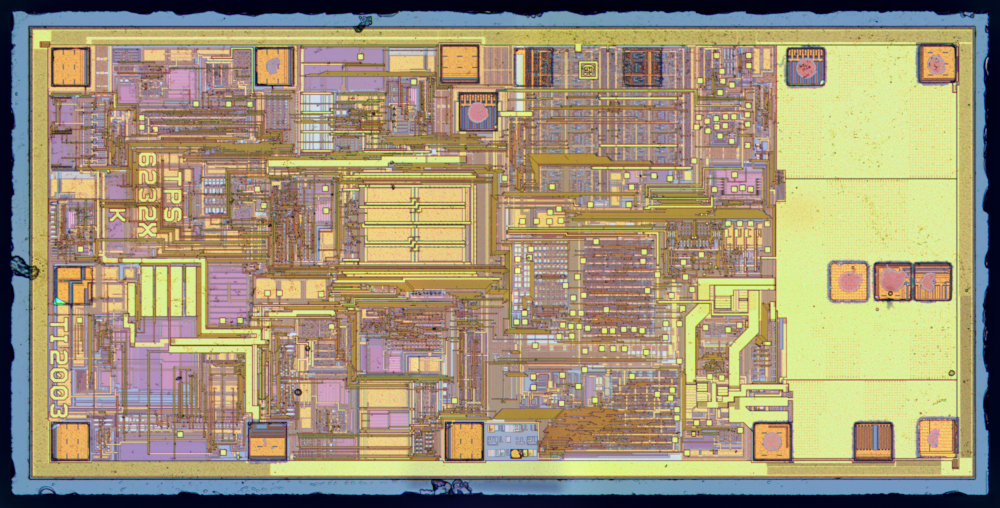

测试图

优秀的工程师非常喜欢全面测试他们的芯片。 “全面”是指-与下图中的TI DC / DC转换器大致相同。 在将板切割成单独的晶体之前,可以连接数十个小的接触垫,以检查所有必要的参数,重要内部线路的状态,确定芯片是否合适,并在必要时找出问题的原因。

图16.德州仪器TPS 62321拓扑图来源-zeptobars.com

图16.德州仪器TPS 62321拓扑图来源-zeptobars.com良好的测试垫覆盖范围对于测试发射和原型尤为重要,但对于批量生产,通常将它们关闭(通过校正一两个面具或可燃跳线),以最大程度地减少对产品性能的影响。 那么,我在说什么呢? 测试接触垫对攻击者有很大帮助,因为您不仅可以自己指出设计中的要点,还可以方便地访问它们。 燃尽的跳线很容易在FIB上恢复,瞧! 理想情况下,安全性要求从串行芯片上完全去除测试垫。 如果此选项不合理(例如,您还需要在批量生产中在板上进行测试),则至少要确保断开测试站点断开的机制是不可恢复的,例如,该机制位于平台正下方并被拉开,以便留出空隙无法方便地连接。

我什至不想开始讨论所有现代数字设计都具有内置的JTAG进行测试这一事实,它使您可以直接查看芯片上任何触发器的状态。 测试的适用性是任何设计的关键特征之一,正是这一事实使得在芯片离开制造商的墙壁之前安全,永久禁用所有测试接口变得极为重要。

优秀的工程师仍然喜欢将测试电路放置在芯片的外围,以进行下一次修订。 通常,这些都是非常重要的方案,否则为什么要浪费时间和精力来组织测试? “构成您的知识产权并对芯片功能至关重要的重要电路?” 仔细地与整个设计分开放置? 非常感谢您!” -逆向工程师会告诉您这样的皇家礼物。 如果您不希望测试者帮助攻击者研究和复制您的设计,请确保它们不会进入批量生产的晶体中或在将平板切割成晶体的过程中经过测试后被销毁。

小习惯

为了再次证明它是如何工作的,在Sergei Skorobogatov的论文中描述

了打开PIC12C508A单片机的

示例,该论文于2004年在剑桥保卫。 翻译简短而免费:

有必要打开外壳并在芯片上找到被紫外线辐射擦除的保护性存储器。 通过查看去往芯片编程引脚的线,可以很容易地做到这一点。 然后,用不透明的紫外线材料覆盖主存储器,并在暴露五到十分钟后,可以将其视为常规编程器。 另一种选择-找到复制保护内存后,只需切断通向它的金属路径,由于某种原因,该路径在该芯片上与其他线路相距太远-如此之远,您不仅可以用FIB进行切割,还可以用针进行切割。 图17.这是非常不幸的一行。 确实,它位于空白处,没有任何保护,可以对其进行切割。

图17.这是非常不幸的一行。 确实,它位于空白处,没有任何保护,可以对其进行切割。结论

当然,不可能掌握它的庞大性,因为微电路的技术和逆向工程以及针对它的保护措施并没有停滞不前,而且一直在不断改进。 信息安全性主题是物联网设计中的关键之一,因此开发人员对此非常关注,并且逆向工程师不能期望像十五或二十年前那么容易提取。 尽管如此,人们应该永远记住,一个保护不佳的系统意味着潜在的损失,巨大的损失,甚至是人员的生命,并且在所有操作级别上,防止未经授权的访问和逆向工程的保护都应该是系统的一部分,而不是排除硬件。