PADS Professional / Xpedition中的约束管理器系统为用户提供了对影响高速信号完整性的所有参数的完全控制。 今天,我们将分析如何在导体总长度的计算中包括微电路引脚的长度和延迟(引脚封装长度和延迟)的影响以及过孔系数的影响。

所有最有趣的事情都在削减。

在本文中,我将尝试回答以下问题:

- 软件长度因子

- 我可以同时在Constraint Manager中为引脚引入长度和延迟限制吗?

- CES中“部件”选项卡上引脚的延迟和长度有何影响?

- 使用输出长度参数和软件长度因子时,“调音表”工具如何工作?

- 软件中的延迟对计算总信号延迟的影响

在约束管理器中配置引脚延迟

在PADS Professional / Xpedition VX2.2及更高版本中,已经出现了将具有延迟和输出长度的文件同时直接导入限制输入系统的功能。

为了导入,请打开CES,请转到“

文件”>“导入”>“包延迟”,然后选择有延迟的文件:

PinPkgDelays / PinPkgLengths文件的格式(* .txt /.* ppd / *。Ppl)如下:

其中,

单位是值的格式(不取决于大小写):

- 延迟,秒(s),毫秒(ms),微秒(us),纳秒(ns)和皮秒(ps)

- 长度-千分之一英寸(th),微米(um),毫米(mm),英寸(in)

part_name是唯一标识您的芯片的关键字

pin_number,值 -此处显示引脚号和相应的长度/延迟

值重要说明 :即使您在CES中将逗号定义为分隔符,导入工具也不支持逗号格式。

PinPkgDelays.txt文件的一个小示例:

自动计算延迟值

如果仅了解有关芯片引脚长度的信息,则可以使用CES根据CES设置

(设置>设置)中定义的信号传播延迟自动计算引脚延迟值:

设置输出长度的值后,右键单击与触点延迟相对应的单元格,然后选择“

计算延迟” ,系统将自动计算该值:

以下是

通孔长度,通孔延迟和引脚封装长度的各种使用案例的示例

。示例1

在此示例中,

不使用“过孔”或“引脚封装长度”参数:

在组件U1的每个引脚上增加长度的100th可获得以下值:

现在,Tuning Meter会显示导体的长度,并考虑到组件的每个引脚增加的第100个:

示例2

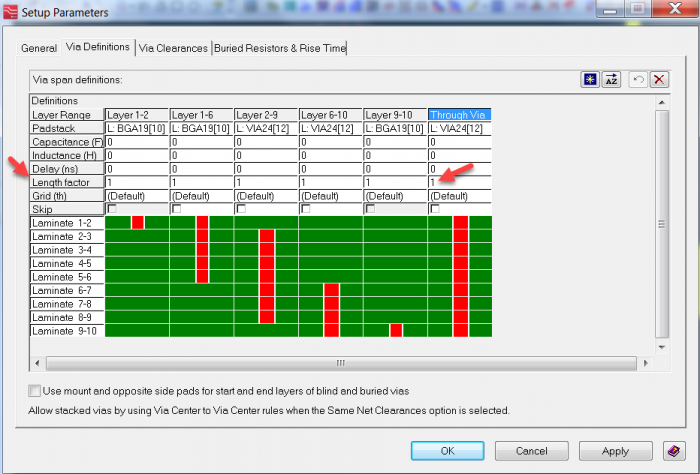

现在转到“设置”>“设置参数”,然后在“通孔定义”选项卡上将“通孔

长度系数”设置为

1 。

注意:软件长度值是根据您的电路板堆栈计算得出的。 另外请注意,在计算软件长度时, 不考虑初始层和最终层的铜厚度。 下图显示了如何计算软件信号的长度,从第1层到第3层,从第3层到第8层:

注意:软件长度值是根据您的电路板堆栈计算得出的。 另外请注意,在计算软件长度时, 不考虑初始层和最终层的铜厚度。 下图显示了如何计算软件信号的长度,从第1层到第3层,从第3层到第8层:

设置软件长度因子后,限制管理器中导体的实际长度将发生变化:

现在,调谐器中显示的导体长度包括软件长度的系数和结论的长度:

示例3

此时,我们将添加0.02 ns的

引脚封装延迟 :

让我们看一下在

TOF模式下为导体计算的延迟值,前提是引脚封装延迟设置为

0 :

现在将

引脚封装延迟设置为0.02 ns:

限制管理器中针对该信号的延迟已更改为0.02,我们可以验证以下内容:

示例4

现在让我们看一下同时安装引脚封装延迟和引脚封装长度以及通孔延迟和通孔长度因数的情况,以及这将如何影响导体总长度/延迟的计算。

下图显示了调谐计工具中零引脚封装延迟和过孔延迟为零时导体中的传播延迟:

下一步是将引脚封装延迟设置为0.02 ns并观察更改:

现在,如果我们在“引脚封装长度”或“通过长度因数”字段中设置另一个值,则延迟值将不会发生任何变化,因为我们使用的是

TOF模式。

但是,如果将引脚封装延迟和通孔延迟设置为0.02 ns,则会得到以下结果:

在限制编辑器中,将“引脚封装延迟”和“通孔延迟”参数设置为0.02 ns时,信号沿导体的传播延迟如下所示:

可以通过“通孔定义”选项卡上的“

设置”>“设置参数”菜单来配置“通孔延迟”和“通孔长度因数”:

结论

PADS Professional / Xpedition约束输入系统允许您指定输出长度和延迟值,

但是,如果您有CES选项来计算信号传播时间(

TOF ),则系统将使用

引脚封装延迟单元中的值,并且如果计算选项基于

长度 -系统将从“

引脚封装长度”单元中获取值。

软件的影响也是如此。 如果在限制管理器中定义的延迟类型设置为

Length ,则将使用软件的

Via Length Factor ;对于

TOF而言 ,将使用

Via Delay值。

我希望它不会显得太大而混乱。

我准备在评论中讨论所有难以理解的时刻。

Filipov Bogdan

PBO ,PADS解决方案产品经理