业界一直使用PCIe 3.0总线已有七年之久,尽管对台式计算机的首个PCIe 4.0支持很快就会出现在AMD第三代Ryzen芯片中,并且第一批PCIe 4.0 SSD

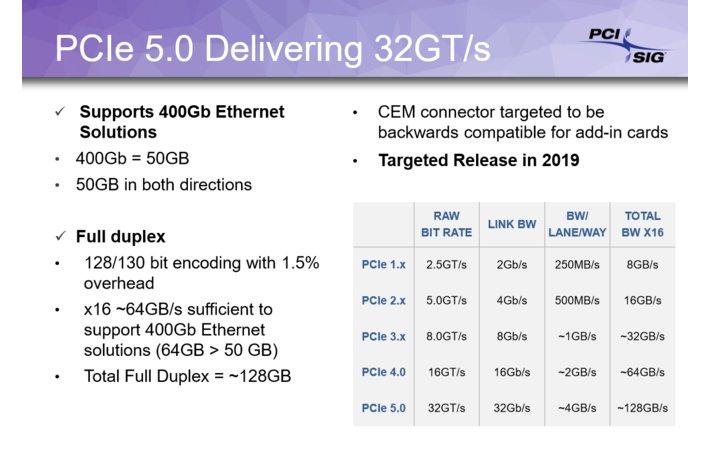

也已经出现 ,但制造商已经在为PCIe 5.0做准备。 与PCIe 4.0相比,新标准将吞吐量提高了一倍,后者的

传输速度为

每秒 32 GT / s [

事务 ]。

今天,定义PCIe标准的组织PCI-SIG已宣布采用PCI Express 5.0总线的规范版本0.9,这意味着最终设备将在不久的将来出现在市场上。 (公司开始开发规范版本为0.4的成品设备,并且随着版本0.9的出现,许多公司已经在推出其产品)。

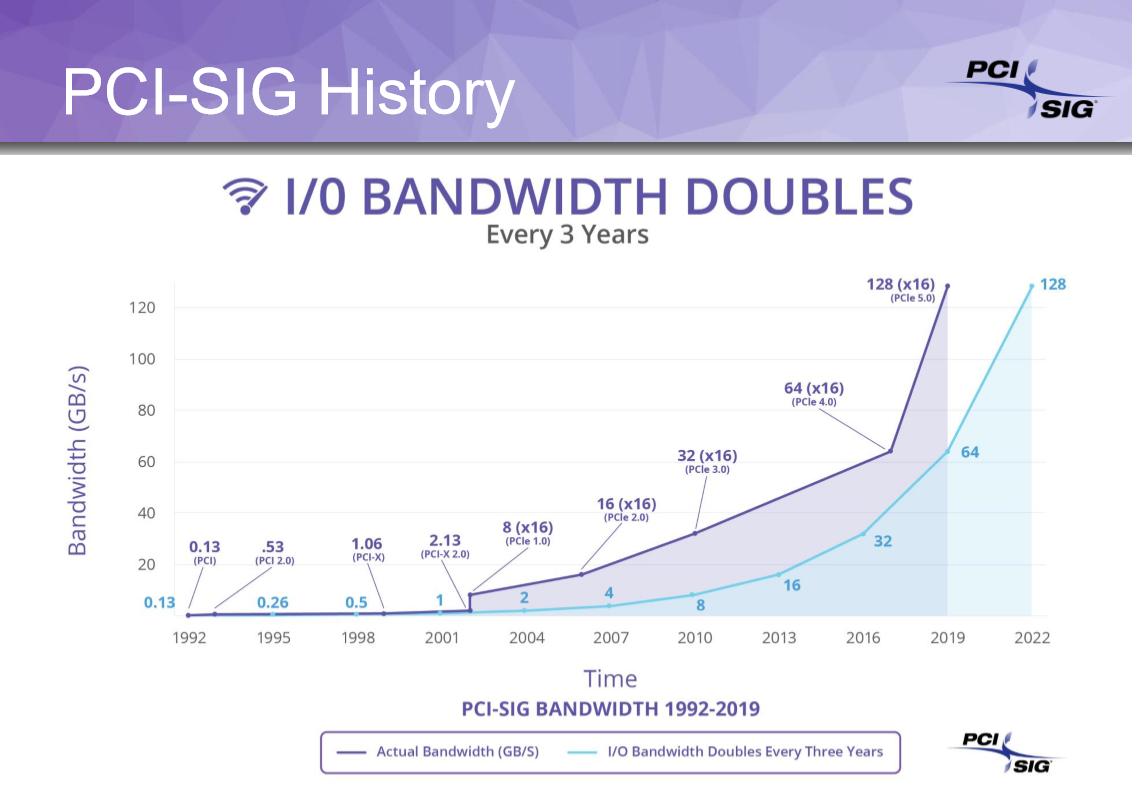

PCIe随处可见,并成为计算技术的有形部分,因为它涉及计算机上几乎所有可用的设备。 因此,它是许多其他技术(例如数据存储,网络技术,GPU,芯片组等)发展的催化剂。

不幸的是,相对于通常每两年发布一次的PCI-SIG节奏,PCIe 4.0标准明显落后。 PCIe 3.0于2010年获得批准,与PCIe 4.0的出现之间存在七年的差距。 鉴于PCIe 5.0标准的迅速兴起,可以很容易地假设它不会长期存在,特别是考虑到制造商已经开始使用新的PCIe 5.0物理层协议开发设备。

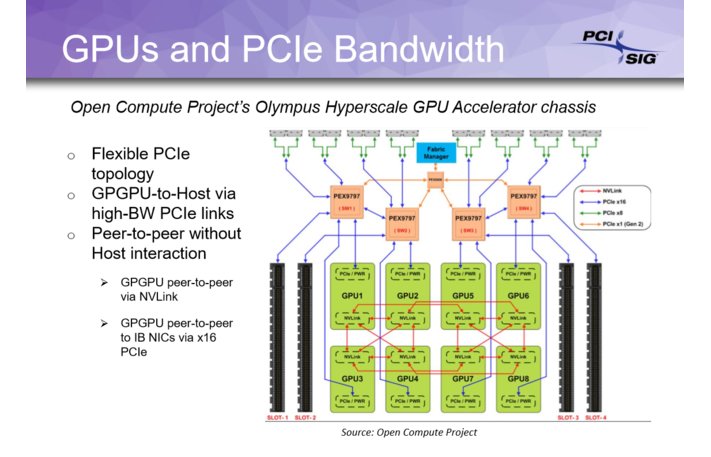

PCI-SIG预计这两个标准将在一段时间内并行存在,PCIe 5.0将用于需要最大带宽的最快设备中,例如,与用于AI和网络技术的计算GPU配合使用。 这意味着许多支持PCIe 5.0的高级设备将出现在数据中心,网络环境和高性能计算中。 要求较低的应用程序(例如家用PC)将满足PCIe 4.0接口的要求。

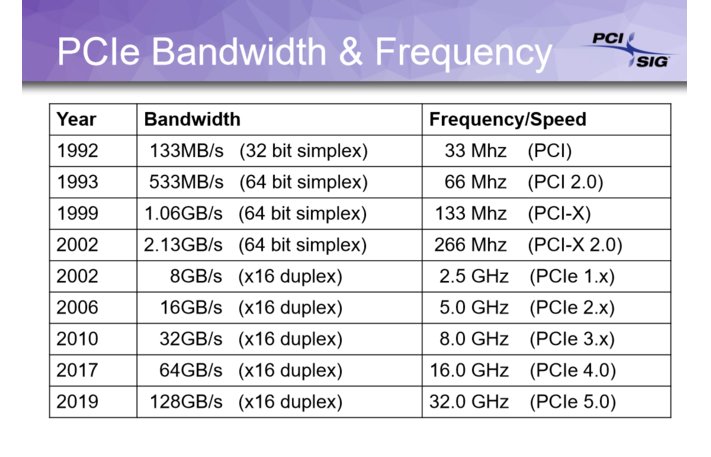

带宽和PCIe频率

带宽和PCIe频率 以太网演进

以太网演进 GPU和PCIe带宽

GPU和PCIe带宽 PCIe 5.0将产生32 GT / s

PCIe 5.0将产生32 GT / sPCIe 4.0可以提供64 Gb / s的吞吐量,而PCIe 5.0可以将其加倍至128 Gb / s。 两种版本都将使用PCIe 3.0标准中引入的128b / 130b编码方案。 PCI-SIG代表表示,使用128b / 130b编码时将开销减少20%感到非常满意,并且进一步的编码改进将带来1.5%的微不足道的收益。

其他功能将出现在PCIe 5.0中,例如,为改善信号纯度而进行的电子技术更改,扩展卡的向后兼容CEM连接器以及与以前版本的PCIe的向后兼容性。 PCI-SIG还开发了一个新标准,该标准可以减少延迟并在防止信号丢失方面更加强大。

PCI-SIG定义了规范,但不能完全控制成品设备何时在市场上出现。 PCI-SIG正在等待2019年第一季度的最终规范版本1.0的批准,并在今年发布首批支持PCIe 5.0的设备。 到2020年,他们的患病率预计会上升。