我们将继续考虑基于赛普拉斯专有文档的UDB,即与Datapath相关的有用琐事。

循环的一般内容是“ UDB。 这是什么?

第1部分。简介。 请第2部分。数据路径。第3部分。数据路径FIFO。第4部分。数据路径ALU。第5部分。数据路径。 有用的小东西。 (当前文章)

第6部分。管理和状态模块。第7部分。时序和复位控制模块第8部分。处理UDB21.3.2.6 CRC / PRS支持

数据路径支持循环冗余校验(CRC)和伪随机序列(伪随机序列,PRS)的生成。 在数据路径块之间跟踪链接的信号,以支持长度超过8位的CRC / PRS。

选择最高CRC / PRS块的最高有效位(英语最高有效位,MSB)的编号,并将其跟踪(并与其他块链接成链)到较低的块。 之后,将具有输入数据(SI数据)的XOR操作应用于MSB,从而提供反馈信号(反馈,FB)。 之后,将反馈信号跟踪(并与其他模块成链状连接)到较低的模块。 该反馈值用于所有模块,以对当前电池值执行多项式的

异或运算(来自Data0或Data1寄存器)。

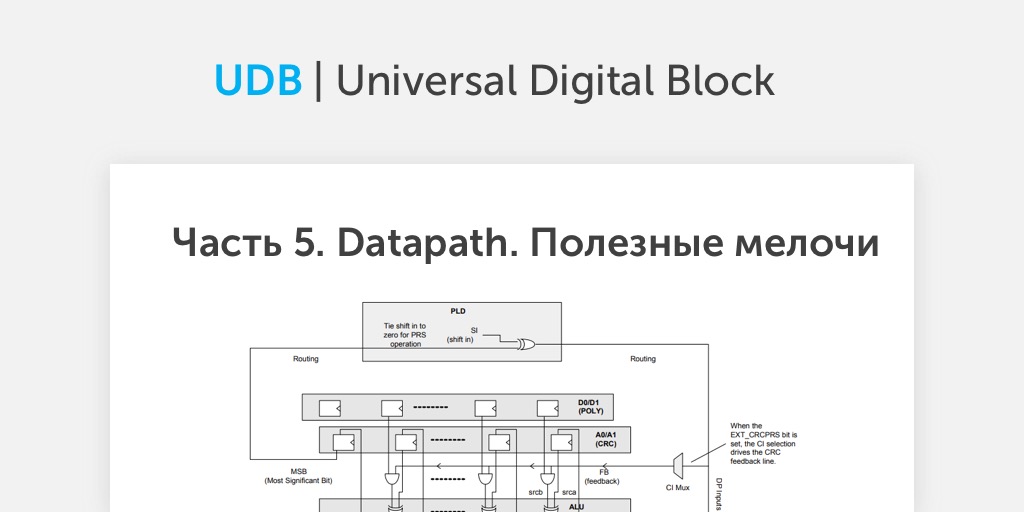

图21-18显示了CRC操作的结构配置。 PRS配置相同,但移位输入数据(SI)被拉为0。在PRS模式下,D0或D1包含多项式值,而A0或A1包含初始值(种子)和计算后获得的CRC值。

译者注意。显然,这句话在专有文档中有一个错字,因为应该在PRS模式下获得一个随机数。 有关CRC的信息位于下面。 图21-18。 CRC的功能结构。

图21-18。 CRC的功能结构。要激活CRC支持,必须将动态配置RAM中的

CFB_EN位置1。这将激活SRCB ALU输入和CRC反馈信号的

AND操作。 如果该位设置为零,则反馈信号将被分配为1,这允许执行正常的算术运算。 在每个周期动态控制该位,使您可以将CRC / PRS操作与其他算术操作交替使用。

链接CRC / PRS

图21-19显示了在三个UDB之间的链中绑定CRC / PRS的示例。 此方案支持在分辨率为17到24位的模式下运行。 链中的控制绑定位是根据数据路径在链中的位置设置的(请参见图)。

图21-19。 CRC / PRS的链绑定。

图21-19。 CRC / PRS的链绑定。CRC / PRS反馈信号(cfbo,cfbi)如何成链连接:

- 如果所选的块最年轻,则此块的反馈信号由内置逻辑生成,该逻辑将移位输入移至右侧(sir)并对其进行最高有效位的XOR操作。 (在PRS的情况下,“ sir”信号设置为“ 0”)。

- 如果所选的块不是低阶块,则必须锁定CHAIN FB配置位,并且从前一个块开始以链状发送反馈。

CRC / PRS MSB信号(cmsbo,cmsbi)链如何:

- 如果所选块为高,则使用MSB_SEL配置位配置MSB配置位(根据所选多项式)。

- 如果所选的块不高,则必须锁定CHAIN MSB配置位,并且将从下一个块沿链发送MSB信号。

多项式规范CRC / PRS

作为要写入相应寄存器D0 / D1的多项式配置的示例,请考虑

CCITT CRC-16多项式,其形式为x

16 + x

12 + x

5 +1。图21-20显示了从多项式提取数据格式的方法。 根据定义,术语X0始终为1,因此无需编写。 对于该多项式的所有其他成员,将单位设置为必要的位置,如图所示。

图21-20。 CCITT CRC16多项式的格式。

图21-20。 CCITT CRC16多项式的格式。请注意,多项式的格式与经典十六进制格式中指定的格式略有不同。 例如,

CCITT多项式

CRC16通常被称为

1021H 。 要将其转换为数据路径所需的格式,您需要右移一个位置,并向MSB位加1。 在这种情况下,要写入D0或D1的正确多项式值为

8810H 。

CRC / PRS配置示例

以下是CRC / PRS配置要求的简要说明,假设D0是多项式,并且在A0中计算CRC / PRS:

- 选择一个合适的多项式(上面的示例),并将其写入D0。

- 选择适当的种子(例如,对于CRC,全为零,对于PRS,为全1),并将其写入A0。

- 如有必要,如上所述配置链接。

- 如上所述,选择一个MSB项目。

- 配置动态RAM RAM字段:

一个 选择D0作为ALU“ SRCB”(ALU B数据源)

b。 选择A0作为ALU“ SRCA”(ALU A数据源)

c。 选择

XOR进行ALU操作

d。 选择

SHIFT LEFT进行SHIFT操作

e。 选择

CFB_EN以启用CRC / PRS支持。

f。 选择ALU作为记录源A0

选择CRC时,您需要为输入数据配置

右移字段,并在每个步骤中在此输入上提交数据。 选择PRS时,必须将

右移设置为0。

UDB的这种配置会生成必要的CRC或生成最高有效位,然后可以将其转发到外部,从而从中删除伪随机序列。

外部模式CRC / PRS

要启用外部CRC或PRS计算,可以指定一个静态配置位(

EXT CRCPRS )。 如图21-21所示,在PLD块中执行CRC反馈计算。 当该位被拉高时,CRC反馈信号直接从输入多路复用器CI(Carry In)发送,绕过内部计算。 该图显示了一个简单的配置,支持高达8位的CRC或PRS。 通常,使用内置电子电路,但是此参数允许您使用时分复用在一个UDB中实现更复杂的配置,例如16位CRC / PRS功能。

图21-21。 外部模式CRC / PRS。

图21-21。 外部模式CRC / PRS。在此模式下,动态配置RAM的

CFB_EN位还控制是否对CRCB ALU输入处的CRC反馈信号使用

AND操作。 因此,与内部CRC / PRS模式一样,该功能可以在必要时与其他功能交替使用。

21.3.2.7数据路径输出和多路复用

条件由电池触发值,ALU输出和FIFO状态产生。 这些条件可以通过数字跟踪通道传输到其他UDB,以形成向DMA或“芯片分支”的中断请求。 下表显示了16种可能的条件。

表21-16。 数据路径条件生成。

数据路径有六个出口。 如图21-22所示,每个输出都有一个16合1多路复用器,使您可以将16个信号中的任何一个路由到任何Datapath输出。

图21-22。 与输出多路复用器的连接。

图21-22。 与输出多路复用器的连接。比较

有两个比较,其中一个具有固定源(

比较0 ),而另一个是动态选择的(

比较1 )。 每个比较都有一个8位静态屏蔽寄存器,允许在指定的位字段中进行比较。 默认情况下,屏蔽处于禁用状态(比较所有位),必须手动激活。

比较1输入是动态配置的。 如下表所示,有四个“比较1”参数适用于较少和相等的条件。

CMP SELA和

CMP SELB配置

位确定可能的比较配置。 动态配置的RAM位在每个周期指定一种配置(A或B)。

表21-17。 比较配置。

比较0和

比较1独立地与前一个数据路径中生成的条件相关联(按处理顺序)。 是否链接比较是在UDB配置寄存器中静态指定的。 图21-23显示了将“等于”链接到比较链,这简化为将

AND运算应用于此块的“等于”比较以及前一个块的输入。

图21-23。 链接到比较链是“相等的”。

图21-23。 链接到比较链是“相等的”。图21-24显示了链接到较少比较链。 在这种情况下,给定块的输出结果(cl0)由“小于”比较电路生成,并且是无条件的。 如果条件等于当前块并且打开了链接模式,则将该信号与来自链的输入结果进行“

或”运算 。

图21-24。 链接少于

图21-24。 链接少于检测全零和全一

每个电池都有一个全零的检测器和一个所有单位的检测器。 这些条件可以按照UDB配置寄存器中的说明进行静态链接。 绑定模式在UDB配置寄存器中设置。 零检测链中的链接是根据与比较“等于”相同的概念发生的。 如果激活了链接,则将

AND操作应用于成功链接的数据。

溢流

溢出定义为MSB中的

XOR传输操作和MSB中的传输。 如

MSB_SEL位所示,使用当前的MSB执行计算。 此条件不能被链接,但是,如果在更高的数据路径上执行总容量功能直到连接块之间的传输,则计算将是正确的。

21.3.2.8并行输入和输出数据路径

如图21-25所示,

并行输入 (PI)和

并行输出 (PO)信号提供了将数据传递和跟踪资源到Datapath以及从其中输出数据的能力有限。 在A0和A1之间选择ALU asrc时,PO信号始终可用于跟踪。

译者注意。这是极其重要的机制,它使UDB不仅可以处理串行数据,还可以处理并行数据。 出于某种原因,本文档没有强调这一点,但是您可以通过传入其中一个应用笔记来了解它。 图21-25。 并行输入/输出数据路径信号。

图21-25。 并行输入/输出数据路径信号。要将数据输入到ALU中,必须选择

Parallel In 。 有两种模式:静态和动态。 在静态模式下,

PI SEL位

将asrc ALU

值转换为PI。

PI DYN位用于提供PI动态模式。 当它被翘起并且还假设

PI SEL为0时,PI多路复用器可以控制动态控制位

CFB_EN 。

CFB_EN位的主要功能是提供PRS / CRC功能。

21.3.2.9链接数据路径

每个数据路径块都有一个8位ALU,用于将连字符,移位,捕获触发器和条件信号链接到最近的相邻数据路径,以创建算术函数和移位具有更高位深度的寄存器。 这些信号以链状连接,是隔离的,使您可以在一个周期内有效地实现16-24位和32位功能,而不会出现加速以及跟踪通道延迟引起的其他问题。 此外,链式手柄支持原子读取链接块中的电池。 如图21-21所示,所有生成的条件信号和捕获信号都从最年轻的块到最老的块连接在一起。 从初级到高级,也执行向左的转换。 从最老到最年轻,向右移动。 用于反馈的CRC / PRS链接信号从高到低路由,而MSB输出从高到低发送。

图21-26。 数据路径线程链。

图21-26。 数据路径线程链。21.3.2.10 RAM动态配置

每个数据路径都包含一个动态配置RAM,该RAM具有8个字,每个字16位(见图21-27)。 这种RAM的目的是基于每个数据路径的选定时钟来控制每个周期的数据路径配置的位。 RAM具有同步的读写端口,用于通过系统总线下载配置。

为了将这些16位字快速输出到Datapath,提供了一个额外的异步读取端口作为控制位。 多路复用器从数据路径输入中选择异步地址输入,该数据可以从任何可能的信号中获取,包括微电路支路,PLD输出,控制单元输出或任何数据路径输出。

异步读取端口的主要目的是在单个周期内提供对数据路径控制位的快速解码。

图21-27。 RAM I / O配置。

图21-27。 RAM I / O配置。下表中显示了动态配置的RAM字的字段以及每个字段的用法说明。

表21-18。 动态配置参考。

(a。-对于CI,SI和CMP字段,RAM字段允许您选择两个预定义选项之一。请参见静态寄存器配置)。

待续...