最近,最近发布了一个免费的在线课程,该课程分为三部分,分别是“智能纳米芯片的创造者如何工作”(

1、2、3 )。 它旨在为学童提供职业指导,其最大特点是:这是微芯片设计团队的工作分配的外观,此处的开发基于寄存器传输级别的此类设计概念,并且这些算法用于确定计算机设计的处理器可以工作多少兆赫兹或汽车电子。

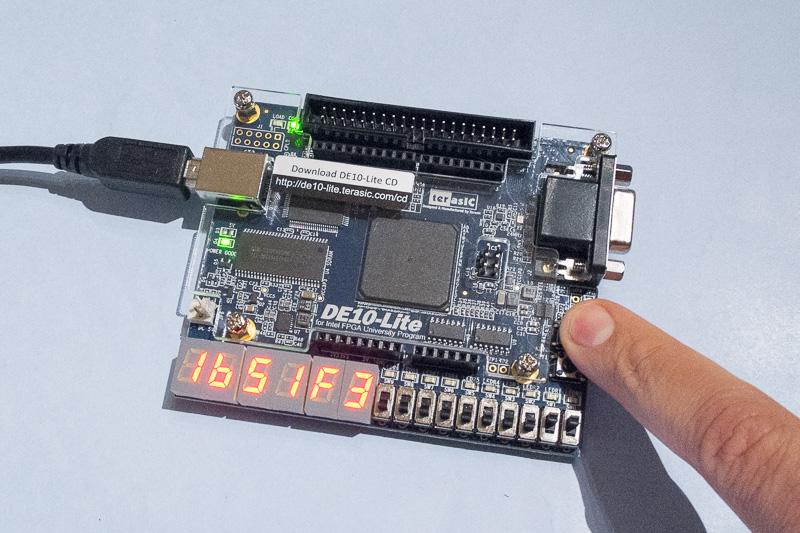

除了理论上的职业指导以外,该课程还可用于选择FPGA和处理器设计方面的实用暑期学校的学生。 这样的学校计划今年在Zelenograd进行,其原型在前一年在新西伯利亚的夏季青年程序员暑期学校以及在基辅的学童电子周中进行了测试。 您还可以尝试在硬件实现的神经网络和游戏的硬件实现上进行黑客马拉松,并输出到VGA显示器(在后面的更多内容中)。

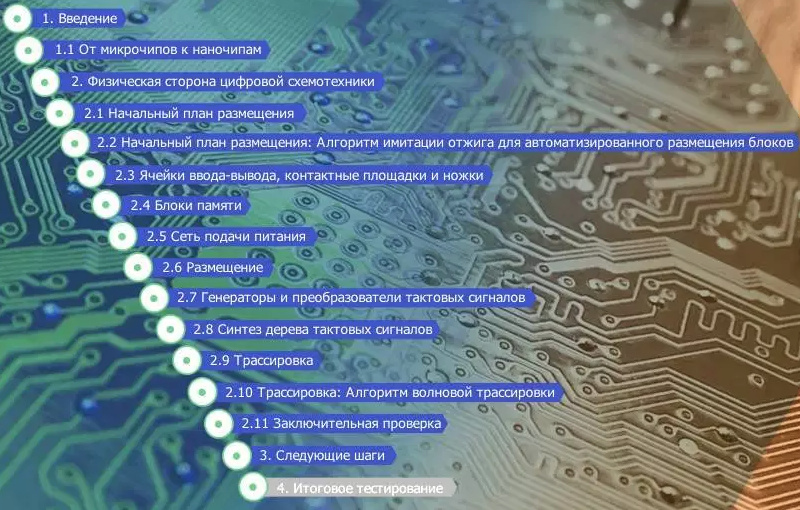

简要介绍三个模块中每个模块的内容-“从晶体管到微电路”,“数字电路的逻辑端”和“数字电路的物理端”。

“智能纳米芯片的创造者如何工作”课程从绝对零开始,因此其第一部分“从晶体管到微电路”在很大程度上重复了过去50年来为学童设计的其他电子材料-什么是晶体管,逻辑元件,二进制数字和触发器。 现代iPhone中的D型触发器的概念与1986年《量子》杂志中的相同。 晶体管减少了千倍,但其本质并未改变。

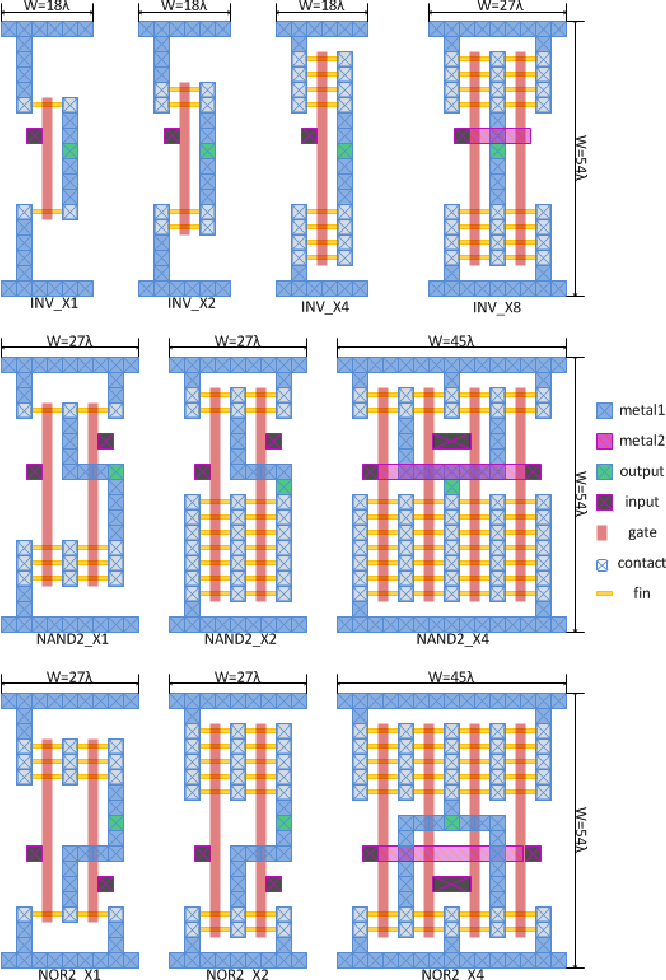

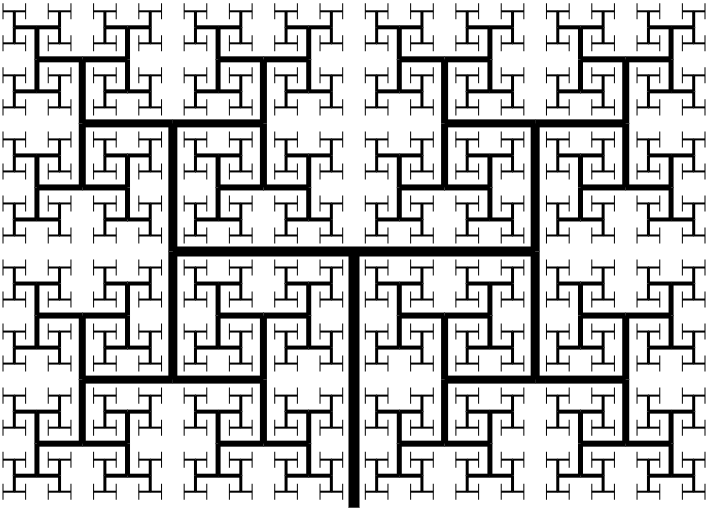

以前的课程中没有的唯一信息块是关于所谓的标准单元的信息,这些标准单元是基于其技术构建的,现代绝大部分的专用微电路都是如此。 他们看起来像这样:

尝试从下面的测试中回答问题,如果知道答案,则可以跳过该课程的第一个模块:

为什么将现代微芯片的标准单元(ASIC标准单元)称为标准?

- 哦,我知道! 这是因为它们实现了标准逻辑功能AND,OR,NOT

- 标准电池中的晶体管元件具有标准的化学成分

- 标准单元以标准时钟速度运行

- 它们具有标准高度(面积尺寸),从而简化了对它们的供电以及它们之间的自动连接

- 标准单元的结构曾经由某个欧洲标准委员会标准化。

正确答案是:

隐藏文字4.标准单元(ASIC标准单元)具有标准高度(面积尺寸),这简化了向它们的供电以及它们之间的自动连接

如果您不知道,则可以学习该课程的第一个模块-“从晶体管到微电路”。 其内容如下:

如果“智能纳米芯片的创造者如何工作”课程的第一部分中的大多数都谈到自1970年代以来在学童中流行的教科书中的相同内容,那么在第二部分“数字电路的逻辑方面”中,我们将进入没有Quantum杂志,而且由于苏联解体,总体上在俄罗斯的教育中被遗弃了。 我们正在谈论所谓的RTL到GDSII路线,这是一种基于硬件描述语言Verilog和VHDL的代码编译/合成来设计数十亿个晶体管和芯片轨道的计划的设计方法。 从高级学生的水平开始,必须克服这方面的失败。 否则,就没有真正的俄罗斯iPhone,机器人或自动驾驶汽车。

近年来,俄罗斯通过综合各种语言的硬件描述,促进了数字电路设计的普及,其中包括由于俄语发行了David Harris和Sarah Harris的免费(电子版)教科书“数字电路和计算机体系结构” 。 哈布雷(Habré)上有关该教科书的帖子获得了超过30万的浏览量,下载量两次使英国的Imagination Technologies网站不堪重负。 最近,发布了该教程的最终修订版,您可以

从MIPS网站的链接中下载该教程。 的确,该链接仅在Windows下有效,但在Mac和Linux下却存在问题。 如果您有任何问题,可以

从此处下载相同版本。 或从臭氧或迷宫中的DMK Press购买纸质书。

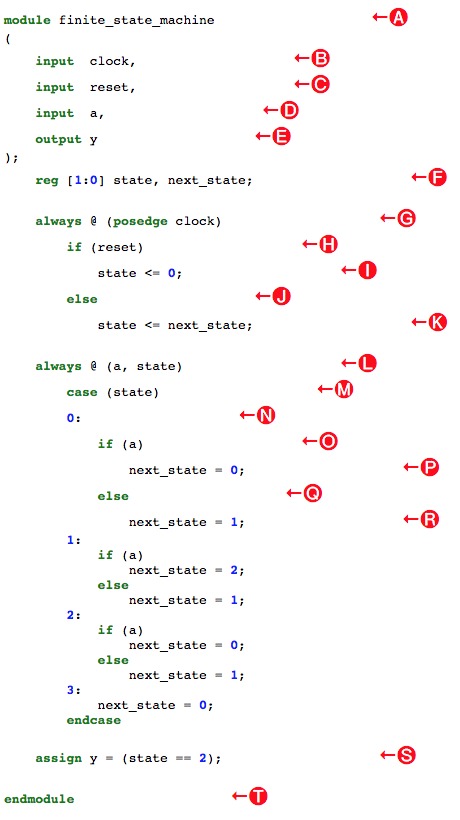

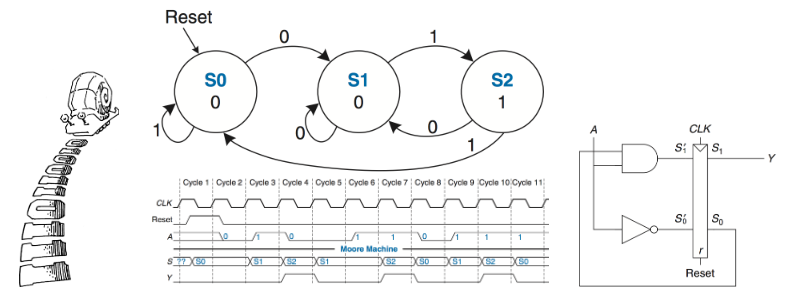

“智能纳米芯片的创造者如何工作”课程的“数字电路的逻辑端”模块以哈里斯(Harris)的“微笑蜗牛”为例。 蜗牛是一种状态机,可识别零和一的序列。 该课程了解Verilog硬件描述语言中“蜗牛”机器的源代码,并介绍状态机状态图和时间信号图的概念。 此后,显示了根据说明合成的电子电路,其中包含逻辑元件和D触发器,用于存储“蜗牛”状态机的状态。

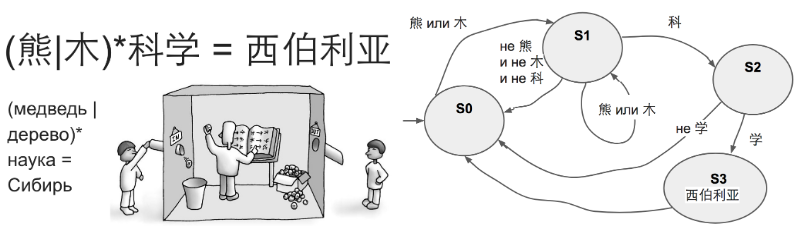

基于“蜗牛”示例,参加黑客马拉松的学童可以为FPGA卡合成各种“代码锁”。 在“智能纳米芯片的创造者如何工作”课程的考试中,存在一个关于所谓“中国房间”的状态机状态图的问题,这是人工智能领域的一个流行例子。 这是一个用于与汉字对话的简单状态机的示意图。 如果您给他几个象形文字“ tree”和“ bear”的组合,再加上以下象形文字“ science”,则机器将发出一系列象形文字“西伯利亚”-这是在新西伯利亚Academgorodok的一个小学生研讨会上诞生的一个例子:

第三部分,“数字电路的物理方面”,描述了如何将在第二部分中合成的逻辑元素图布置在微电路上,并转换成GDSII图,然后将其发送到烘烤微电路的工厂。 本部分还讨论了面向数学的学生感兴趣的布局和跟踪算法。 微电路设计自动化领域的研究是数学竞赛的前获奖者中的一个热门领域。

使用Synopsys IC编译器放置和追踪后,芯片设计如下所示:

但是这种优雅的分形结构是芯片内部时钟信号的树,其构建是为了使时钟信号大约同时到达所有D触发器。 该树的“分支”的宽度在微电路上从厚金属化合物到薄金属化合物不等,以便在半导体技术的纳米级上满足铜导体的物理限制:

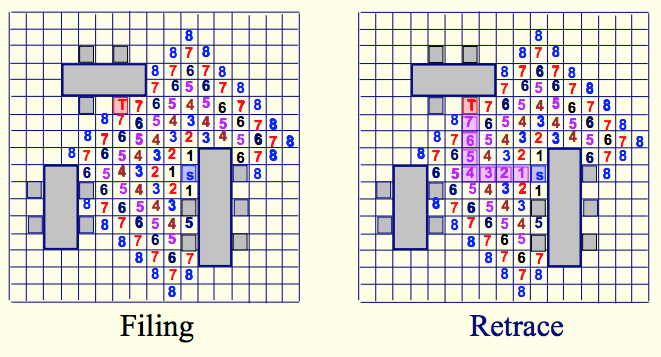

这是所谓的波形跟踪算法的说明(英文为Maze Routing-“在迷宫中搜索路径”)。 该算法在早期的设计自动化程序中用于连接电路的逻辑元素。 波形跟踪算法非常简单,有能力的高中生可以用C,Python或Java编写它。 对于将来打算编写更复杂算法的人(例如,将来的三维芯片),这是一个有用的练习:

学生掌握了Verilog上的数字电路设计概念后可以做什么? 尽管有必要,但是在模拟器中进行练习或在FPGA板上闪烁指示灯是一件很烦人的事情,简单的处理器和神经计算器的设计仅对决定掌握计算机体系结构的一小部分学生感兴趣。 幸运的是,学生可以进行的练习不仅限于这两个领域。

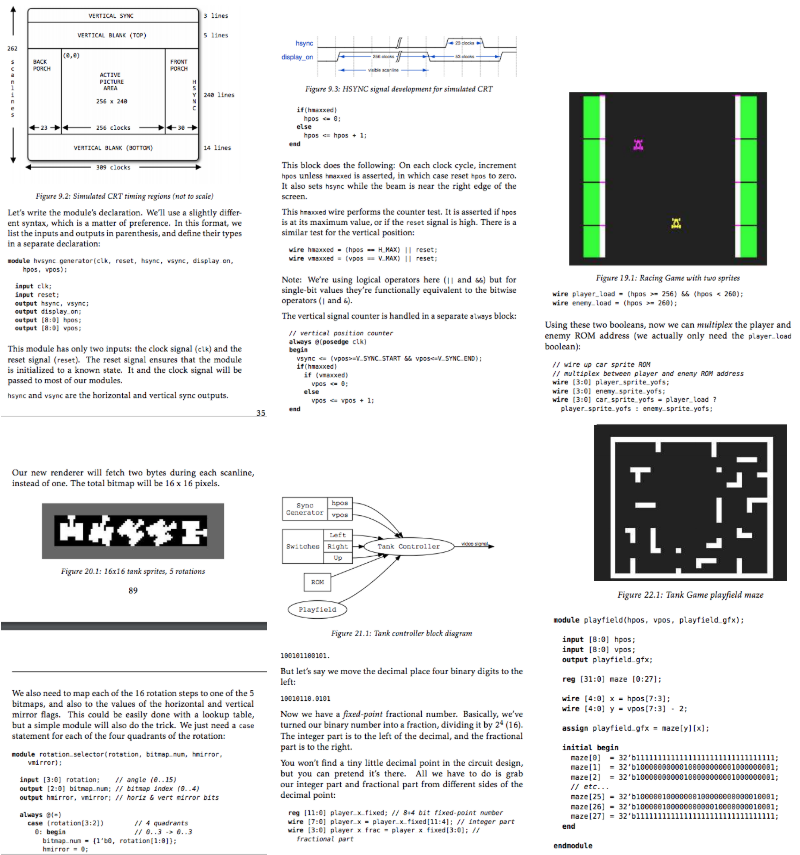

就在两个月前,史蒂文·哈格(Steven Hugg)出版了《在Verilog中设计视频游戏硬件》一书,其中描述了在Verilog上进行游戏方案的设计,并将FPGA的实现与VGA显示器相连。 我们谈论的是1970年代和1980年代的视频游戏,其中包括扫描,帧缓冲区和子画面的生成。 Atari乒乓球,太空战争,tanchiki。 用于这些游戏的老虎机最早是在1970年代组装在集成度很小的微电路上的,然后组装在PAL和微控制器上,包括Apple首次使用的Motorola 6502。 史蒂文·哈格(Steven Hagg)的书还讨论了1980年代下半叶使用德州仪器(TI)TMS9918视频处理器对苏联程序员和游戏玩家熟悉的子画面的硬件实现,该处理器安装在当时进口到苏联学校的日本雅马哈MSX计算机中。

哈格的书不仅有用,而且对怀旧的曲柄也没什么用。 对于开始学习电子产品的现代学生和学童来说,这是一组出色的任务。 由于任务很老,但Verilog,逻辑综合,FPGA原型技术是新技术,与

麻省理工学院 2018-2019学年正在研究的技术相同

(6.111) 。 如果没有使用Verilog和FPGA进行简单的练习,现在坐在Intel,NVidia和AMD的Santa Clara,Apple和其他电子公司的Cupertino的工程师就不会长大。

总结一下。 如果现在有一定数量的学校和大学教师检查“智能纳米芯片的创造者如何工作”课程,然后将感兴趣的学生发送到该课程,那将是很好的。 然后,对于将获得此课程证书的学童,您可以邀请他们参加带有FPGA板的实践研讨会(其中一些将作为成功项目的奖品分发)。 目前正在莫斯科的泽列诺格拉德讨论此类研讨会,索契,明斯克等地也有兴趣。 从长远来看,俄罗斯将发展一个在硅谷,日本,台湾,韩国,英国开发的芯片开发者社区,现在在上海和其他地方正在形成。 这是每个技术先进的大国都应该存在的东西,在俄罗斯,数学,物理学和工程学都有足够的传统来支持这种发展。