在开发

本文描述的REDD复合体的硬件时,我们考虑了各种实现选项。 之所以考虑使用PSoC,是因为它有一个现成的相对标准化的USB-I2C适配器版本,尽管事实上。 不幸的是,由于

有关DMA的

文章中所述的原因,不可能对PSoC上的这种特殊复合体做一些困难的事情,并且简单在经济上不可行。 事实证明,从FTDI购买芯片更便宜。 但是,在使用PSOC进行实验的同时,有趣的细节被揭示出发布是有意义的。

核心经验

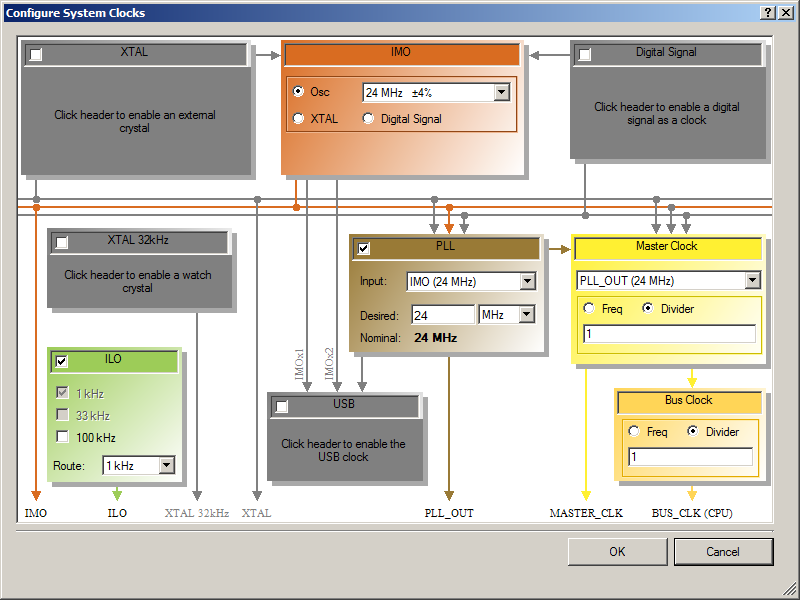

让我们做一个简单的项目。 让我们如下配置其块的时序:

PLL选择了尽可能低的频率(开发环境不会降低频率)。 总线由它计时。 这是有意完成的。 工作的结果将由示波器控制,在

本文的评论中,我表明最好不要靠近通带的上限,特别是如果示波器是中文的话:前端会被阻塞,以至于您可能在测量中犯错。 因此,最好降低频率。 最小为24 MHz,我们接受。

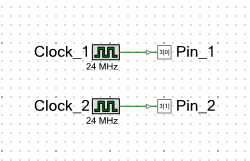

设计方案是微不足道的。 两个时钟脉冲源连接到芯片的引脚。

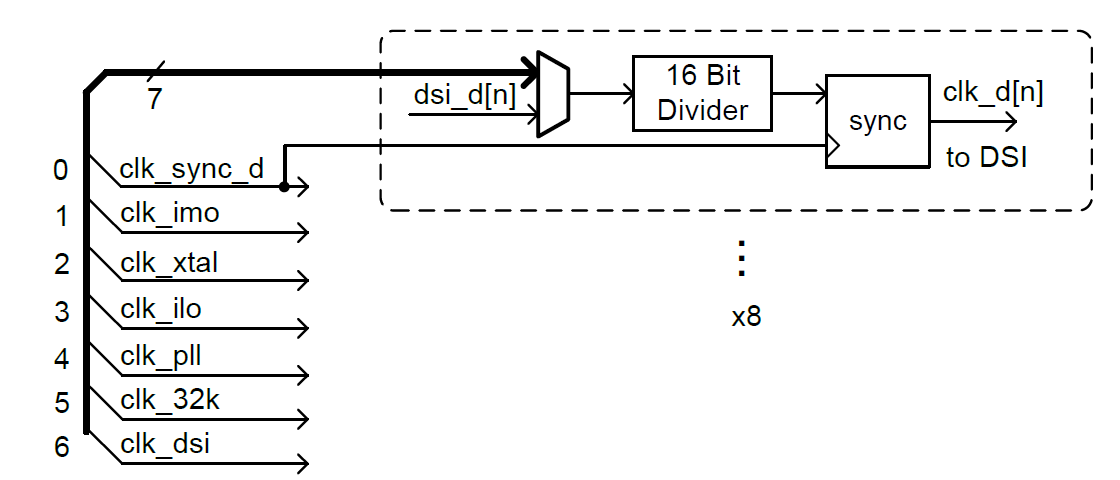

文件AN60631表示,系统将通过分频器从基座产生Clock_1和Clock_2源的频率:

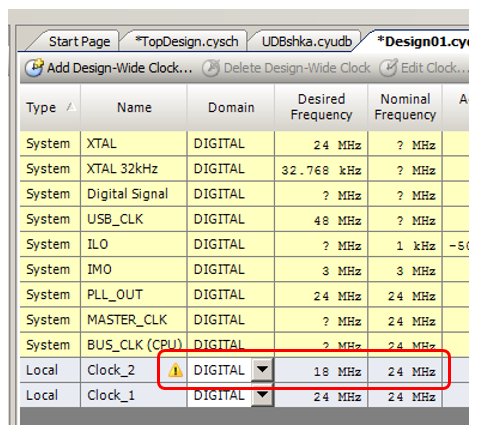

在我们的项目中,我们将始终将频率为24 MHz的信号发送到Pin_1支路,并尝试将较低频率的信号发送到Pin_2。 起初,一切都会按预期进行。 在23到18 MHz的所需频率下,我们可以达到等于24的频率。

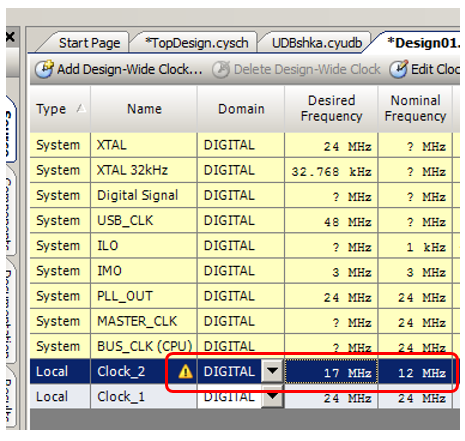

通过将所需频率降低到17 MHz,我们可以实现12。一切都是合乎逻辑的。 分频器不是PLL。 除法常数必须为整数。 只要确保没有意外。

将所需的频率设置为12 MHz。 我们正在组装一个项目(无需编写任何代码)并查看结果。

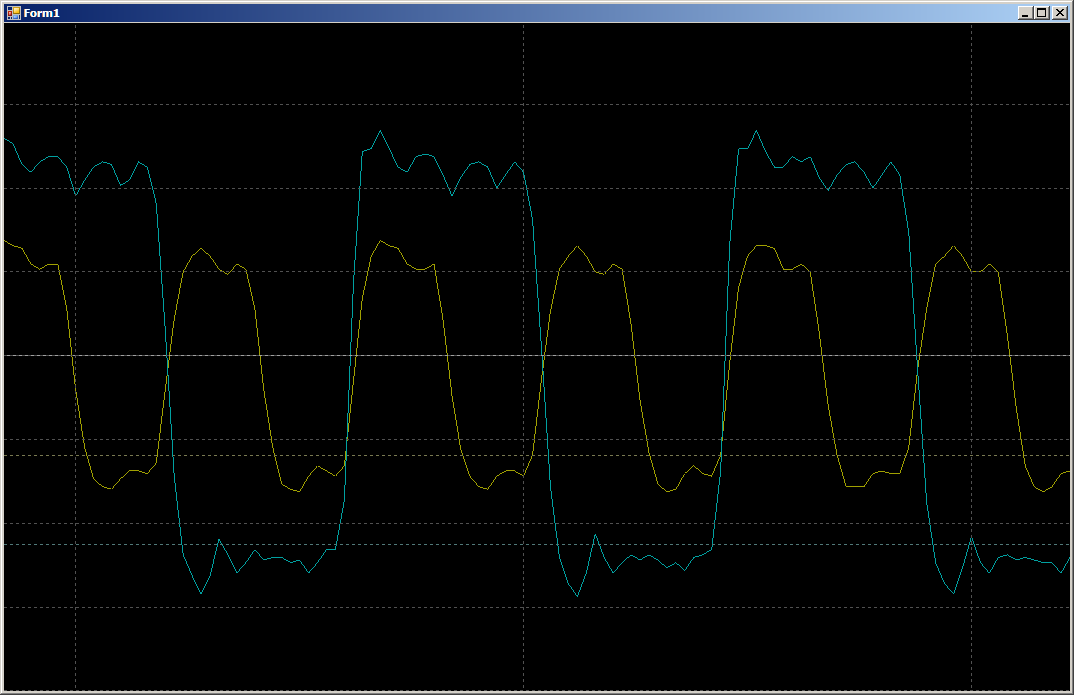

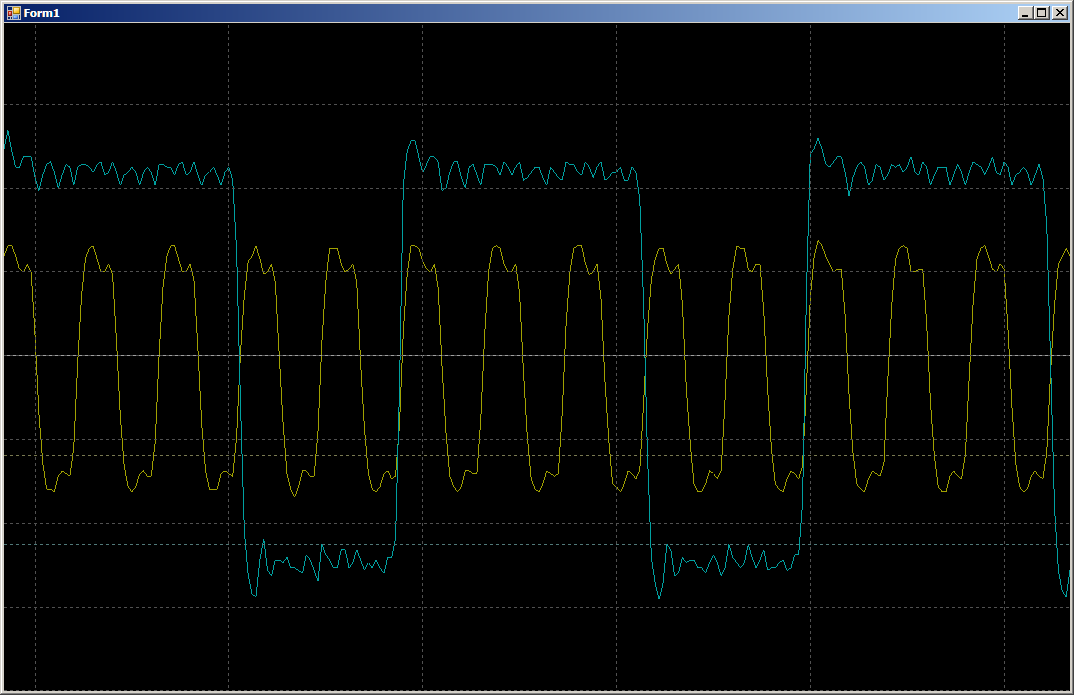

黄色光束是基频,蓝色是分频的。 再次没有抓住。 那么本文的目的是什么? 我们只是去最有趣的地方。 下一个分裂因素是什么? 三。 下一个可达到的频率是24/3 = 8 MHz。 我们更改项目设置,“闪烁”,看...

请爱护和偏爱,在蓝光上可以看到占空比不是50%的时钟信号。 一个简单的程序员是否期望时钟源能够为他提供时钟? 几乎没有 但是他发布了。

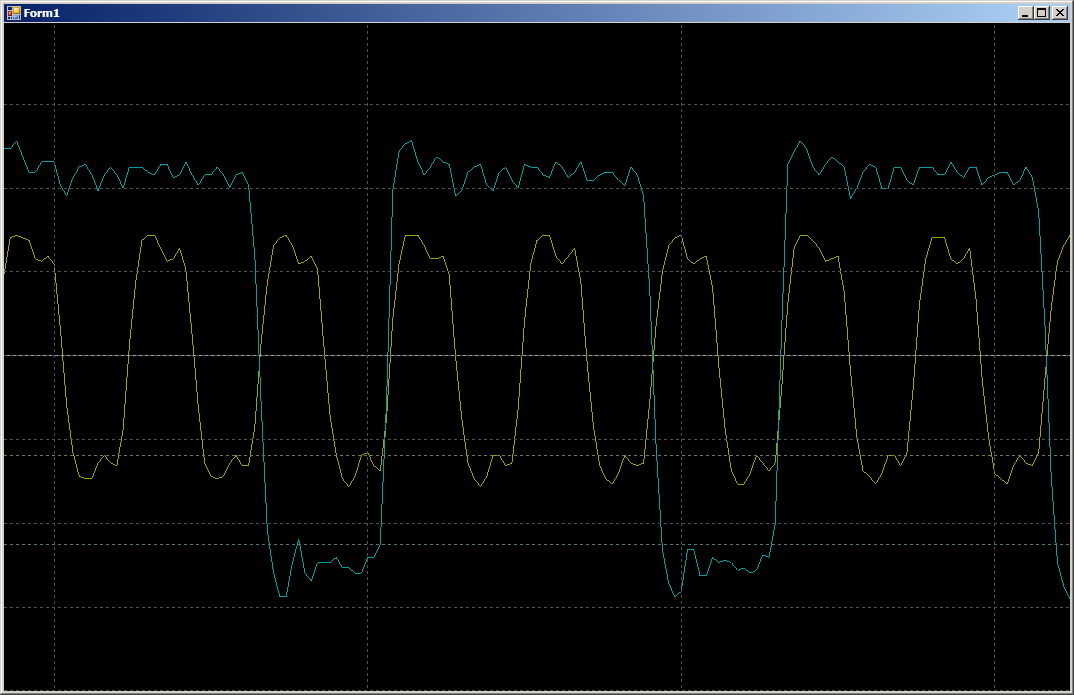

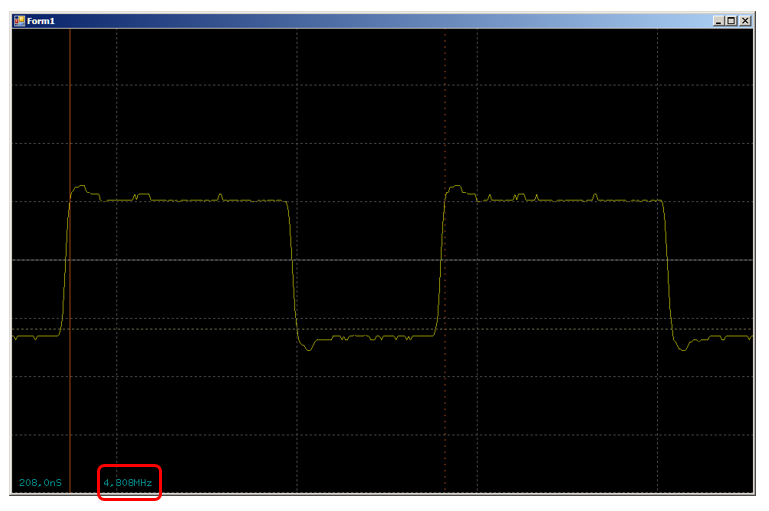

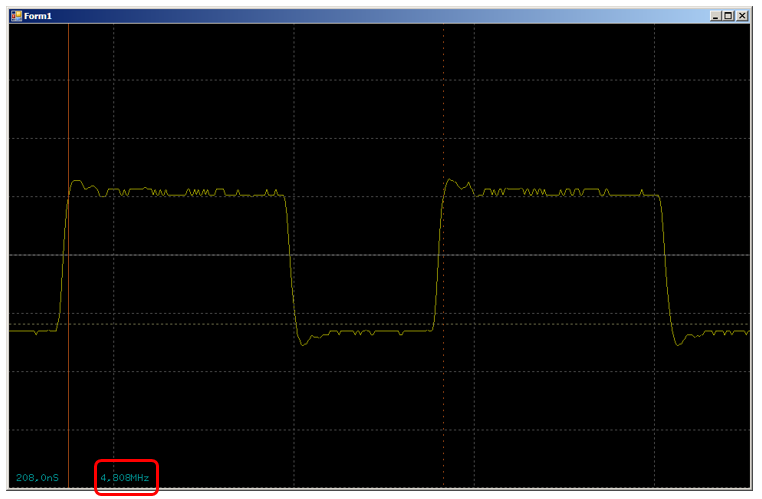

可以预见,除以4会很漂亮。 我们检查除以5(期望的频率为4.8 MHz):

趋势很明显。 PWM显然起着分压器的作用。 奇数分频比越高,占空比越接近50%,但通常,正半周期和负半周期之间仍存在一些差异。 如果电路仅由正前沿提供时钟,那么这并不可怕。 但是,如果开发人员自己制作了某个组件,其中同时使用了时钟信号的正沿和负沿,则可能会产生细微差别,有时还会出现浮动故障。

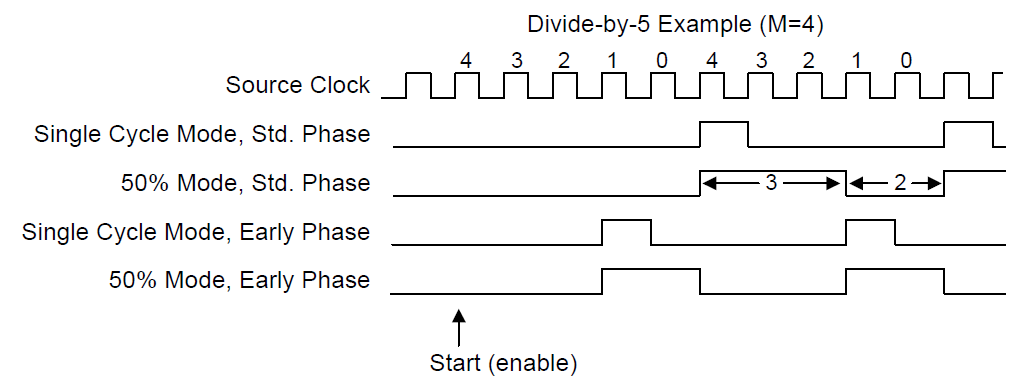

通常,在图14-12的TRM中或多或少描述了这种情况,因此,再也没有人隐藏任何东西:

但是有一点告诉我,很少有人会在示波器上捕捉到相应的图像之前就研究这种模式。 而且,只有经过长时间尝试找出系统崩溃的原因,他才会抓住她。 因此,我认为有必要警告PSoC时钟组件的此功能。

其他PSoC时钟信息

内部发电机频率的温度依赖性

结果很简短。 让我们再探讨一个与时钟速度有关的问题。 从前,我在AtMega8上做一个项目。 为了降低系统成本,时钟来自内部发生器。 该项目已在看台上进行调试,但随后发现,当板子进入目标环境时,只有在打开电源后才能正常工作。 几分钟后,一切都变热了,频率消失了,接收到的串行数据开始错误地解码。 而且,如果您在此模式下调整遮蔽物-一切都在预热之前。 在那个项目中,所有事情都是安全决定的:数据在曼彻斯特代码中,并且是自同步的。 我只是从包的开始而不是从包的开始进行同步。 但是对于将来,我了解到在控制器中使用内部发电机时,有必要检查其热稳定性。 我们将使用PSoC对其进行检查,因为现有面包板上没有石英谐振器,因此系统由位于控制器中的内部振荡器作为时钟源。 对于我的任务,控制器本身尚未为我加热,但是可以由位于同一板上的组件加热。

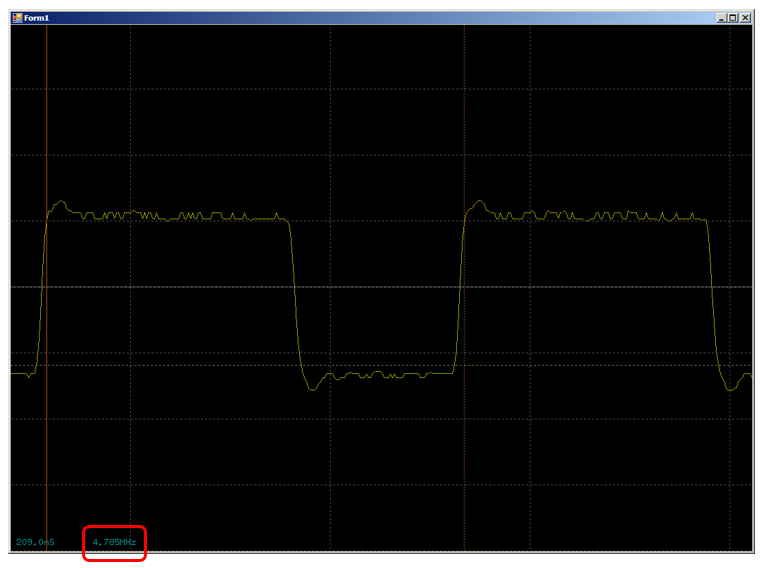

在24 MHz的频率下,前端非常圆滑,您可能会犯一个错误。 让我们将获得的频率f / 5用于实验。

顺便说一句,这不是4.8,而是4.78 MHz。 没关系! 发电机可以校准! AN60631表示,通常情况下,这是由端口IMO_TR0和IMO_TR1中的11位寄存器引起的。 CE219322中介绍了如何使用外部参考发生器自动计算其最佳值。 该文档甚至附有示例。 但是在我的试验板上没有单独的发生器,因此,对于一个实例,我更容易根据经验来选择该值,重点放在示波器的读数上。 将以下代码添加到main()函数(增量步骤为0x20,因为未使用低5位):

volatile uint16_t* ptr = (uint16_t*) CYREG_IMO_TR0; ptr[0] += 20 * 0x20;

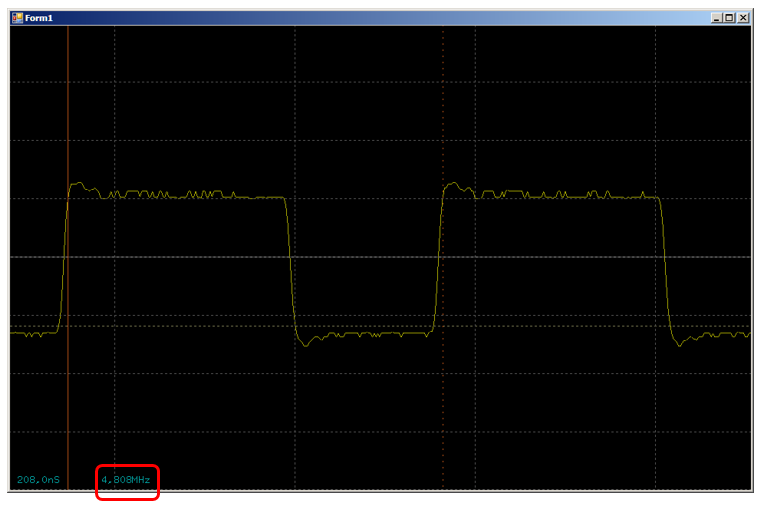

我取得了相当不错的成绩:

我们把木板放在阳台上,那里现在大约是零。 频率几乎没有变化,但是在现有的示波器上甚至很难测量。 肉眼可见(在左光标和黄光束的交点处)。

现在,我们加热电池板上的电路板。 同样在设备上看不到差异。

因此,在PSoC中,生成器非常稳定。 他不应期望工作系统开始出现大错误的频率发生剧烈变化。

内部发电机的频率对电源电压的依赖性

我已经写了这篇文章并作了粗略的阅读,因为另一个有趣的因素浮出水面,与时钟频率有关。 在一个项目中,频率测量的误差约为2%,这对于该任务至关重要。 此外,UDB中实现的逻辑已正确实现。 逻辑上没有错误。 我用示波器控制一切,我注意到参考频率仅为2%。

但是为什么呢? 还是很棒! 那时我想起了条款草案。 不仅取决于温度,还取决于电源电压。 有时我将其从5伏降低到3.3伏。 校准发电机的频率后,误差消失了。

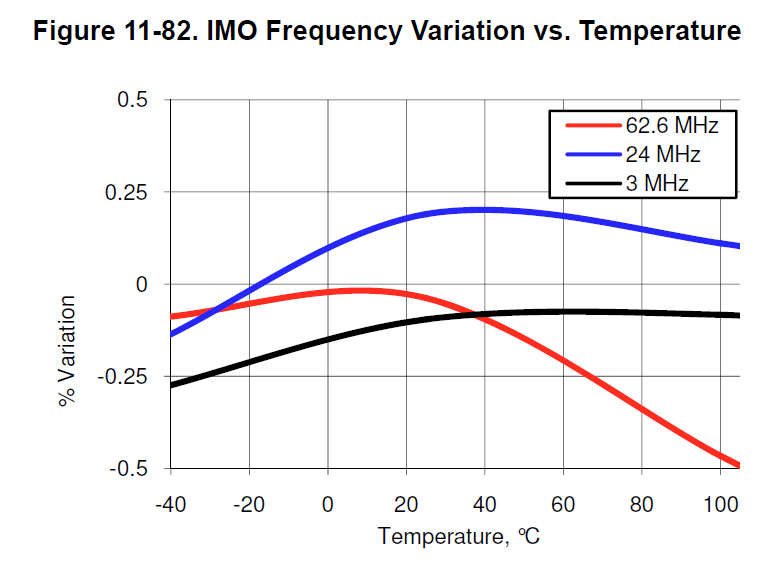

但是在那之后,人们希望在文档中找到依赖项。 事实证明,它们都在特定芯片的DataSheet中列出。 这是发电机误差的温度依赖性

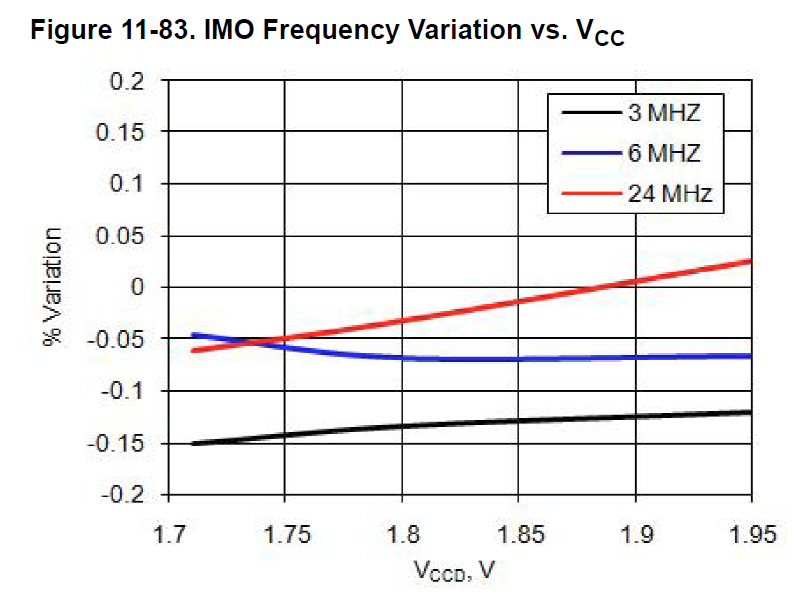

我的时间表是蓝色的。 通常,一切都与实际结果一致。 这是电压依赖性:

在这里,所需的时间表是红色的。 在2%时,他显然没有拉力,但是误差线性增加是明显的。

结论

在PSoC Creator中使用标准时钟组件时,应做好以下准备:脉冲的占空比不会达到50%。 如果项目不仅使用前端,还使用信号切片,则这一点很重要。 为了消除这种影响,您应该将基本频率除以偶数系数。

对于对频率误差敏感的应用,建议仅在稳定的电源电压下使用内部时钟(IMO),对于组装后的每个特定产品,建议校准频率。 如果期望电池不稳定,则最好使用外部石英谐振器。