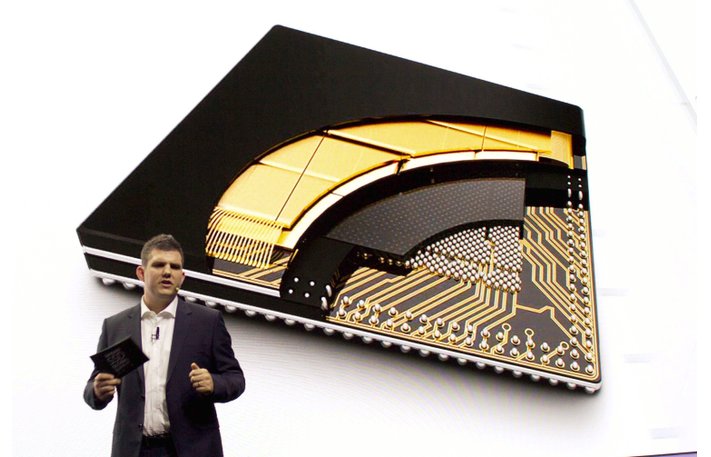

英特尔Foveros 3D

英特尔Foveros 3D由于摩尔定律不再适用,芯片设计人员必须寻找其他方法来提高性能。 一种适合的技术称为3D芯片堆叠。 这是芯片的三维堆栈体系结构,英特尔在这一领域处于领先地位。 两个月前,英特尔推出了

Foveros 3D架构:一种三维结构,包括一个10nm CPU,一个I / O芯片和位于芯片中央的TSV(直通硅通孔)垂直电连接,以及位于整个芯片顶部的存储芯片。

在Rice Rice and Gas HPC高性能计算会议上,AMD

保证它正在开发自己的3D芯片体系结构版本。

高级副总裁兼总经理福雷斯特·诺罗德(Forrest Norrod)表示,该公司正在开发几种技术,以提高回报率,并绕开与终止摩尔定律以及停止晶体管密度和时钟频率增长的后果相关的问题。 这些是制造商接近极限的不可避免的后果,在该极限中,晶体管的尺寸仅为几个原子(硅原子的尺寸为0.2纳米)。 近年来,计算机功能的增长并不是因为计算速度的提高,而是由于并行性的提高。

与其他公司一样,AMD面临约700mm²芯片面积的限制,并被迫开发3D架构。 该公司已经在采用这种方法,将HBM2内存放置在GPU基板旁边,也就是说,与处理器的情况相同。 但是在将来,该公司计划转向更高级的3D堆叠。

Norrod说,AMD正在努力将SRAM和DRAM直接放置在计算组件(例如处理器和GPU)的顶部,以提供更大的带宽和性能。

三星北极星

三星北极星这种方法与通常的层叠式包装(PoP)实施方式不同,后者只是将两个完成的包装箱相互叠放,如Norrod所示,以三星Polaris芯片为例。 在此示例中,DRAM外壳通过围绕基础芯片的另外两行BGA连接器连接。 这些BGA连接器在两个芯片之间传输数据。 与任何标准设计一样,由于需要更多的连接器,因此逻辑位于堆栈的底部,但两个晶振并未直接连接。 因此,PoP方法可提供最大的密度,但这不是最快的选择。

在真正的3D堆叠中,两个芯片(在这种情况下为内存和处理器)彼此叠置,并通过直接与它们直接连接的垂直TSV连接进行连接。 这些TSV连接以最快的速度在晶体之间传输数据,通常位于芯片的中央,就像我们使用Intel Foveros 3D所看到的那样。 这种直接配对可提高性能并降低功耗(所有数据移动都需要电源,但是直接连接可优化过程)。 3D堆叠还可以提高密度。

Norrod没有详细介绍正在开发的项目,但这可能是AMD处理器设计的根本转变。

Tom's Hardware 写道 ,新的Intel Foveros 3D技术可能成为该行业的决定性时刻,因此听到AMD朝着这个方向发展并不奇怪。

到目前为止,除了Forrest Norrod在题为《超越摩尔定律的工作》的演讲中所说的以外,没有关于AMD 3D堆栈技术的技术细节,请参见下面的视频。

还有什么其他选择可以返回到戈登·摩尔预测的指数增长曲线? 这个问题没有单一答案。 半导体行业正在尝试使用可以代替硅的材料。 某些III-V半导体材料可以

比硅更低的电压和更高的频率工作 ,但是它们不会使原子变小或变慢。 身体上的限制仍然适用。

问题仍然是未来的3D芯片将如何冷却。 当能量分布在整个芯片上时,如何有效地冷却它? 微电路将无法同时向所有电路传输功率而不会导致过热。 她可能大部分时候必须断开某些零件的连接,并仅在使用过程中为每个零件供电。