前几天,

日本自动站Hayabusa-2向小行星Ryugu投下了一枚炸弹 。 该航天器由辐射稳定系统控制,该系统基于HR5000芯片(JAXA2010 / 101),带有64位MIPS 5Kf处理器内核。 机载计算机运行uITRON实时操作系统,该系统是TRON标准RTOS系列之一,该系统于1980年代在日本出现

,应另作文章 。

在本说明中,我将简要描述HR5000 SoC及其处理器核心中的内容,我将展示MIPS 4K和5K系列的两个关键开发人员的照片,并告诉您如何与该计算机的“后裔”一起在FPGA上在家玩- 32位MIPS microAptiv UP内核,其Verilog硬件描述语言的代码基于MIPS 4KEc。

日本航空航天公司JAXA从美国公司MIPS Technologies获得了MIPS 5Kf处理器内核的许可。 这发生在2000年代。 开发此核心的小组以各种配置存在了40年:

- 首先,在1978-1984年,MIPS是由约翰·轩尼诗(John Hennessey)领导的斯坦福大学项目。 随着该项目的成功,轩尼诗成为史上最著名的计算机体系结构教科书的作者,并成为斯坦福大学的总裁。

- 然后,在1984年,MIPS成为一家商业公司-MIPS Computer Systems。 同年,ARM也商业化。 1991年,MIPS发布了世界上第一个64位微处理器-MIPS R4000。

- 此后,MIPS被Silicon Graphics所吸收,并在1990年代用于制图站,在那里第一部具有逼真的图形的电影在好莱坞(侏罗纪公园)制作。

- 在2000年代,该小组分为MIPS Technologies,特别是为JAXA设计了处理器。 MIPS的总部位于加利福尼亚;一些MIPS 5Kf开发人员位于哥本哈根的 MIPS欧洲。

- 2012年,MIPS Technologies被英国公司Imagination Technologies收购,后者以早期Apple iPhone中的GPU开发人员而闻名。

- 2017年,苹果公司抛出了Imagination,在经历了一些混乱之后,该技术和MIPS集团的一部分被整合到了Wave Computing公司中,该公司开发了一种芯片来加速神经网络。

- Wave Computing芯片由64位MIPS I6500处理器集群,基于脉动阵列和Google TPU的矩阵乘法器以及基于具有粗粒度可重配置架构-CGRA的设备的数据处理器处理器组合而成) I6500集群中的经典处理器会加载矩阵乘法器和数据流处理器,矩阵乘法器提供计算密度,而任务数据处理器位于经典处理器和矩阵乘法器之间的中间位置-它比乘法器更加灵活,比经典CPU更具生产力。

因此,我与MIPS 4K和5K系列的两个主要开发人员之一合影了-Larry Hudepohl,Larry Huedepol(穿着红色衬衫)。 Larry在Digital Equipment Corporation(DEC)担任MicroVAX的处理器设计师,开始了他的职业生涯。 然后Larry在一家小型公司Cyrix工作,该公司在1980年代后期挑战了Intel,并制造了与Intel 80387兼容且速度提高50%的FPU协处理器。 然后,拉里(Larry)在Silicon Graphics公司设计了MIPS芯片。 当MIPS Technologies从Silicon Graphics分离出来时,Larry和Ryan Quinter共同推出了第一个独立的MIPS产品MIPS 4K,该产品成为主导2000年代家用电子产品(DVD播放器,照相机,数字电视)的产品线的骨干。 然后,MIPS 5K飞入太空-日本航天局JAXA使用了它。 然后,作为硬件工程副总裁的Larry领导了以下几行的开发,现在他正在研究新的Wave加速器体系结构:

现在回到Hayabusa-2中的处理器(在Hayabusa-1中是不同的)。 这是

MIPS64 5Kf处理器内核的

数据表,以及

在HR5000芯片上包含系统数据的

页面 。 注意一些有趣的观点。

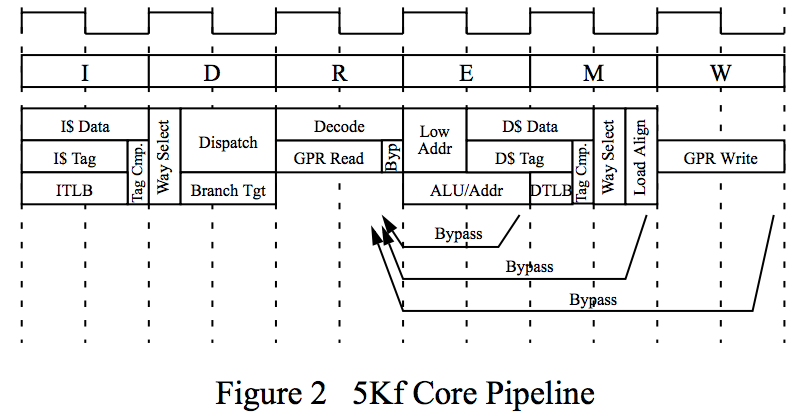

首先,MIPS 5Kf是流水线处理器。 如果您不熟悉它的工作原理,那么最容易彼此了解的方法是研究David M. Harris和Sarah L. Harris所著的《数字电路与计算机体系结构》一书的第七章,该书的最新版本可以在

此处或

此处下载为俄语) 。 MIPS 5Kf中的输送机不同于Harris&Harris的经典MIPS输送机。 那些阅读过X&X的人可以查看差异并猜测原因:

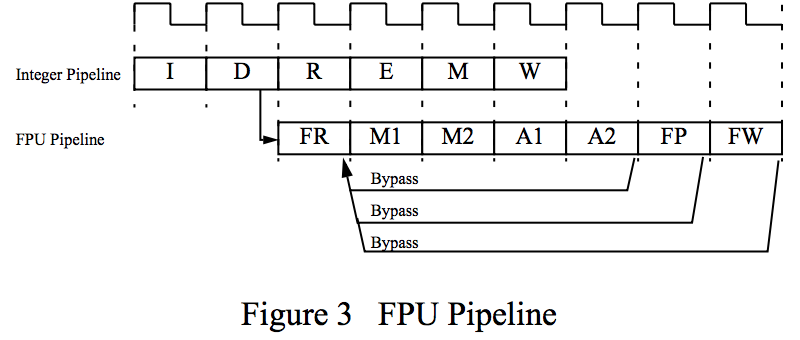

当然,MIPS 5Kf没有五个流水线阶段,而是六个,还有一个附加的Dispatch阶段。 要使MIPS 5Kf有界地成为超标量,需要这个阶段。 它不仅可以在流水线中一个接一个地执行操作,而且还可以与整数操作或内存操作(加载或保存)同时执行浮点操作。 Stage Dispatch启动浮点协处理器,该处理器具有自己的七级管道:

照片的右边是MIPS 5Kf的FPU开发人员Darren Jones,Darren Jones。 “ 5Kf”中的字母“ f”确切表示它具有浮点数:

在此板上,您可以看到FPU中需要多少个周期进行不同的操作,以及它们在管道中可以运行的频率(重复率)。 例如,单精度乘法需要四个周期,但是您可以在每个周期的管道中开始一个新的乘法。 因此,FPU可以在每个处理阶段同时处理四个单精度乘法。 但是双精度乘法需要五个周期,并且只能在周期中暂停才能开始。 进行双精度平方根的复杂操作需要多达32个循环,并且只能在29个循环后才开始对平方根进行新的计算。 这是如何优化船舶坐标及其在外层空间中的运动公式的计算:

Hayabusa-2将MIPS 5Kf配置与单独的32 KB指令和数据缓存一起使用。 同时,从

HR5000的

简要说明中还不清楚它是使用8 KB的四通道高速缓存还是使用16 KB的两通道高速缓存。 您可以在X&X和

旧的有关缓存的演示文稿以及有用的书

《 Dominic Sweetman的MIPS Run Linux 2nd Edition》中阅读这些缓存的工作方式

:

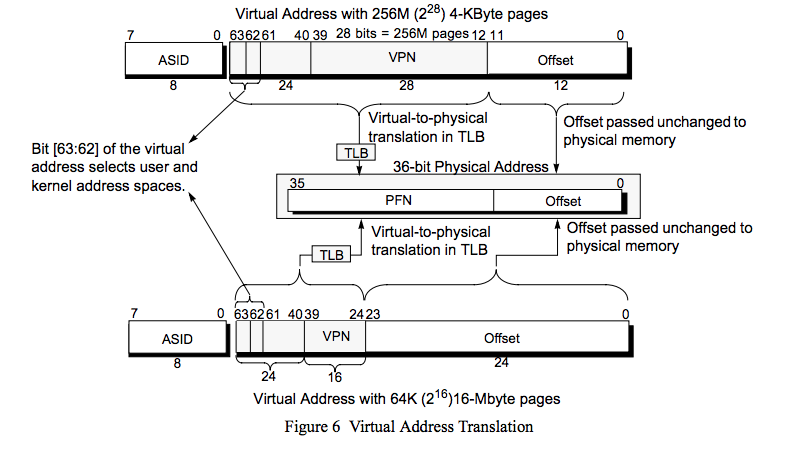

Hayabusa-2还具有一个内存管理单元(MMU)和一个转换后备缓冲器(TLB)。 TLB是用于快速将地址从虚拟地址转换为物理地址的通用工具。 TLB允许您:

隐藏非特权代码中的操作系统内存。

保护用户程序彼此之间。

提供对超出物理RAM量的虚拟内存量的程序访问。

提供比虚拟地址更大的物理内存地址。

将程序放在物理内存的任何部分。

允许多个内存区域看起来像一个连续的片段。

允许您根据需要从外部设备加载程序片段。

TLB还将各种属性与该地址相关联:读取,写入和执行以及高速缓存和一致性属性。

TLB可以存储一个指示符,指示已记录了具有给定地址的页面。 这在物理内存少于应用程序需要用虚拟地址来寻址其所有代码和数据的系统上进行交换,加载和卸载内存页面时会有所帮助。

这就是将MIPS 5Kf上的64位虚拟地址转换为36位物理地址的样子。 为什么在Hayabusa-2上使用具有36位物理地址的64位处理器? 我怀疑Hayabusa-2拍摄照片并且必须处理图像,这需要大量内存。 也许对于某些算法,64位算术和64位缓存交换(或64位不可缓存的内存交换)有所改进,并且在空间上很有用。 但是我不确定,我可能需要问

Zelenyikot和

amartology ,他们比我对太空的了解要多。

您可以在X&X中阅读有关TLB的信息,并查看MIPS Run,但有一个细微差别:这两本书都从程序员的角度描述了TLB的外观。 但是从硬件开发人员的角度来看,尽管实际上TL内部有三个表,但处理器设计人员通过将TLB显示为一个关联的转换表来欺骗程序员,尽管实际上这三个表是:三个micro-TLB指令,一个micro-TLB数据和一个共同的(联合TLB)。 首先,内存管理设备搜索ITLB和DTLB,并且只有在找不到它的情况下,它才会从JTLB获取它。 这会使处理器额外花费2个周期。 另请参阅

我在TLB上的旧演讲 :

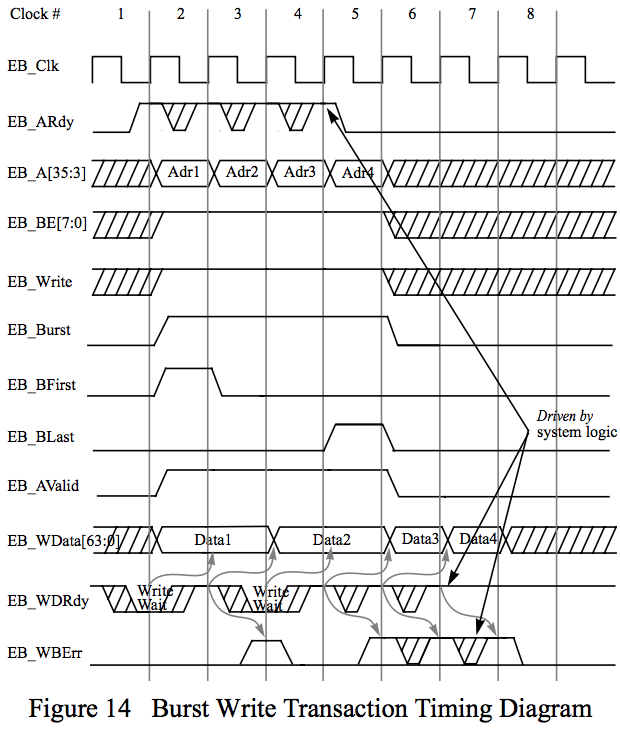

Hayabusa-2中MIPS 5Kf中一级缓存和内存控制器之间的接口称为EB(发音为IB)。 这是外部总线的缩写。 它类似于AHB和AXI,并允许您使用顺序循环中的传输来突发,从高速缓存中转储或从内存中填充整行。

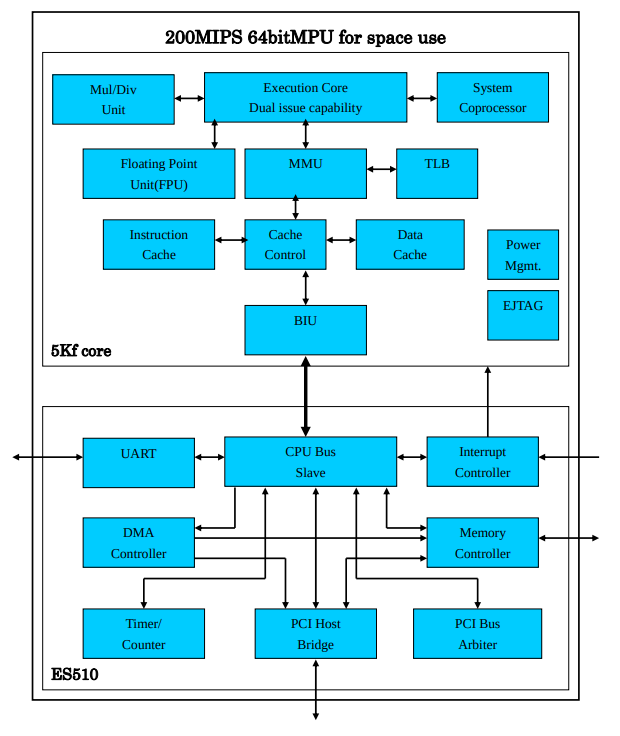

HR5000在处理器内核之外,具有中断控制器,UART模块,直接存储器访问控制器,计时器和PCI控制器:

要在太空中工作,必须保护芯片免受辐射。 我不是辐射防护方面的专家,因为哈布雷(Habré)上有这方面的

知识 ,但我知道可以在物理生产技术级别,各种ECC检查级别甚至架构级别,三重级别等进行这种保护。 HR5000晶体系统的创建者决定使用商业应用中常用的RTL2GDSII路由,从Verilog硬件描述语言的代码中的逻辑元素合成图形。 但是,在收到这样的图形(网表)之后,他们使用特殊的图元按设计硬度(HBD)库对其进行了修改(从未使用过,因此欢迎在注释中进行任何澄清):

由于MIPS 5Kf是用Verilog编写的,因此它不仅可以转换为网表,而且不仅可以转换为用于在工厂制造芯片的掩模,还可以转换为FPGA配置。 不幸的是,MIPS 5Kf源不在公共领域,而是在公共领域中是他的“弟弟”的后代(32位MIPS 4K处理器)的源。 该“后代”称为MIPS microAptiv UP,其基本配置包含在MIPSfpga软件包中。 MIPS 4K / 4KEc / microAptiv UP / M5150代码(这是该系列产品的所有渐进版本)也是由Larry,Ryan和Darren编写的。

您可以使用管道,缓存,内存管理设备和MIPS microAptiv UP内核中断,在模拟器或带有FPGA / FPGA的板上运行它。 为此,只需下载

MIPS Open™FPGA入门软件包以及

MIPS Open™FPGA Labs ,然后(这很重要!)与

MIPSfpga +互补。 在后者中,有

关于管道,缓存和内存管理设备的实验室 。

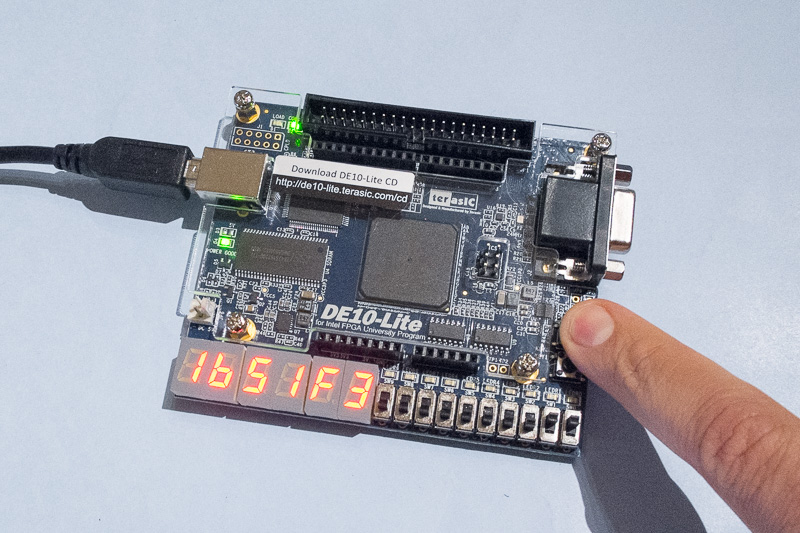

您可以在便宜的板上合成并运行MIPS microAptiv UP处理器,价格为85美元(学术价格为55美元):

要使用MIPSfpga / MIPSfpga +软件包,您需要有关Verilog硬件描述语言的知识,在寄存器传输级别的设计原理以及用MIPS汇编程序编写的能力。

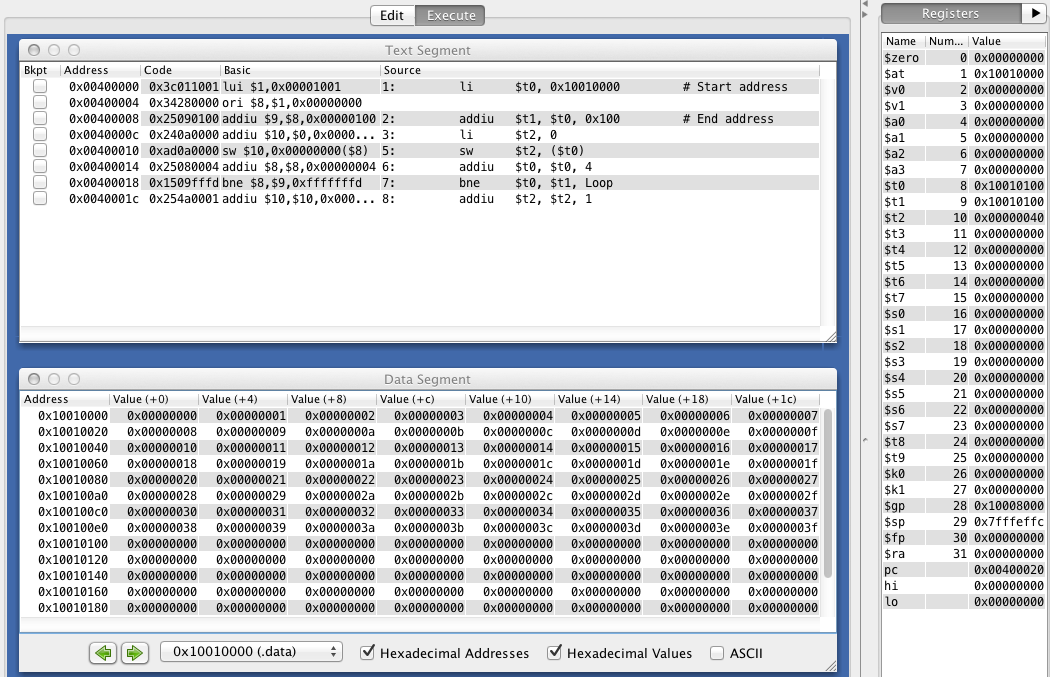

MIPS汇编器最容易学习。 为此,您可以

下载MARS模拟器(MIPS汇编器和运行时模拟器) 。 您可以在5分钟内学习如何使用它,实际上,其中有三个按钮-组装,运行,逐步运行:

然后,您可以花一天的时间练习用汇编语言编写书籍

Harris和Harris和

See MIPS Run Linux 。

如果您对数字电路的总体发展,尤其是对设备的描述语言一无所知,则可以从Rosnanov在线课程开始,该课程分为三个部分:

“从晶体管到微 电路” ,

“ 数字电路的逻辑端” ,

“物理端”。数字电路” )。 然后,您可以在X&X上研究Verilog,并了解简化的

schoolMIPS处理器上有一个处理器。

如果您对此主题感兴趣,并希望参与

MIPS Open (在其框架内

打开了MIPS microAptiv UP内核)的工作,请在评论中写下。 Rosnanovtsy还

于4月17日至19日为小学生举办了

数字设计研讨会 ,除其他事项外,该

研讨会将包括该空间处理器。 Hayabusa-2轰炸了Ryuga并没有白费-这也是俄罗斯学童和学生了解她内心的一次机会。