赛普拉斯官方文档中有关定时和复位管理的下一章。 正如本系列第一篇文章中已经提到的那样,该模块提供了时序选择和分辨率,以及UDB中的重置选择。 更多细节-在削减。

循环的一般内容是“ UDB。 这是什么?

第1部分。简介。 请第2部分。数据路径。第3部分。数据路径FIFO。第4部分。数据路径ALU。第5部分。数据路径。 有用的小东西。第6部分。管理和状态模块。第7部分。定时和复位控制模块。 (当前文章)

第8部分。处理UDB21.3.4复位和时钟控制模块

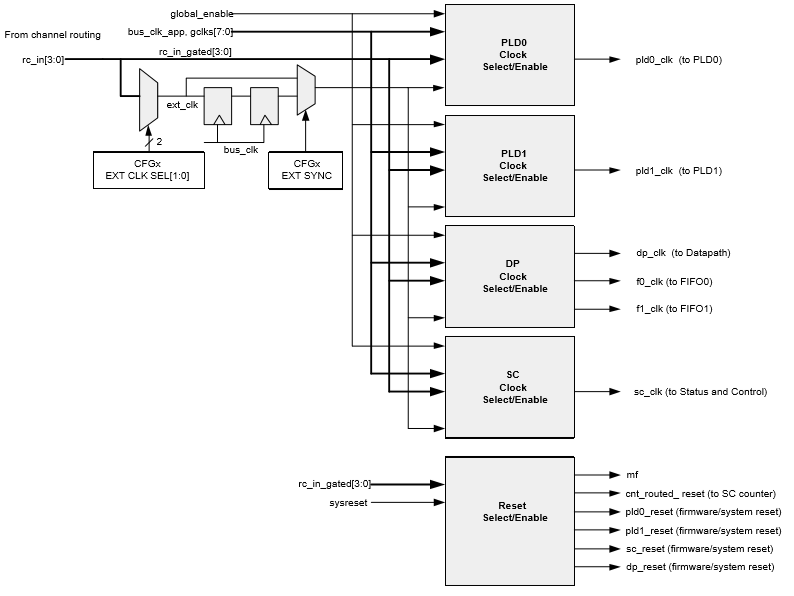

该模块的主要功能是从可用的全局时钟或总线时钟中为每个PLD,数据路径以及控制和状态模块选择时钟。 该模块还支持动态和软件UDB块重置。 如图21-38所示,有四个时钟控制单元和一个复位控制单元。 四个输入(RC_IN [3:0])可用于从全局跟踪矩阵转发。 每个时钟控制单元都可以从这些跟踪输入中为时钟使能输入选择一个源,并且还有一个多路复用器,您可以从中选择一个跟踪输入作为外部时钟源。 从图中可以看出,可以同步选择外部时钟源。 对于每个UDB组件,都有10个时钟可供选择:8个全局数字时钟,一个总线时钟和一个选定的外部时钟(ext clk)。 任何跟踪的输入信号(rc_in)都可用作电平敏感激活器或边缘敏感激活器。 该模块的复位功能提供了PLD模块和SC计数器的跟踪复位,以及通过编程方式复位每个模块以支持重新配置的功能。

应用于时钟和复位控制模块的总线时钟与系统总线时钟不同。 该信号称为“ bus_clk_app”,并以与其他数字时钟信号相同的方式锁定。 系统总线时钟仅用于输入输出操作,并且每次访问都会自动解锁。 数据路径时钟发生器生成三个时钟:一个用于数据路径,一个用于每个FIFO信号。

图21-38。 时钟和复位控制模块。

21.3.4.1时钟控制

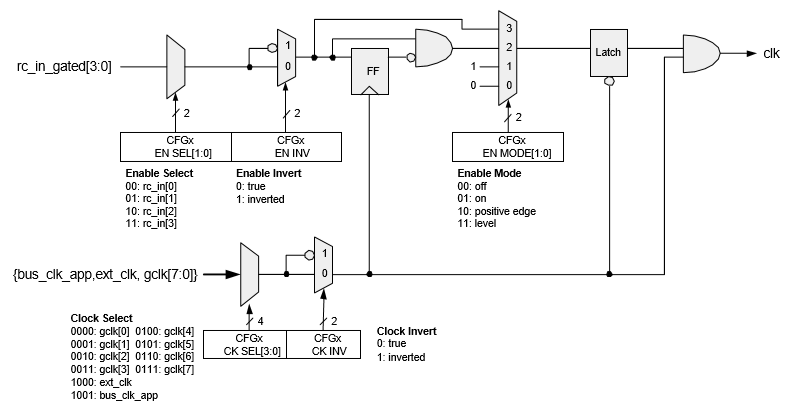

图21-39显示了时序选择和解决方案的示例。 每个UDB都有四种这样的方案:一种用于每个PLD块,一种用于数据路径,一种用于控制和状态块。 该电路的主要组件是全局时钟选择多路复用器,时钟反相器,时钟使能信号多路复用器,时钟使能信号反相器和差分检测逻辑。

图21-39。 管理时间选择/激活。

时钟选择有八个全球数字时钟转发到所有UDB。 可以选择其中任何一个。 全局数字时钟是用户选择的分频器的输出。 请参阅原稿的第109页的“定时系统”。 另一个选择是总线时钟,它在系统中具有最高频率。 该信号称为“ bus_clk_app”,与系统总线时钟分开跟踪。 此外,为了支持直接时钟信号(例如SPI)的功能,可以选择外部走线作为输入时钟信号。 由于应用程序功能绑定到UDB中的任意边界,因此为每个UDB子组件选择一个单独的时钟信号有助于在编程中实现精确的粒度。

时钟倒置所选时钟信号可以反转。 由于存在半周期的部分,这将限制最大工作频率。 当内部时钟反相并且具有与总线时钟相同的频率时,不支持同时进行总线记录和内部记录(例如,程序在其运行期间记录新的计数器值)。 此限制会影响A0,A1,D0,D1以及计数器模式下的控制寄存器。

时钟使能选择时钟使能信号可以转发到任何同步信号,并可以在该模块可用的跟踪矩阵的四个输入中的任意一个上进行选择。

时钟使能反转时钟使能信号可以反相。 因此,可以以任何极性生成该信号。

时钟使能模式默认情况下,时钟分辨率模式为OFF。 设置目标单元的操作后,软件可以使用CFGxEN MODE [1:0]寄存器设置以下描述的一种操作模式,如图21-39所示。

表21-23。 时序解析模式。

使用时钟权限有两种常见的计时权限用例。

软件启用(固件启用) :假定大多数功能需要启用软件时钟才能启动和停止功能。 由于绑定到UDB数组的函数的边界是有条件的,因此该函数可以跨越多个UDB和/或部分UDB。 因此,需要一种方法来原子地包括每个功能。 通常使用转发到一个或多个时钟使能输入的控制寄存器中的一位来实现。 此方案还支持应用程序需要同时运行多个不相关的块的情况。

模拟本地时钟生成:此功能允许UDB使用同步时钟激活实现模板生成本地时钟并将其分配给阵列中的其他UDB,而不是直接为每个UDB分别提供时钟。 使用上升沿功能启用分辨率可消除对分辨率信号占空比的限制。

特殊FIFO时序FIFO数据路径块具有定时功能。 默认情况下,FIFO时钟与数据路径时钟具有相同的配置。 但是,FIFO模块具有特殊的控制位,可以更改时钟配置:

- 每个FIFO时钟可以相对于所选数据路径时钟的极性反转;

- 当选择FIFO FAST模式时,总线时钟将替代通常使用FIFO的数据路径时钟。

21.3.4.2重置管理

重置管理模式有两种:继承的和标准的。 使用UDB CFG31的每个配置寄存器中的

ALT RES位可以设置该模式。 默认情况下,该位值为0(传统模式);默认值为0。 建议您将其分配为1(标准模式)。 标准模式具有更高的粒度-UDB中的各个块可以使用跟踪刷新。 有关传统模式的信息,请联系赛普拉斯。

PLD重置控制图21-40显示了PLD复位系统。

图21-40。 重置结构PLD。数据路径重置控制

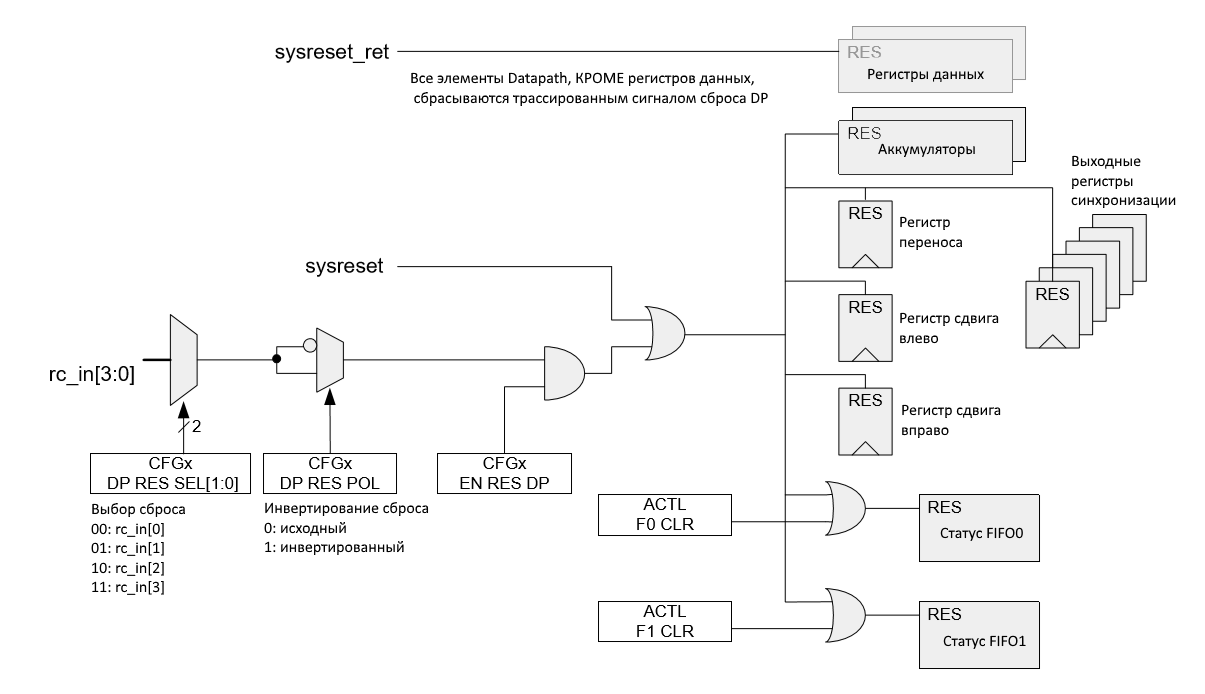

图21-40。 重置结构PLD。数据路径重置控制图21-41显示了数据路径重置系统。 跟踪刷新适用于所有数据路径寄存器和状态,数据寄存器D0和D1除外。 数据寄存器是持久性寄存器。 复位后,FIFO中的内容未定义,因为它位于RAM中。

图21-41。 数据路径重置结构。状态和控制重置控制

图21-41。 数据路径重置结构。状态和控制重置控制图21-42显示了控制和状态重置系统。 控制/计数器和状态寄存器具有通用的跟踪复位,但是它们是分别使能的。 掩码/周期重叠寄存器和辅助控件为保存寄存器。

图21-42。 重置管理和状态管理。

图21-42。 重置管理和状态管理。21.3.4.3上电UDB初始化(POR)

注册和状态初始化表21-24。 启用时初始化UDB状态

跟踪初始化启用后,跟踪输入和输出的状态具有以下功能:

- 将数据定向到跟踪矩阵的所有UDB输出均保持为“ 0”;

- 最初从跟踪走出并进入UDB输入的所有驱动器均被清零。

这种初始化避免了在跟踪期间发生冲突的状态,并且初始配置以顺序无关紧要的顺序发生。

结尾如下。 我们正在准备赛普拉斯有关UDB的专有文档的其余部分(即UDB寻址)的

最新翻译。