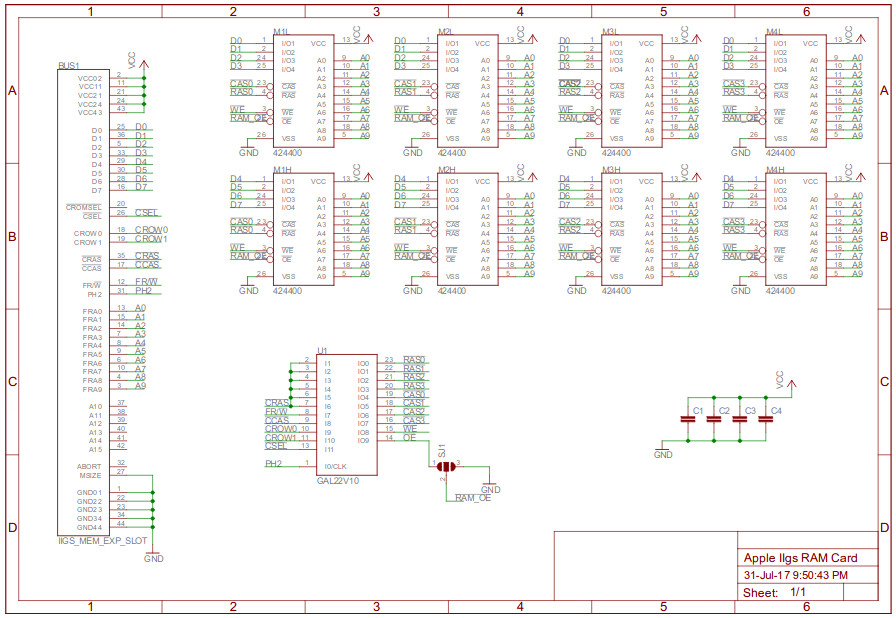

拟议中的Apple IIgs计算机RAM扩展板基于NEC uPD424400-70芯片,该芯片来自多个1兆SIMM模块。 这些微芯片中的每一个都存储1 M的半字节,并容纳在26引脚SOJ型外壳中。

Apple IIgs计算机由65位CC处理器(16位,但具有8位数据总线)供电。 扩展卡包含4 MB的RAM。 内存分为四行,每行1 MB。 该生产线由两个1 M半字节的芯片组成,因此总共需要八个芯片。

该计算机已经有用于RAM扩展卡的插槽。 它显示所有必要的信号,计算机还负责动态RAM的再生。 因此,扩展卡非常简单。 作者决定将电路板小型化,因为其制造成本取决于该成本,并将所有逻辑都放在GAL22V10 FPGA中。

RAM扩展插槽上显示以下信号:

FRA0-FRA9-10位多路复用单元地址,直接提供给动态RAM芯片的地址输入

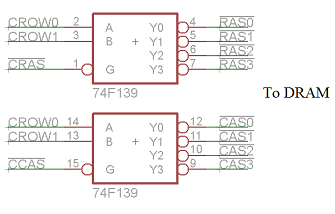

CROW0,1-2位选择四行之一

/ CRAS-动态RAM的信号选通地址线

/ CCAS-动态RAM的信号门控列地址

FR / W-RAM中的写入权限,此信号需要其他处理,请参见下文

D0-D7-数据总线,直接连接到RAM芯片的输入/输出线

/ CSEL-从RAM读取时,该行上会出现一个逻辑单元,必须将其反转并馈送到RAM芯片的输入/ OE

MSIZE-告诉计算机线路的数量:1-256 kB,0-1 MB,此处该线路连接到公共电线

14M,PH2CLK,A10-A15-不包含在建议的开发板中

必须对/ CRAS和/ CCAS信号进行多路分解以获得每条线的单独的/ RAS和/ CAS信号。 为此,74F139芯片是合适的(此后将了解,板上将没有单独的芯片,取而代之的是一个通用的FPGA)。

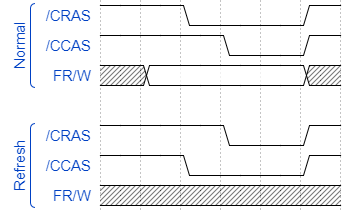

FR / W信号不能直接馈入动态RAM芯片的/ WE输入,这就是原因。 在正常的读写操作中,/ RAS行首先变为活动状态(对应于逻辑零),然后变为/ CAS行。 相反,在动态RAM再生周期中,/ CAS线首先变为活动状态,然后/ RAS变为活动状态。 但是所使用的芯片要求在/ RAS行激活之前,一个单元出现在/ WE行上。 并且来自Apple IIgs的FR / W信号不满足此要求。 再生周期中FR / W的状态不确定。 因此,需要一个检测再生周期并将单元馈送到/ WE的电路。

第一步是确定再生周期。 下面是时序图:

作者的想法是使用“透明”闩锁。 / CRAS信号是输入信号,/ CCAS是锁存信号。 当本机打开/ CCAS时,设备将通过其自身传递输入信号:输出状态在输入状态之后发生变化。 当/ CCAS从1变为零时,锁存器会记住输入端的信号,现在它在输出端不会改变。 在/ CRAS上的正常读/写操作中,/ CCAS从1切换为零时,零表示。 在/ CRAS上的再生周期中,将/ CCAS切换为零时也有一个。 然后,当/ CCAS切换回1时,闩锁再次变为透明。 它让人想起“第三行星的秘密”中的奇fantastic,它既可以是“镜子”又可以是“相机”。

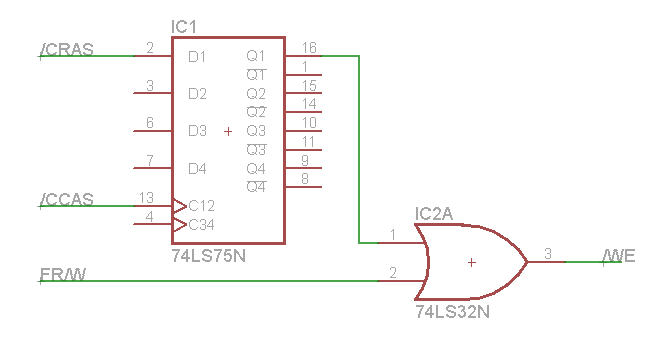

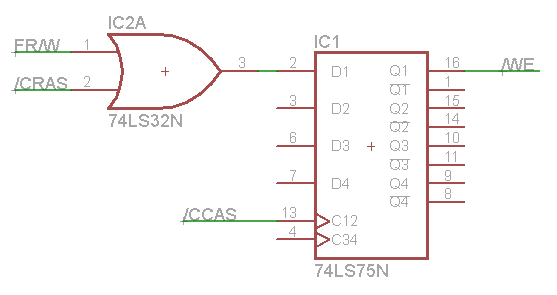

首先,作者拟定了以下方案:

但是要传输到GAL22V10 FPGA,需要两个输出引脚。 因此,该方案必须简化。 在正常操作期间,FR / W信号会一直取到期望值,直到发出喀嗒声为止,因此这也是可能的。

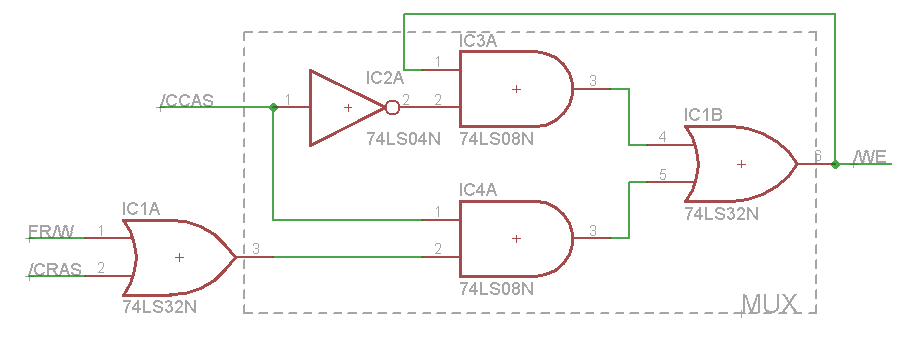

“透明”锁存器可以由多路复用器制成,而其又可以由逻辑元件制成。 该方案如下所示:

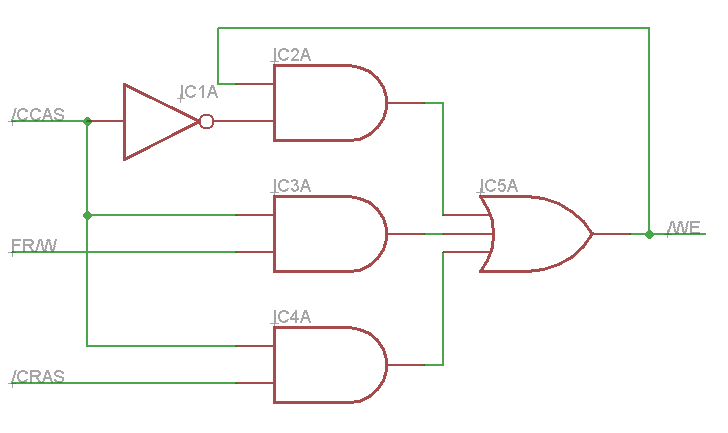

并经过简化-像这样:

该选项已传输到FPGA。 为了进行编译,作者使用WinCUPL。 该程序位于Atmel网站上。 它是原始的并且不断飞行,但是完美地完成了任务。 程序员-Genius G540。

板上的跳线SJ1就是这样。 如果连接了引脚1和2,则/ OE信号通过FPGA。 如果连接了引脚2和3,则将其连接到公共电线。 作者不确定用于确定再生周期的方案是否有效。 因此,他添加了该跳线,以防必须重做FPGA配置。

由于事实证明一切正常,因此您无需焊接引脚,只需用一滴焊料连接端子1和2。

为了减小电路板的尺寸,作者为每四个RAM芯片使用一个电容器供电,并将芯片本身放在电路板的两侧。

SOJ情况下的微芯片很难用烙铁焊接,尤其是焊接。 作者建议使用吹风机。

正确扩展芯片。 在最底线,它们是倒置的。 引脚1朝下。

一些通孔太靠近焊盘。 不要用焊料使它们短路。

相反,跳线的平台1和2关闭。

电容器C1-C3的电容为0.1 F,C4-10F。

作者在OSH公园下令董事会。 涂了ENIG涂层-金,但很薄。 对于游戏墨盒不适合-它将很快被擦除。 在这里,将板子放置在插槽中一次,并且没有从那里卸下更多。

作者感谢

GGLabs提供了类似电路板的电路,这对我们

很有帮助 ,谢谢!

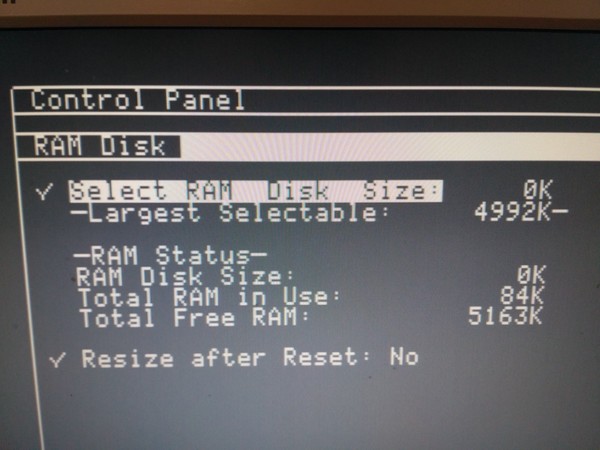

完成的电路结果如下:

档案:

FPGA固件 GAL22V10,WinCUPL程序版本5.30.4已应用

开发板 ,Eagle 7.1版软件

PDF大纲赚了!