小介绍:

编写自己的内核的想法是在托木斯克市通过一次关于数字电路的学校研讨会之后产生的 。 在此活动中,熟悉当前的硬件描述语言(Verilog HDL和VHDL),以及小型处理器核心schoolMIPS 。 为了了解核心的结构,决定按照schoolMIPS的发展道路发明自己的自行车,但以另一种指令系统为基础。 由于RISC-V的日益普及及其命令系统的开放性(编写内核时MIPS尚无开放的命令系统),因此选择了RISC-V指令集RV32I来开发未来的内核。 RV32I具有少量基本指令(特殊指令除外的37条指令),并且,如果需要,可以例如通过添加整数乘法和除法指令(RV32M)或支持压缩指令(RV32C)对其进行扩展。 另外,该项目被认为具有教育意义,因此决定最大化内核的可见性以有效地展示其工作。

与schoolMIPS相似,实现了以下内核版本:

- 单周期版本(00_simple_risc_v_cpu)。

- 支持lw / sw指令(加载字/存储字)(01_simple_risc_v_cpu_lwsw)的单周期版本。

- 管道版本(5级输送机)(02_pipe_risc_v_cpu)。

当前,正在描述具有完整RV32I命令集(不考虑某些特殊命令)的下一个内核版本(03_pipe_risc_v_cpu_fc)。

在内核描述的过程中,考虑了提高工作可见性,调试和验证的方法。 当前实现了以下方法:

添加一个调试文本VGA模块(用于两个单周期内核分支)。 通过包含此模块,您可以在监视器屏幕上同时跟踪32个寄存器的值,这在使用七段指示器上的信息输出时是不可能的。 在下面显示的图中,内核计算Leonardo数,并在相应的调试模块上显示信息。

hex_display和DebugScreenCore七段指标的信息输出:

VGA显示屏上的信息输出:

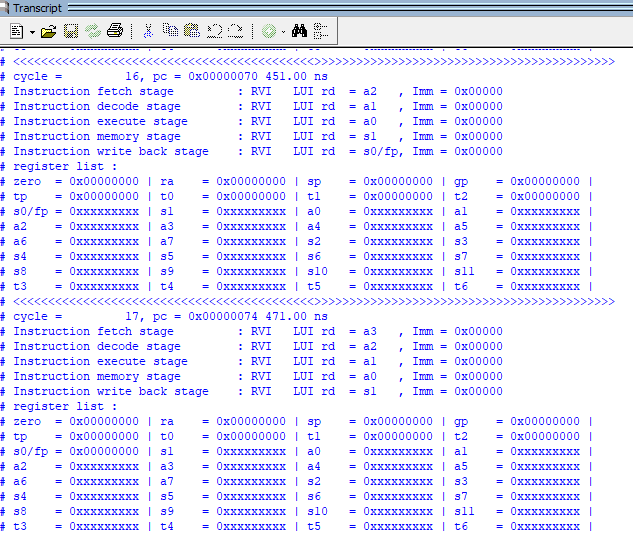

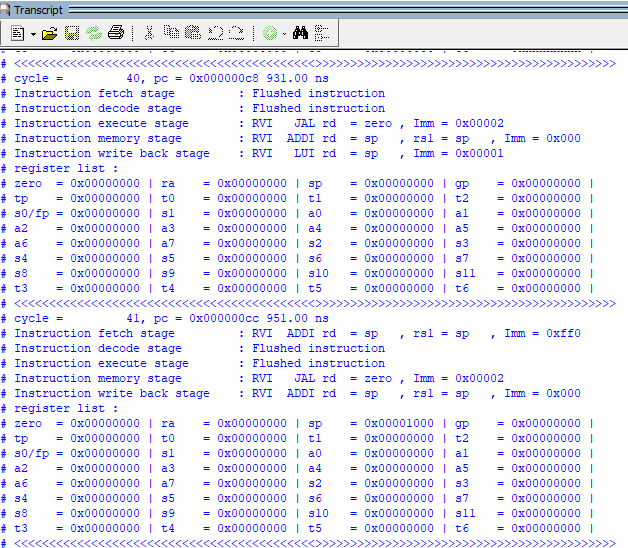

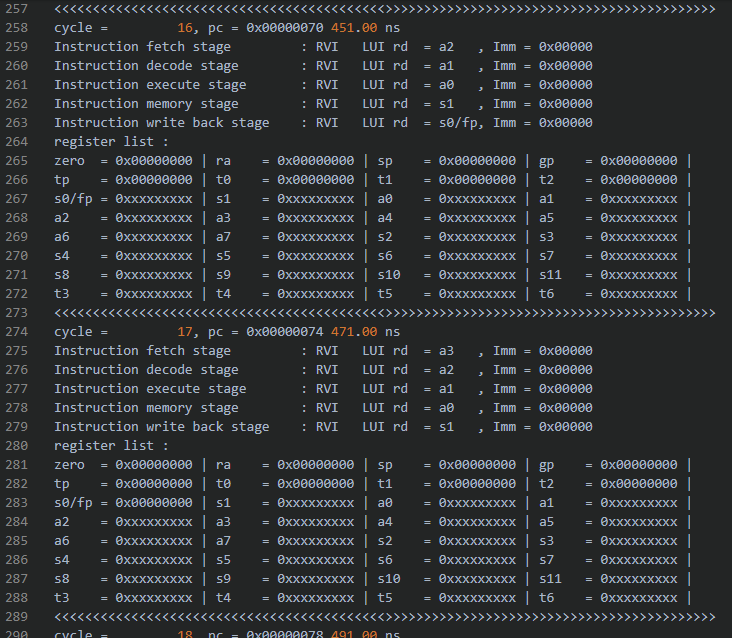

向模拟器终端添加有关寄存器文件状态和当前正在执行指令的消息。 这种方法可以使您在开发的早期阶段更好地分析内核的运行情况,但并不总是很方便。

航站楼寄存器文件的初始化:

更改sp值:

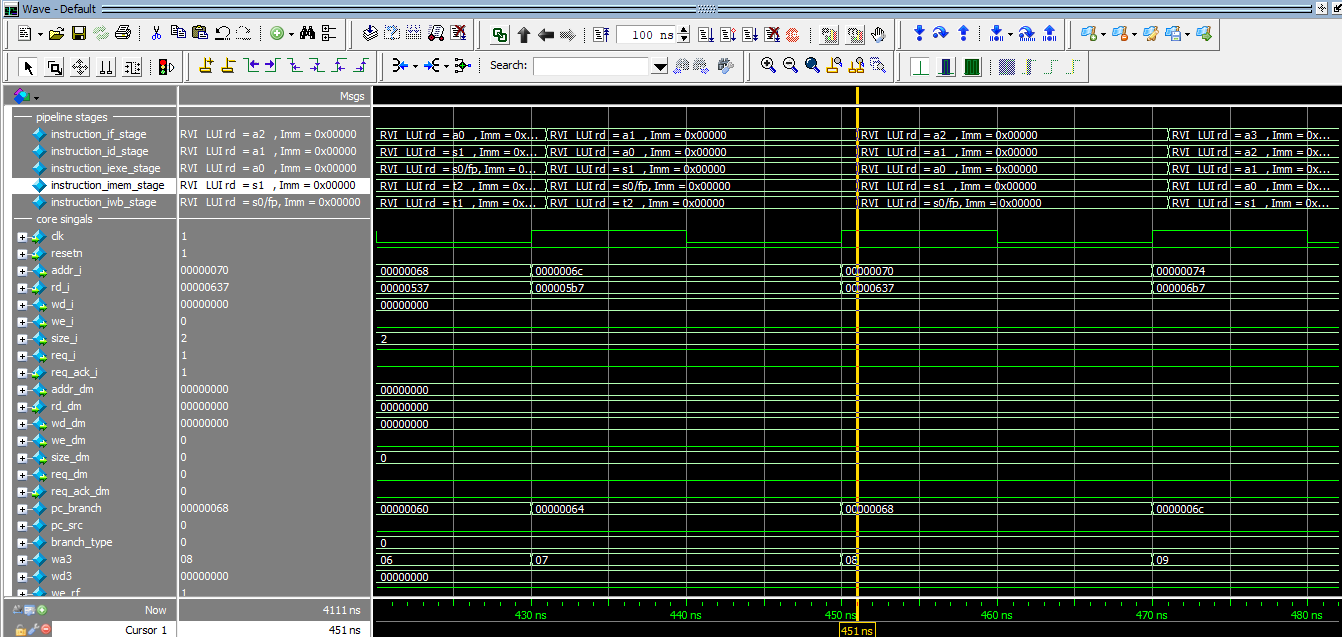

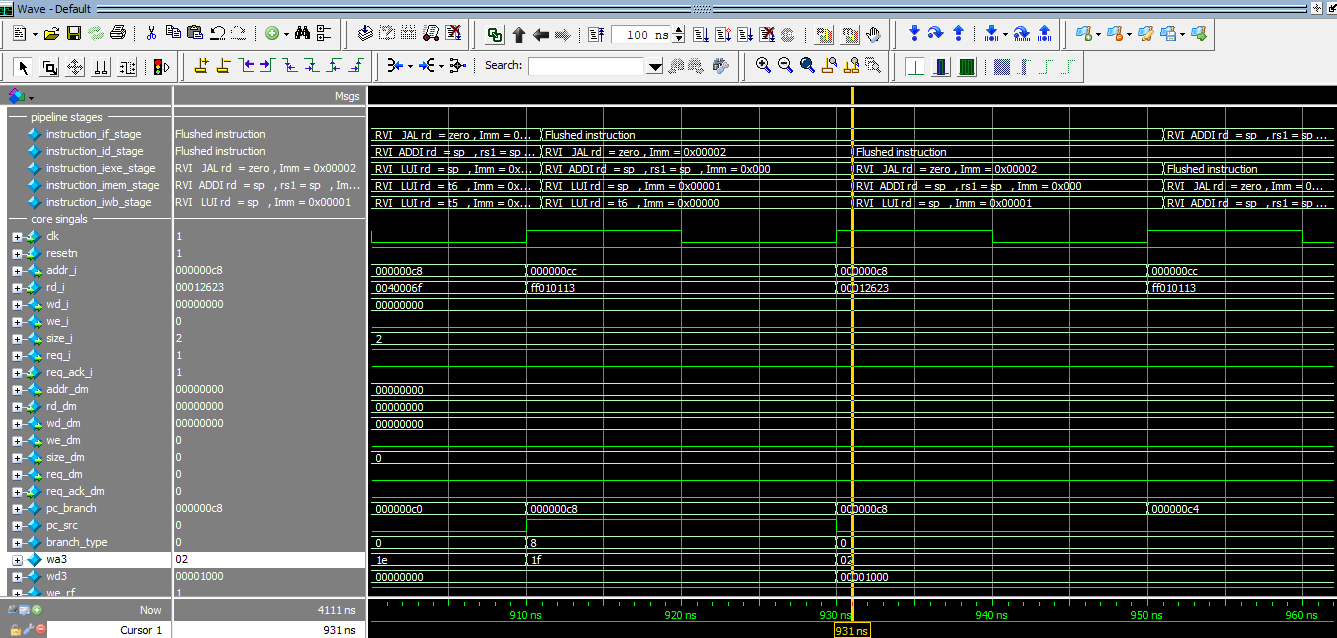

通过显示可执行指令将字符串变量添加到波形中。 使用这些字符串变量,开发人员可以在管道的所有阶段跟踪控制信号的正确设置。

波形图寄存器文件的初始化:

更改sp值:

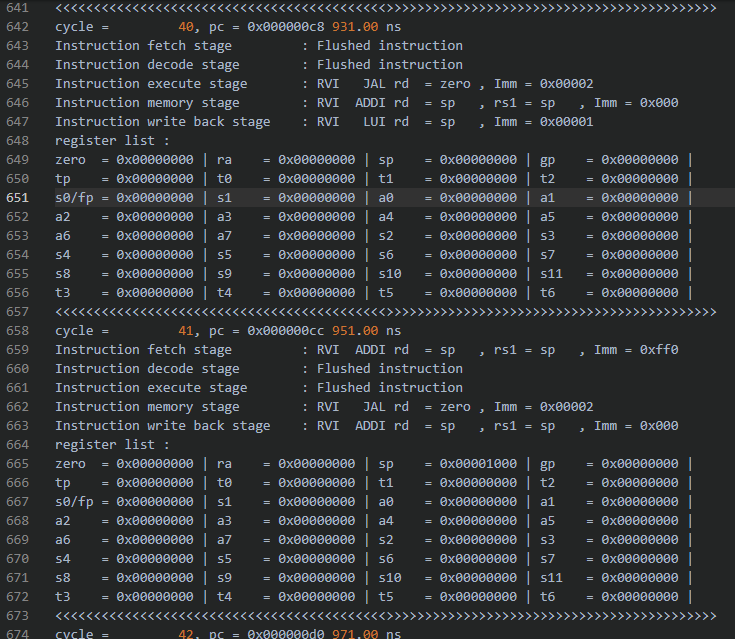

添加了在文本文件中写入有关内核状态的调试信息的功能。 寄存器文件的状态以表格形式显示,并且还指示内核当前执行的一条或多条指令。 它是2分的模拟,但允许对接收到的信息进行更多操作。

文字档寄存器文件的初始化:

更改sp值:

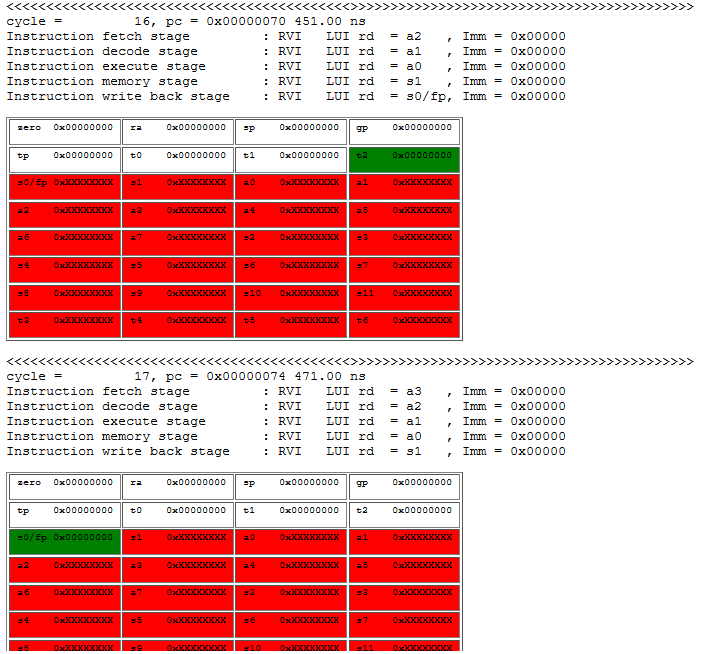

添加了在HTML文件中编写有关内核状态的调试信息的功能。 寄存器文件的状态以表格形式显示,并带有有关更改单元格值的注释,并显示内核当前正在执行的指令。 它与第2段和第4段类似,但是除了它们之外,它还允许您方便地指示数据更改。 如下图所示,如果未定义寄存器值,则寄存器以红色突出显示(寄存器s0 / fp-t6)。 在周期17上,寄存器s0 / fp的值更改,并且该单元以绿色突出显示。

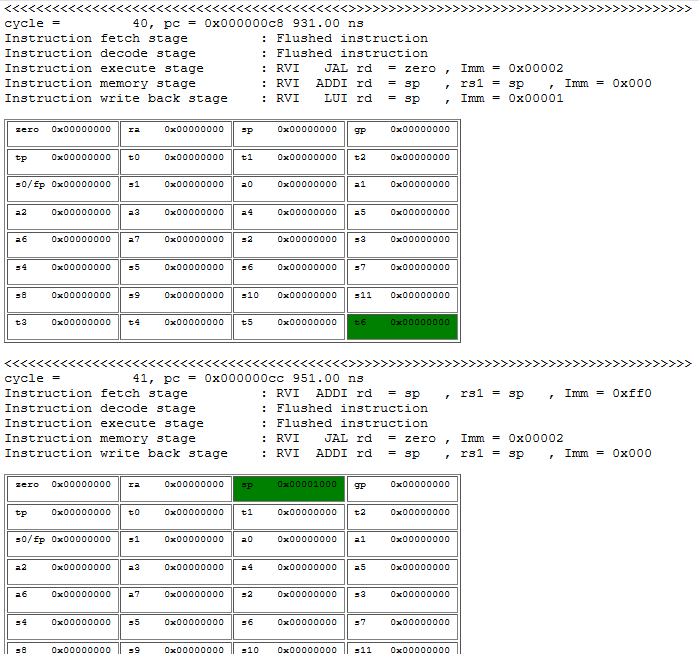

在周期41上,值0x00010000被加载到sp寄存器中。

HTML文件寄存器文件的初始化:

更改sp值:

内核分支比较:当前支持的用于不同分支的内核指令:

支持的外围设备:

编写程序支持的语言:

内核所需的FPGA资源(nf_cpu):

EP4CE22F17C6(de0_nano):

10M50DAF484C7G(de10_lite):

项目开发。

计划将来做什么:

- 添加所有RV32I指令(在描述阶段);

- 进行调试;

- 添加一个DMA(DMA)控制器;

- 增加对其他轮胎AXI,Avalon,叉骨的支持;

- 添加缓存(cache)内存;

- 集成各种外围设备(SPI,TWI(I2C),以太网(10 base-t));

- 添加中断控制器;

- 将不同版本移植到其他调试板;

- 添加其他方法以增加内核的可见性;

- 运行RTOS,例如zephyr 。

也接受有关内核开发的建议。

链接到存储库: nanoFOX 。