在有关航空航天或电子学的有关哈布雷的每隔两个主题中,都会出现辐射抗性的话题。 关于防辐射元素库的进口替代的话题贯穿于有关国内太空探索的消息,但与此同时,埃隆·马斯克(Elon Musk)使用便宜的常规芯片并为此感到自豪。 Bereshit的以色列人使用了辐射处理器,并为此感到自豪。 原则上,俄罗斯的微电子产业之所以能生存,很大程度上是因为有相关要求的国家秩序。 定期观察有关如何正确制造卫星的争议,这表明参与者的培训水平通常较低,他们的论点承受着刻板印象,偶然听到的事实和从上下文中摘取的知识,这已经过时了。 我认为不再可能阅读这篇文章,因此,亲爱的分析师,请在您的沙发上放松一下,我将开始一个简短(非常重要)的故事,讲述关于集成电路的耐辐射性的最普遍误解。

图1.关于宇宙辐射和易碎地球的必不可少的美丽图画。

图1.关于宇宙辐射和易碎地球的必不可少的美丽图画。在近太空争端中使用的最受欢迎的抗辐射论文看起来像这样:

- 不需要辐射状芯片。 Kubsat可以在普通计算机上完美飞行,在ISS上是普通的联想笔记本电脑,在Dragon中有普通的微电路,甚至Orion的NASA也提供了普通的微电路!

- 很有可能在卫星上放置很旧的微电路,一直到“松散的碎屑”,那里并不需要很严格的性能。 但是没有喜悦,无处可走,因此飞上了垃圾。

- 补充上一篇文章的理论:从根本上说,在低设计标准下根本无法实现稳定的微电路,因此使用经过时间考验的组件不仅是合理的,而且也是必要的。

- 为了使微电路具有抗辐射性,使用“绝缘体上的硅”或“蓝宝石上的硅”技术制造微电路是必要且充分的。

- 所有的“军用”微电路都是抗辐射的,所有的防辐射微电路都是“军事”的。

如您所见,其中一些论点直接相互矛盾-这通常是有争议的主题,或者是产生深远错误结论的原因。

您需要从一个重要的免责声明开始对话:抗辐射性不是世界的中心,而是唯一适合在太空或其他侵略性环境芯片中使用的质量。 长期以来,抗辐射性只是其中一项要求,包括可靠性,扩展的温度范围,抗静电放电性,抗振性以及对所有上述参数的可靠确认,即长期且昂贵的认证。 重要的是,所有可能无法使芯片发挥出全部所需使用寿命的因素都非常重要,并且大多数抗辐射芯片的应用都暗示着无法维修或更换。 另一方面,如果其中一个参数出了问题,那么最终产品的设计者通常可以找到一种方法来解决该限制:将对壁厚的辐射剂量最敏感的芯片放在芯片上,监视易受晶闸管效应影响的芯片电流消耗,并在必要时重置电源,或将温度范围狭窄的芯片恒温。 或找不到它,解决任务的唯一方法是订购新的耐ASIC雷达。

记住,专用系统的开发人员与任何其他开发人员都是同一个人,这也很有用。 他们中的许多人还喜欢在昨天的截止日期之前为硬壳拐杖编写代码,并使用功能更强大的硬件,使其能够正常工作。 如果经过适当的认证,有些人会使用Arduino。 而且,当然,为专用系统的开发人员和微电路的开发人员设置任务的人很少会对可靠性,性能和抗欢乐性提出要求。 因此,仍然需要有关卫星的现代设计标准-我想要大量的DRAM,多核处理器和最新的FPGA。 上面我已经提到过,至少可以部分避免不良的抗辐射性和其他潜在问题的后果,因此在很大程度上缺乏有关芯片商业状态的确切数据需要避免的数据,这在很大程度上阻止了开发人员利用所有这些功能。

辐射效应

“抗辐射性”和“抗辐射微电路”的概念非常简化。 实际上,有许多不同的电离辐射源,它们可以以不同的方式影响电子设备的功能。 因此,对于不同的应用,必须具有对不同影响因素和不同暴露水平的抵抗力,因此在分析切尔诺贝利的障碍物时,绝对不需要设计用于低地球轨道的“稳定”微电路正常工作。

电离辐射称为电离,因为在制动进入的粒子期间,物质体积中的能量释放会将物质电离。 每种材料都有其自身的能量,对于电离和创建电子-空穴对来说是必需的。 对于硅,这是3.6 eV,对于其氧化物-17 eV,对于砷化镓-4.8 eV。 同样,进入的粒子可能不会离子化原子,而是将其“移动”到晶格中的正确位置(在硅中,这需要21 eV才能转移到原子上)。 在物质中产生的电子-空穴对可能会对电气和物理特性以及电路的行为产生不同的影响。 辐射效应可分为四大类:总吸收剂量的效应,剂量率的效应,单个粒子进入所引起的效应以及位移效应。 这种分离在某种程度上是任意的:例如,用重离子流照射会产生单一影响,也会导致一组总吸收剂量。

剂量效应辐射的总吸收剂量以弧度为单位,表示吸收辐射的物质。 1 rad = 0.01 J / kg,即单位质量的物质释放的能量。 较不常用的是灰色的度量单位,等于100 rad(或1 J / kg)。 重要的是要了解,对于相同数量的辐射源释放的电离粒子,不同物质中的吸收剂量将有所不同(这是暴露剂量)。 在硅微电路的情况下,所需的材料是氧化硅,因为对其的影响(而不是对硅的影响)主要影响电路的电特性,因为常温下SiO2中空穴的迁移率很小,以至于它们积聚在氧化物中,从而形成内置正电荷。 商用微电路的典型剂量电阻水平在5-100 crad(Si)的范围内,根据微电路的用途,客户要求的辐射电阻水平从30 crad(Si)开始,大约在1 Grad(Si)左右。 对人类的致死剂量约为6灰。

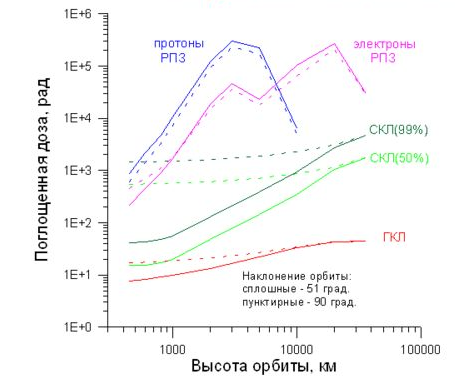

图2.在各种圆形轨道上为保护1 g / cm ^ 2而在10年内的总吸收剂量的一组计算示例。 来源-N.V. 库兹涅佐夫,“航天器近地轨道和行星际轨道的辐射危害”。

图2.在各种圆形轨道上为保护1 g / cm ^ 2而在10年内的总吸收剂量的一组计算示例。 来源-N.V. 库兹涅佐夫,“航天器近地轨道和行星际轨道的辐射危害”。全剂量效应与该正电荷在电介质中的积累有关,并以几种主要方式在CMOS方案中得到体现:

- 由于栅极电介质中正电荷的积累和晶体管沟道中电场的变化而引起的晶体管阈值电压的偏移。 对于n沟道晶体管,阈值通常减小(但是相关性可以是非单调的),而对于p沟道晶体管,阈值通常增大,并且偏移值与栅极氧化物的厚度相关,即与设计标准相关。 具有粗略设计标准的电路中的晶体管阈值可能会更改,从而导致功能故障(n沟道晶体管停止关闭,p沟道晶体管打开); 在亚微米技术中,这种影响并不那么重要,但是在模拟电路中,它会带来很多麻烦。

- 发生不受控制的泄漏电流。 它可以从晶体管的源极流到其自己的漏极或相邻的晶体管。 泄漏的原因是正电荷的积累,但不是在栅极绝缘体中,而是在厚的绝缘材料中。 实际上,寄生晶体管平行于主晶体管形成,其栅极电压由辐射剂量控制。 这种影响的表现取决于从栅极绝缘体到绝缘体的过渡的几何形状特征,也就是说,很大程度上取决于特定的技术而不是设计标准。

- 由于分散了电荷载流子的缺陷的积累,导致电荷载流子的迁移率降低。 该因素对硅上的亚微米数字电路的影响很小,但对于功率晶体管而言,包括复杂的半导体(氮化镓和碳化硅),这一点更为重要。

- 噪声边缘晶体管造成的噪声增加1 / f。 这对于模拟和射频电路很重要。 当剩余剂量效应的影响减小时,该效应的值随着设计标准的降低而增加。

在双极方案中,主要剂量效应是由于在硅与钝化氧化物的界面处从发射极到基极的泄漏而引起的基极电流增加引起的增益下降。 双极晶体管的另一个特定剂量效应是,它们不仅可以(不必)响应累积的剂量水平,而且还可以响应其收集速率-累积的剂量越慢,电阻越差。 这种效应被称为ELDRS(增强的低剂量率敏感性),它不仅使双极电路而且还使CMOS电路极大地复杂化并增加了测试成本-因为它们有时还具有双极晶体管,并且比起所有人更容易进行统一测试弄清楚ELDRS可能在哪里,何处不在。

剂量率与剂量率有关的另一部分影响是超快剂量设定,在该剂量设定下,微电路中产生了如此多的电子-空穴对,以至于它们没有时间重新结合,并且巨大的电荷被引入到芯片中,在充电期间,该电荷通过接地线和电源线溶解大量时间-电路停止工作的时间。 该时间称为“工作时间损失”,是微电路或器件抵抗这种影响的主要特征。 另外,引入微电路的大量电荷会严重改变连接到地面和电源的区域的电势-这可能导致晶闸管效应的出现。

这是高剂量率的影响-出于抵抗的缘故,最初开发了“蓝宝石上的硅”和“绝缘体上的硅”技术,因为减少引入电路的电荷的唯一方法是将微电路的有源区与衬底的体积分开,而不是从基材上带走电荷以参与该过程。 为什么这些影响很重要? 短时间内的高剂量率是核爆炸的典型结果。

单一效果单一作用与长时间暴露于辐射无关,但与单个电离粒子的可测量作用有关。 它们可以分为两大类:

- 无损。 其中包括各种存储元件(高速缓存,寄存器文件,FPGA配置存储器等)中的故障,组合逻辑和模拟电路中的瞬变。 这种效果的主要特征-它们不会导致芯片的物理损坏,并且可以是固定的软件或硬件。 而且,瞬变会在一段时间后自行校正(问题是它有多大)。 存储器阵列中的故障具有主要的实际意义,这仅仅是因为在现代微电子系统中,由于大量的存储器,它们占所有故障的绝大部分。

- 破坏性的。 这些包括晶闸管效应和各种但幸运的是,罕见的效应,例如刺穿晶体管的栅极或雪崩烧毁。 它们的显着特征是它们不可逆地破坏芯片元件。 在晶闸管效应的情况下,如果快速复位电源,通常可以(但不总是如此!)保存芯片。 破坏性影响严重威胁某些类型的闪存以及具有高电压和高电流密度的设备,其中最重要的是电源开关。

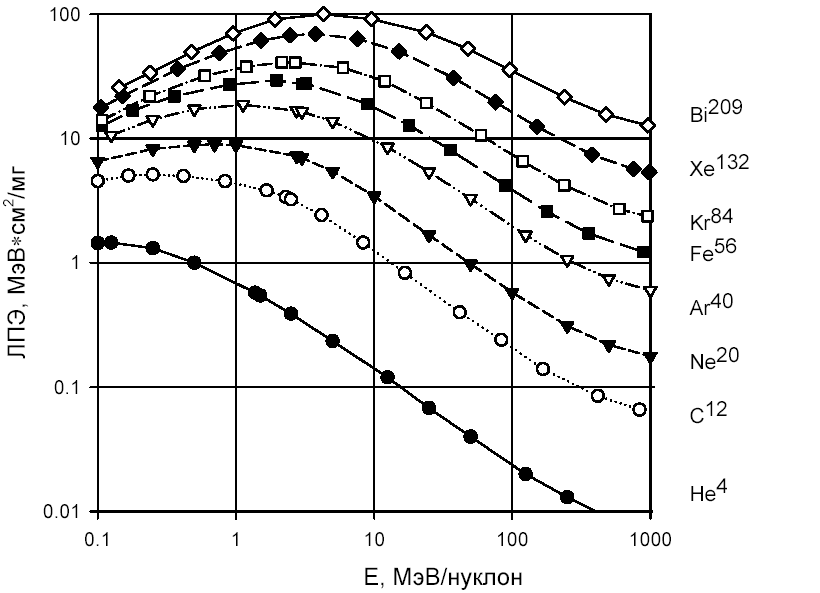

电离粒子的比能产率称为“线性能量转移”(LET),以MeV度量,以单位材料中粒子跨度的单位长度,材料的单位密度转移,即(MeV * cm ^ 3)/(mg * cm)或(MeV * cm ^ 2)/毫克。 LET非线性地和非单调地依赖于粒子能量,并且与平均自由程互连,对于微电子相关的粒子和材料,平均自由程的范围从数百纳米到数百毫米。

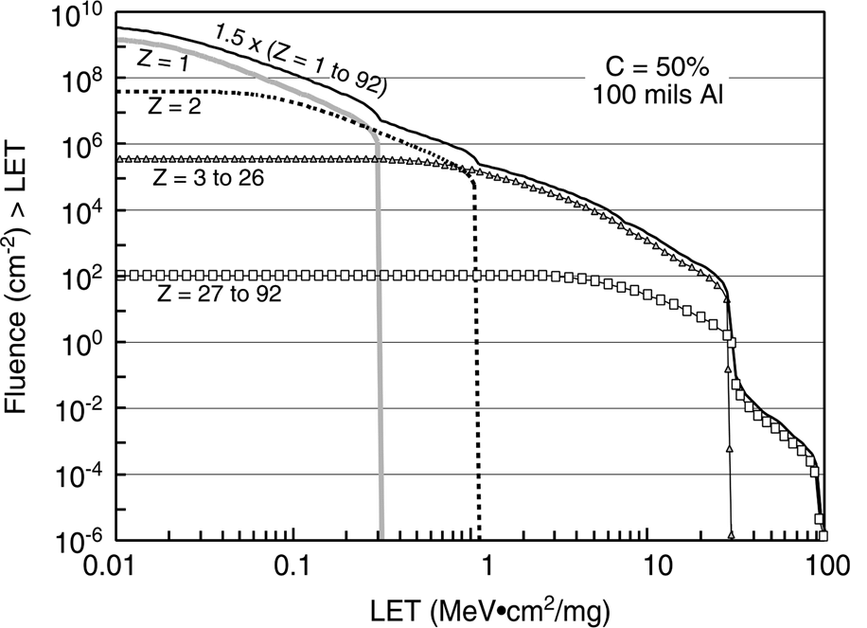

随着LET的增加,在空间中发现的粒子数量会减少(请参见图4)。 重要值是30(对应于铁离子)和60或80(在此之后,该事件的可能性可以忽略不计)。 另外,一个重要的数字是15 MeV * cm ^ 2 /(mg)-这是质子或中子进入硅时核反应产物可能具有的最大LET。 质子是太阳辐射的主要类型之一,尽管其自身的LET小(十分之一单位),但由于核反应和二次电离,它们具有显着的作用。 二次电离可以直接在活性区域中发生,也可以是质子进入某种原子数较大的材料(例如钨或钽)的原子的结果。 重元素积极地用于现代微电子技术中,例如,形成从硅到第一金属化层的接触。 二次电离也是不需要将芯片包装在引线盒中以提高抗辐射性的原因。

图3. LET对不同类型颗粒的能量依赖性。

图3. LET对不同类型颗粒的能量依赖性。值得一提的是,氦原子核(α粒子)值得关注-不仅因为它们的太阳辐射成分很多,而且因为在日常生活中可以找到很多α辐射源。

图4.根据Xapsos等人的论文,“累积的太阳重离子能量和线性能量转移谱模型”,IEEE TNS,第1卷,在两年的轨道飞行中,不同类型粒子的数量比较。 5号 6.,2007年

图4.根据Xapsos等人的论文,“累积的太阳重离子能量和线性能量转移谱模型”,IEEE TNS,第1卷,在两年的轨道飞行中,不同类型粒子的数量比较。 5号 6.,2007年1、30或60 MeV * cm ^ 2 /(mg)-这是多少? 在7 nm技术中,标准存储单元的故障阈值远低于1的统一阈值(180 nm),范围从1到数十。 使用特殊电路可使您将阈值提高到例如几百,但通常更合理的做法是达到15或30个单位的数字,并使用抗噪编码滤除罕见事件的残余。 60单位是通常出现在抗破坏性要求中的数字。

位移效果位移效应是晶格的局部破坏,即原子从其预期位置“敲除”。 破坏晶格所需的能量通常很大,因此大多数通过的粒子都不会引起这种效应。 但是它的原因可能是质子或中子撞击的核反应,而质子或中子撞击的轨道很多。 这种局部晶格缺陷导致电荷载流子迁移率降低,噪声增加以及其他一些影响。 它们对常规CMOS芯片的影响小于“普通”剂量效应,但在太阳能电池板,光电探测器,功率晶体管以及不具有氧化物的复杂半导体(例如,砷化镓和氮化镓)中占主导地位。 这就解释了它们的高剂量耐受性-它们根本没有导致硅芯片快速降解的作用,而这种作用会变得更弱。 导致偏置效应的辐射量以每平方厘米芯片面积的粒子(通常是质子或中子)为单位进行测量。

因此,在找出了影响辐射的因素的描述之后,现在让我们看一下它们在何处以及以何种组合威胁微电路。

什么啊 在哪 什么时候

图2显示了计算不同轨道上的全剂量组的示例。 接下来,我们需要讨论许多假设-太阳活动,形状,材料和保护层的厚度等,但是总的来说,尽管图片是真空中的典型球形马,但趋势很明显:在不同的轨道上,全剂量的速度可以变化五个数量级。 , , , . , . , — , , , , , the last but not least, .

, , , . , .

-, , . , , — — , , , , - . , .

, — , , , . ; , - , - , , . , .

, , , - , . , . , ; , , Apple A9, 16 TSMC 14 Samsung, , . Trusted Foundry — , - .

« ?» : «, , ». : , . , , - 3DPlus — , , ( ) , .

, . — — “”, .

5. “”.

5. “”., - ( — 500 , — 40 000 , 12 ) . “” — , - , (- ) .

2 (Si) — 5-10 (Si), 10-15 . , , — - , . , , , , , — , .

, , «», «» «» . — , — . Mil-Std-883 ( , ), — , , .. 等

:

1017.2 Neutron irradiation

1019.8 Ionizing radiation (total dose) test procedure

1020.1 Dose rate induced latchup test procedure

1021.3 Dose rate upset testing of digital microcircuits

1023.3 Dose rate response of linear microcircuits. ? . / , , . , «military» ? 是的,是的。

一个例子就是臭名昭著的“ Phobos-soil”的命运,根据官方版本(非常难以证明,但非常方便),它的死亡是由于美军级存储芯片中的一个重电荷粒子击中而造成的,该粒子不能抵抗单个故障。和平原子和其他. , , , . — . , , , . - , — , .

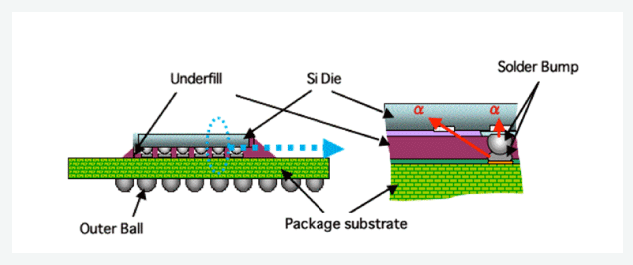

, , , - , , , , , , - — . c BGA- 3D- — .

6. -.

6. -.— - ( , ), . — -, - , , , ( ). , TSMC 2018 IEEE International Reliability Physics Symposium - 7 , - , .

, — . ( , ) , , . — (Si), , . , , — . - , , -, .

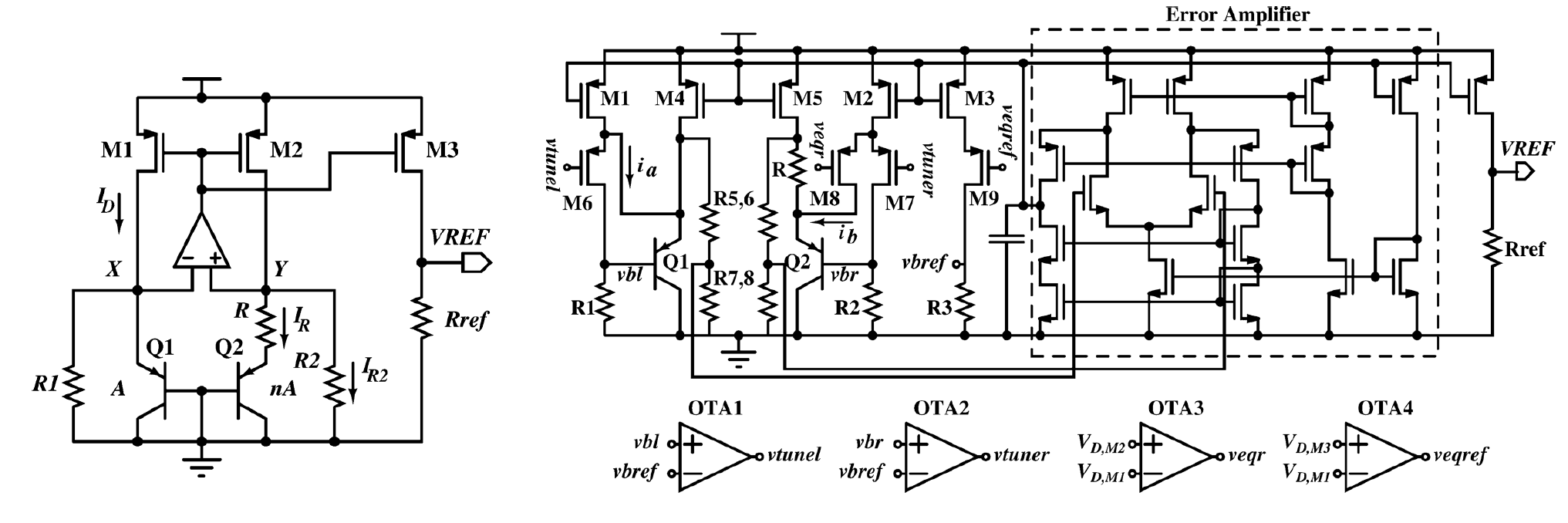

7. . Y. Cao et.al., «A 4.5 MGy TID-Tolerant CMOS Bandgap Reference Circuit Using a Dynamic Base Leakage Compensation Technique», IEEE TNS, Vol.60, N.4, 2013

7. . Y. Cao et.al., «A 4.5 MGy TID-Tolerant CMOS Bandgap Reference Circuit Using a Dynamic Base Leakage Compensation Technique», IEEE TNS, Vol.60, N.4, 2013, , . (), (bandgap voltage reference) — . , ( - -). , , , , 15-20%, - . 1% ( 7 ) 4.5 . , , , , . , , . , . , .

在一个微电子工厂的网站上已经有相当长的时间了,有一种说法是,在低于600 nm的设计标准下无法达到抗辐射性,因为否则“带电粒子会穿透硅”。 碰巧的是,该工厂可用的最低设计标准仅为600 nm。 另一家工厂的一位高级员工在一次采访中表示,制造技术水平低于90 nm的微芯片“在技术上是不可能的”。 再一次,这恰好是巧合的,以至于在该特定工厂中,以低于90 nm的速率进行某些技术处理是不可能的。 这些情况的市场营销原因以及从中获得的直接好处是可以理解的,但是从长远来看,针对广泛受众的此类短语在我看来弊大于利。

此外,定期讨论与根据设计标准制造的微芯片不符合特定限制的粗加工,不受破坏性单一故障(尤其是晶闸管效应)的影响没有任何市场联系,这意味着多年使用悠久的技术不仅合理,而且和必要的。

反之亦然,这些短语指出设计标准低于250 nm的微电路不受晶闸管效应的影响,因为它们具有如此低的工作电压,以致晶闸管根本无法断开。 或者有观点认为实际上问题不在于设计标准,而在于CMOS技术从根本上易受辐射的影响(这已由申请人在70年代进行的测试证实),并且旧的抗辐射芯片是双极/ KNS / GaAs。 而且,由于CMOS技术从根本上来说是不好的,但是所有现代芯片都在上面制造-这就意味着现代芯片在定义上并不稳定,航天学的唯一肯定方法是投资以使人们想起长期废弃的砷化镓(同时在英特尔的商业市场上)获胜)或返回经过时间考验的离散逻辑。 甚至更好-到灯。

容光焕发-意味着古老又落后?公平地说,应该注意的是,在按设计标准执行大约几微米或更多的电路中,通常通常没有晶闸管效应和单一故障。 但是,“通常”在任何情况下均不表示“总是”,其中有一些旧电路对晶闸管效应的抵抗力很低,并且设计标准不能保证任何事情。 仅由于按这种设计标准的开关元件需要大量能量,所以产生了对单个故障的高抵抗力。 同样在正常运行期间,我也希望那些继续使用旧芯片的人们尝试按照74系列的逻辑组装英特尔酷睿处理器,并考虑使用哪种火箭能够将最终的怪物升空。

另一方面,微电子技术还没有被单个处理器激活。 有很多任务不需要或不需要非常小的设计标准,并且500-90 nm的水平已经足够。 直径为200mm的晶圆上的微电路的全球商业市场(这些设计标准为90nm或更高)已经发展了几年,这主要是因为生产设备短缺。 “长期开发的”和全新的微电路都是按照“过时的”设计标准生产的,许多工厂已准备好保证技术过程的长远未来(但不一定是完全不变的)。 因此,有条件的台积电对特定工厂的“落后”一点也不意味着在民用或特殊抵抗领域不可能取得商业上的成功。

与汽车或工业电子产品相比,开发,制造和认证抗辐射电路的高昂成本令制造商更加头疼。 小批量生产(通常不是几百个,甚至几千个)通常会使这种开发的商业化复杂化,因为如果您需要将一百万美元分成一千个芯片(按照180 nm标准,开发成本是相对简单的芯片),那么每千个芯片就需要一千美元。芯片,但仍然需要认证,这很容易导致数百万美元的结果(尤其是如果您在ELDRS上测试CMOS电路)。 如果您需要在短时间内偿还10亿美元? 这就是在5-7 nm的开发成本。 开发和认证的高昂费用导致了这样一个事实,即在世界范围内,大部分防雨电路的开发都由国家直接或间接资助。 这极大地减少了新项目的数量,鼓励更长久,更有创造力的人出售现有产品,并最大限度地利用成熟的IP块。 结果,流行的耐雨水微电路被生产并使用了许多年,从而产生了一种幻想,即所有的耐雨水微电路都是陈旧的。 而且在大多数情况下,客户对此感到满意,因为在可靠性仍然是与性能相关的主要情况下,重用已经证明的解决方案通常是您可以想到的最佳方法,拥有“飞行遗产”是巨大的竞争优势。 这也有助于延长成功开发的活跃生产时间,即使它们已经过时且已经存在替代品也是如此。 此外,即使在大多数情况下,即使安装了引脚对引脚兼容的模拟,也至少需要对设计文档进行核对,并需要进行大量昂贵的测试。 而且这是在不需要开发的情况下,那么当您真的需要重做一些事情以使用新芯片时,情况又如何呢? 当然,在这种情况下,硬件开发人员倾向于整体上使用经过验证的解决方案。

公众认为新发展进入太空的道路漫长而棘手-甚至进入新闻的过程也无济于事,而普通人通常是从科普新闻中了解航天工业的成就。 在2015年,有几条消息,形式为“到达冥王星的新视野卫星,具有与Sony PlayStation相同的处理器”,并且该前缀在新闻发布之时已经有20年的历史了。 出色且非常称职的材料介绍,您什么也不会说。 New Horizons于2006年推出,项目开发于2000年开始-Mongoose-V处理器的首飞之年,也就是说,它是具有现有轨道经验的最新可用处理器。 该处理器的开发在1998年结束,并在1994年开始-与PlayStation发行完全同时。 这是另一个示例:Power750架构处理器于1997年发布用于民用应用,1998年,iMac首次推出了这种处理器。 2001年,抗辐射类似物RAD750的开发完成。 该处理器于2005年首次冲击宇宙,直到好奇号火星车在火星上软着陆后,才在2012年发生。 当然,在15年前,处理器也有一些黄色的头条新闻,但是Curiosity项目的开发始于2003年,也就是在RAD750处理器首飞之前。

尖端尽管有上述所有内容,但目前正在进行空间计算平台开发的设计标准级别是65-45-22 nm。 美国RAD5500芯片组已经开始以45 nm的速度批量生产,欧洲的DAHLIA处理器将于明年在28 nm的速度生产,而比利时IMEC正在积极地设计用于65nm的长期使用的ASIC开发平台。 俄罗斯开发人员也不甘落后-明年的NIISI RAS路线图显示了65纳米抗辐射处理器的输出,有关该主题的出版物谈到了创建开发平台,也就是说,这些设计标准不仅在欧洲而且在俄罗斯都有很大的未来。

即使在这种设计标准水平下,防雨电子产品的开发也不会停止-如果您查看IEEE核科学事务的最新一期,那么您可以在研究20-16-14 nm设计标准的晶体管方面找到足够的工作,为新一代空间微处理器做准备。 在这些设计标准下,开发人员期望有很多新颖有趣的东西:首先,无法制造环形晶体管;其次,FinFET具有完全不同的沟道几何形状和隔离度;其次,还有FDSOI技术,它们也具有足够的特异性。

设计标准的降低当然会影响在其上制造的微电路的抗辐射性,但不一定会恶化。 总的趋势是,随着设计标准的降低,全剂量的效果会降低,而单一效果会提高。 即使对于大剂量,在180 nm或更低设计标准中的阈值电压偏移也以单位或数十毫伏为单位进行测量:栅极氧化物是如此之薄,以至于在其中累积的电荷会隧穿进入沟道而不是累积。 具有STI绝缘的技术中的过渡层足够紧凑,这在许多情况下允许以几十甚至数百个支架(Si)的总剂量实现低泄漏。 而且,如果我们在深亚微米体积技术中应用环形晶体管和保护环,那么我们将立即摆脱所有剂量问题。

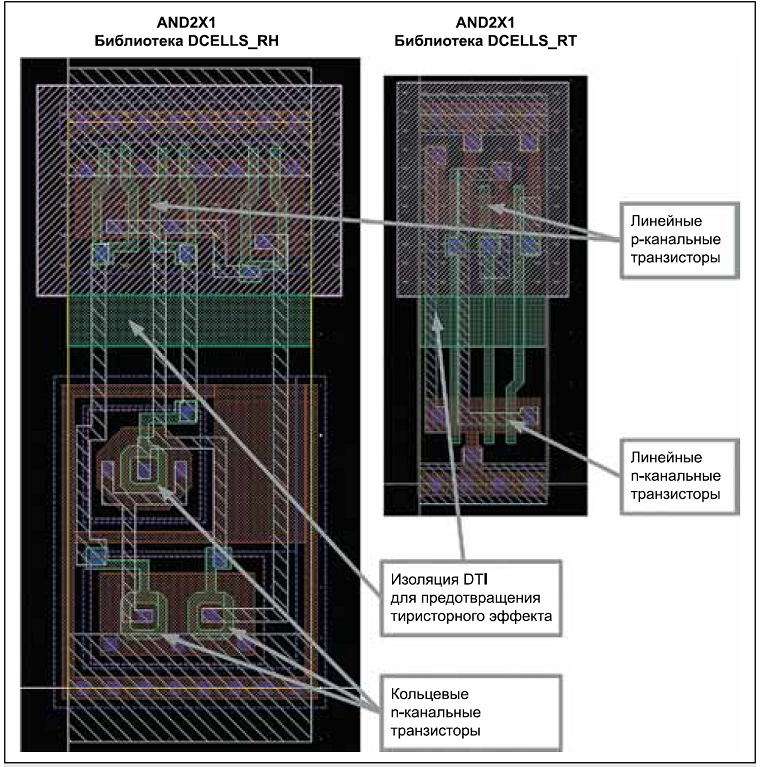

图8. Milander使用SOI BCD技术开发的抗辐射元素示例。

图8. Milander使用SOI BCD技术开发的抗辐射元素示例。图8显示了在不同条件下实现相同AND逻辑元素的两个选项。 在左侧,我们看到了完整的填充-各个保护环中的环形晶体管。 右边是更简单的选择,对于总剂量低:线性晶体管而不是保护环,只有良好的接地接触。 在这两种情况下,n沟道晶体管与p沟道的介电隔离可保护芯片免受晶闸管效应的影响。 在容积技术中,保护环执行此功能。 应当指出的是,对于许多空间应用而言,在50-100 crad(Si)的水平下对全剂量的电阻已经足够,线性晶体管可以很好地做到这一点,而无需为了达到稳定性而显着降低电路的功能参数。

对于单个故障,情况是这样的:当单个粒子进入时,从中收集电荷的区域的近似直径约为1微米,即大于根据深亚微米设计标准制造的存储单元的尺寸。 确实,实验上发现了所谓的多重故障,即一个粒子立即引起多个位的切换。 此外,随着设计标准的降低,切换存储器位所需的能量也降低了,也就是说,与根据更粗糙的设计标准制造的芯片相比,更多的命中导致失败。 包括结构材料中放射性杂质引起的α粒子进入。

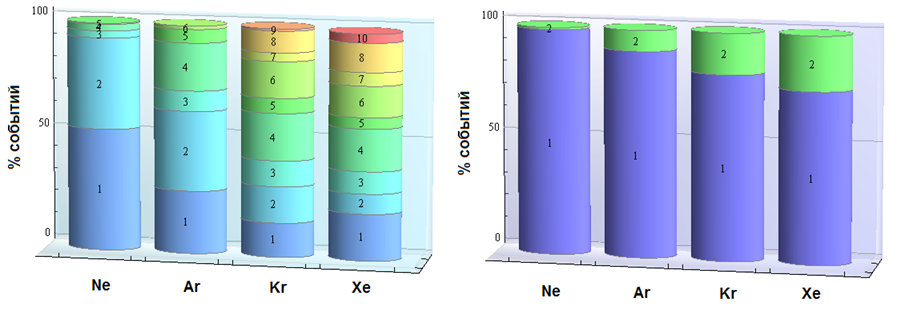

图9.在65 nm设计标准的技术中,两个不同的6T SRAM变体在单个粒子撞击下的故障数量比较。 资料来源-A. Balbekov等人,“在外层空间因素的影响下,对于65 nm CMOS技术的VLSI适用性问题”。

图9.在65 nm设计标准的技术中,两个不同的6T SRAM变体在单个粒子撞击下的故障数量比较。 资料来源-A. Balbekov等人,“在外层空间因素的影响下,对于65 nm CMOS技术的VLSI适用性问题”。图9显示了65 nm体积技术中单个故障的实验数据。 左侧是常用的6T-SRAM。 一击十小故障! 海明码不会保护您免受此侵害。 因此,如果我们谈论的是商用微电路,那么在具有单一故障的粗略设计标准下,一切都将比在薄型故障上有所改善。 至少,它们将保持单独状态,并且实际上可以通过编码进行校正。 但是,如果该芯片是专门为太空应用而设计的,那么开发人员的武器库将拥有大量的架构,电路和拓扑解决方案,这些解决方案可以在提供高性能的同时提供高耐用性。 图的右侧还有6T-SRAM,电路完全相同,但拓扑不同。 消除多个故障,晶闸管效应并增加对全剂量电阻的改进的代价是面积增加了四倍。 听起来不太好,但是没有人说这很容易。 但是,通过设计进行辐射硬化可以使您在任何体积技术上以较小的设计标准达到预定的电阻指标。

为什么要预设? 因为达到不同级别的抵抗力需要使用不同的方法来增加抵抗力,并且对于每种技术和技术任务,所需的方法集也不同。 那为什么不立即应用所有内容以便感觉良好呢? 因为总是由于功能参数(能耗,晶体面积,速度等)的下降而实现抗辐射性,因此它们是第一要务。 这就是为什么我们需要在功能和耐用性方面对技术规范有明确要求的原因。 没错,微电路并不是经常用来解决单个问题,尤其是从根本上来说是稳定的,因为每个可用应用的流通量可能都是几十个。 但是,尽管如此,对要求的充分理解允许,例如,不使用环形晶体管,从而大大增加了面积和电流消耗,最终获得了更具竞争力的产品。

细心的读者可能会注意到“任何体积技术的小型设计标准下的预定义电阻指标”一词中的“体积”一词。 那里不是多余的吗? 众所周知,需要使用“绝缘体上的硅”或“蓝宝石上的硅”技术制作耐辐射微电路。

绝缘体上的硅

长期以来,“绝缘体上的硅”技术已根深蒂固于抗辐射的荣耀。 这种流行的误解的根源可以追溯到上古时期,当时SOI的先驱者,即蓝宝石上的硅被积极地用于军事发展。 怎么了 该技术中的晶体管彼此电隔离,更重要的是与衬底电隔离。 这意味着当芯片短期暴露于高剂量率的辐射下时,辐射感应电荷的收集面积将很小。 反过来,这又大大减少了工作能力丧失的时间-这是原子战所需的工作。 实际上,除了完全绝缘隔离之外,没有其他减少工作时间损失的方法。

神话中的第二个重要部分“ SOI =耐喜悦性”是对晶闸管效应的抵抗力,包括暴露于高剂量率时的抵抗力。 晶闸管效应或“闩锁”几乎是微型芯片和太空设备开发人员的主要头疼,并且让您摆脱它的技术以抗辐射闻名,这也就不足为奇了。 但实际上,情况再次有些复杂。

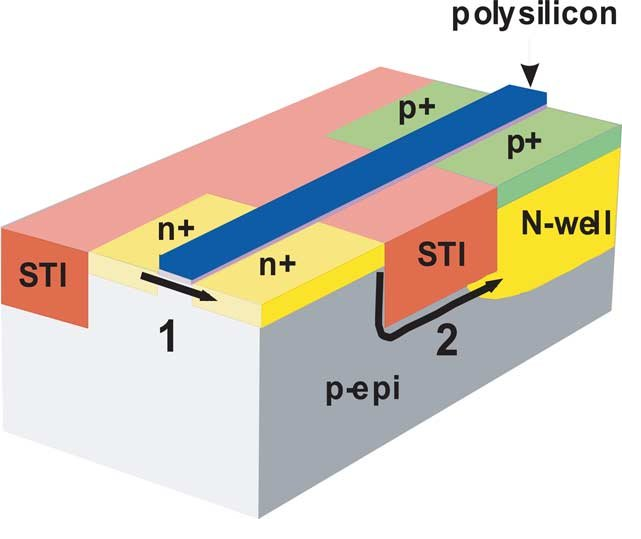

图10.带有寄生晶闸管的体CMOS技术的横截面。

图10.带有寄生晶闸管的体CMOS技术的横截面。晶闸管效应的原因是在体积CMOS技术的元件内部存在的寄生晶闸管结构。 如果电阻Rs和Rw足够大,则这种带晶闸管的结构(当带电粒子进入时)会通过电源打开和短路芯片的接地,这是不好的。 实际的微芯片中这些电阻有多大? 这个问题的答案很简单:与基材或口袋的接触是一个额外的区域,因此他们尝试将其数量最小化。 反过来,这意味着默认情况下,“普通”芯片中的晶闸管效应将更有可能出现。 的确,晶闸管效应不仅可能发生在辐射中,而且还可能发生在例如暴露于静电放电中时,或者甚至只是由于拓扑结构不成功而导致的高温和高电流密度时。 在“普通”应用中,电力和汽车电子制造商面临着晶闸管效应。

在太空系统的很大一部分中,在无法预料的情况下重新启动是完全可以接受的,也就是说,您可以尝试通过将电源控制电路置于电源中来使用容易“闩锁”的芯片,如果超出正常范围,则可以重置电源。 实际上,这是在非常有必要使用高性能的商用微电路的情况下定期进行的,而晶闸管效应的保护芯片(闭锁电流限制器)是一种颇受欢迎的抗辐射产品。 但是这种解决方案有很多局限性。 您可以随时随地重设电源,在执行重要动作的过程中重新启动可以结束长期的任务。 现代微电路的电流消耗可能会根据其工作模式而变化很多倍,也就是说,“什么都没有发生,有闩锁”模式下的电流消耗会比另一种模式下的常规操作要少。 电流限制应设置为什么水平? 也不清楚。 关闭电源和防止芯片损坏所需的时间取决于许多因素,包括特定的芯片。 - , , - - .

, , , . — , . , , , , . , , «».

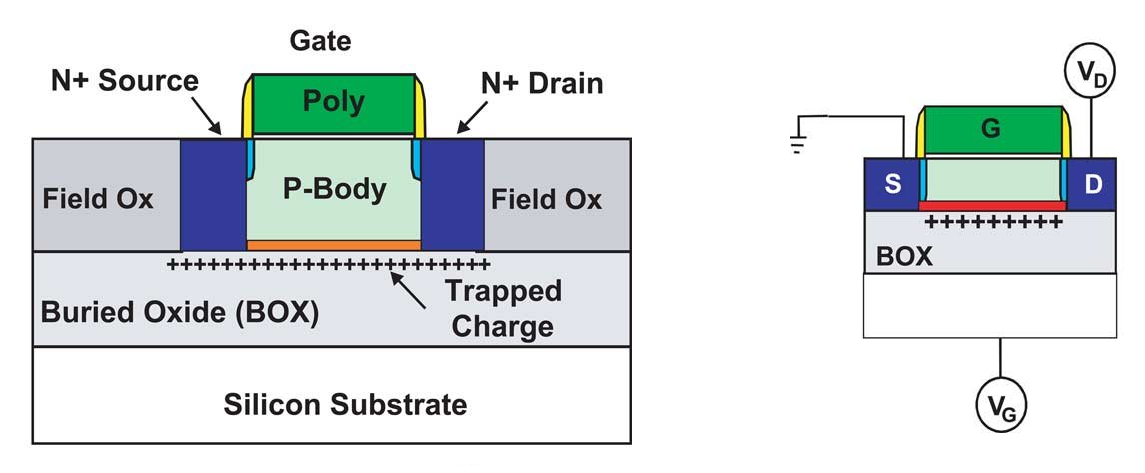

11. - -. — J. Schwank et.al., «Radiation effects in MOS oxides», IEEE TNS, Vol. 55, No. 4, 2008

11. - -. — J. Schwank et.al., «Radiation effects in MOS oxides», IEEE TNS, Vol. 55, No. 4, 2008? , , «», , - . -. — n- , — . ( , ), .

12. .

12. .. , , . «» ( 12), , , «-» — , — , . ( , — ), «» n- . , . , . , , - ?

, , ? , . (FDSOI) 45-28 . , , . , , , ! , , , , , « » , 100 (Si). , . ( ) , .

. , , ( ). , («») , . pn- -, --, , , . 1 *^2/(), . , — /. , -, ( ), -, — , , . - , . 4-8 , , . , , . , , .

« » , « », . , . , «» «» .

结论

, - . . , . , - , . , , . , , , , , — , , , , .