我欢迎大家

遵循先前有关Habré上逻辑分析仪的文章的踪迹,我决定完成我的“基础”工作。

我会从远处开始。

这一切始于10年代初期,当时我在某个业余广播论坛上首次发现了Saleae Logic(以下简称Saleae,我指的是没有滑块的8通道分析仪)。

注意到了。 但是在执行另一个项目的过程中已经13岁了,我发现我确实需要一个带有大缓冲区的逻辑分析仪。 当时可用的示波器和hanteck la-5034不能解决问题。

Saleae及其克隆的主要特点是缺少内置缓冲区-整个流立即被追逐到PC并保存在PC中。 然后可以对其进行分析,解码和导出。 一方面,我们几乎没有观看深度限制(数据可以存储数小时),另一方面,最大采样频率为24 MHz。 然而,在大多数情况下,由于采样的程序性,采样具有明显的“抖动”。

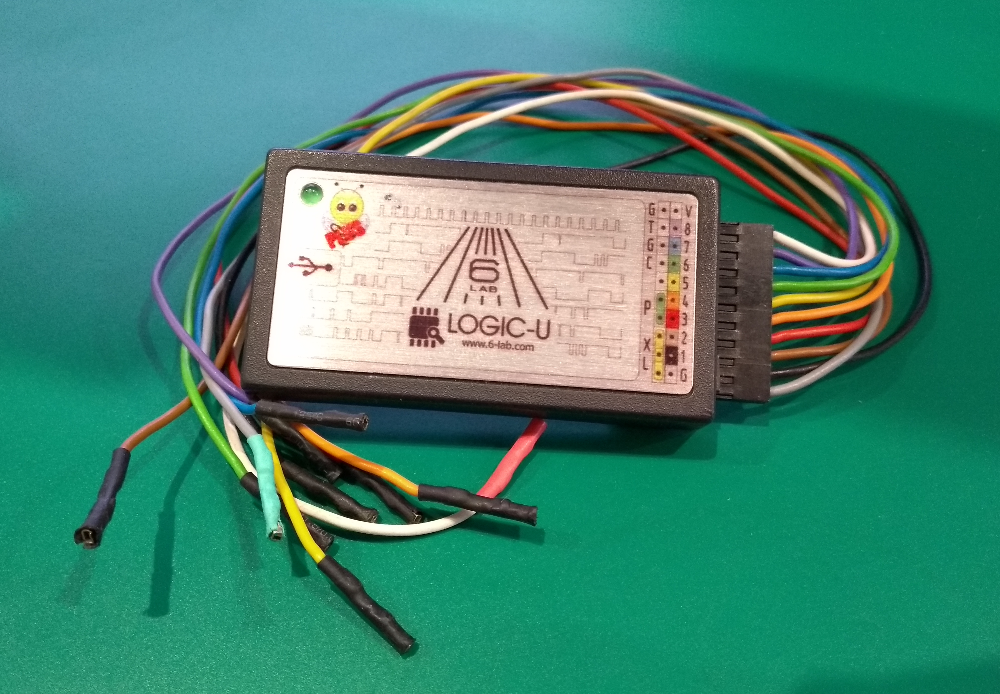

结果,他们很快从哈尔科夫(Kharkov)的6个实验室(现已去世)通过克隆的saleae克隆向我发送了邮件,其中已经内置了两个eeprom,以切换saleae和xbee的类型(这些设备的硬件是相同的,只有vid不同: pid(在eeprom中闪烁)。

因此,您可以使用两个制造商的软件。

从那时起,我开始对Y7C68013A感兴趣,或者说它比FX2短(尽管它比FX2LP更正确)。

这是一个8051兼容的微控制器,具有硬件USB2.0端口和诚实的480Mb / s。

功能包括:16KB的RAM和能够从连接的I2C EEPROM和通过USB下载固件的功能(那里没有内置闪存)。

而且该MK可以假装为USB总线上的任何设备(在响应任何VID:PID的意义上)。

数据表中有关加载过程的一些详细信息

考虑将I2C EEPROM连接到MK的情况。

在这种情况下,将从中分析前8个字节:

如果第一个字节是0xC0(如Saleae克隆固件中一样),则MK会用1-4个字节中指定的VID:PID配置USB端口,并等待通过USB下载固件。 取决于刷新的VID:PID MK可以“成为”另一台设备,至少有人可以将Saleae至少可以Xbee。 很舒服 您可以将EEPROM焊接在堆栈中,并使用跳线进行选择。

但是,如果第一个字节为0xC2,然后从9个字节开始,则MK的固件应存储在EEPROM中,然后将其加载到RAM中并开始执行。

存储格式类似于英特尔的HEX:

也就是说,固件分为多个块,分别加载到内存的不同部分。 因此,没有必要存储空白区域。

现在,我们正在顺利接近文章DreamSourseLab的主要特征。

我不会重述整个故事(我不太了解,也没有深刻的见识) 这三名工程师通过众筹(几乎)看到了逻辑梦想分析器的项目。

他们做了什么。

他们在FX2上增加了便宜的plisina-Spartan 6(可能在Saleae上进行了间谍)。

并且这一次是16个通道,这些是清晰的采样点,这是打包单个位的能力(两条线的采样率可以比8高4倍,主要是保持在USB带宽之内)。 这是一个以高频率(400 MHz / 4通道,200 MHz / 8通道,100 MHz / 16通道)保存到缓冲区,然后将其缓慢传输到PC的机会。 而且,如果您将sigrok与它最强大的解码协议库结合在一起。 总的来说,该项目被解雇了-每个人都很高兴。 考虑到作者保存了流模式(不保存到内部缓冲区)这一事实,我们得到了一个逻辑上的梦想分析器(嗯,几乎是因为我立即想要32个通道和FX3)。

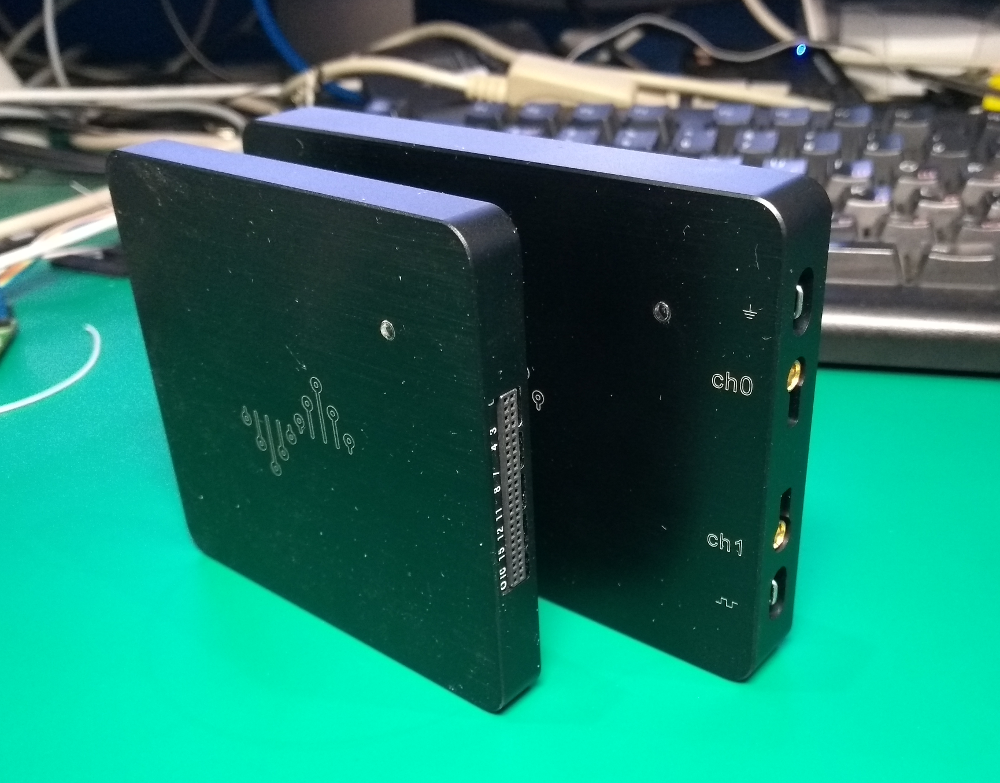

因此出现了DSLogicPro。 带有USB-C连接器的严格黑色铝盒。

然后,工程师开始了业务。 他们发布了名称为DSLogicBase和DSLogicPlus(据我所知是通过中国站点征服世界的盒子)以及DSCope(我们挂了几个8位ADC,现在有了一个两通道示波器)。

好吧,为了严格控制此过程,我们对板布局进行了一些更改。 也就是说,DSLogicPlus和DSLogicPro在电气和功能上是相同的,但SRAM挂在其他引脚上的插头上(在轨迹图中可以清楚地看到)。 我怀疑在其他地方已经进行了改进。

顺便说一下,在用于连接研究信号的电缆方面进行了非常有价值的修改。 如果在Pro中,所有16条线都用一个宽连接器一次连接,则在Plus中,所有电缆都分成4个通道的组,可以分别连接。 好吧,电缆本身是短的,同轴的,并且在切割的地方(同轴被分为单独的信号线和普通线)是一条带过滤器的小围巾。

因此,在17月的春天,我在中国订购了DSLogicBase(不幸的是,我当时不了解我所写的全部内容)。 他们向我发送了所有信息,但是期待着64兆采样缓冲区,我解开了电路板,发现一个空白处。 迅速提高肉chu可返还50%的成本。 然后他开始研究将我的Base变成Plus的问题。 这恰好是Base和Plus之间的区别-存在单独的缓冲区。 Base使用内置在FPGA中的存储器。

在17岁的夏天,在MCC火车上班往返半小时的过程中,我研究了这个问题。 很快就发现区别仅在于密封的SRAM和一对字节的EEPROM固件。

关于DSView / res目录中的内容

在那里,我们有一组带有bin和fw扩展名的文件。

bin-这些是plisina的固件。 它们是通过fx2在启动程序时加载的。

fw是FX2的二进制固件文件。

如果比较所有的fw文件,结果发现它们都只在末尾地址的PID字节不同。

也就是说,所有设备之间的区别仅在于此和插头的固件(如我所说,它是在初始化时加载的)。

将fw与EEPROM中写入的内容进行比较(当然,我立即从分析仪中转储了转储)表明已部署了固件。

如果从EEPROM部署固件,那么(据我所知)它们将匹配(对于0.96版的软件)。

因此,正如已经在集线器上编写的那样,您只需要焊接内存并更改固件中的2个字节(在标头中,然后在固件中)。

以类似的方式,DSCope完成,我们将内存加倍并更改EEPROM中的PID。

还有一点细微差别。

随着新软件版本(0.96-0.99)的发布,添加了受支持的硬件模型,并且更改了这些模型的PID。

所以我得到了这样的平板电脑:

此外,固件的某些功能出现在Pro版本为5的固件中,地址为0x20,而Base和Plus版本为6。最有可能的是,这只是印刷电路板的版本。

顺便说一句,还有另一种提炼方法。 无需EEPROM重新编程。 焊接SRAM就足够了,然后在编译libsigrok4DSL时,对文件libsigrok4DSL / hardware / DSL / dsl.h进行更正:

在描述设备静态结构DSL_profile support_DSLogic []的结构中,

在描述DSLogic PLus和Base的位置,更改PID字段,以便程序认为它具有Base PID 20和Plus PID 21。

319 {0x2A0E, 0x0020, "DreamSourceLab", "DSLogic PLus", NULL, 320 "DSLogicPlus.fw", 321 "DSLogicPlus.bin", 322 "DSLogicPlus.bin", 323 {CAPS_MODE_LOGIC, 324 CAPS_FEATURE_VTH | CAPS_FEATURE_BUF, 325 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 326 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 327 SR_MB(256), 328 0, 329 DSL_BUFFER100x16, 330 0, 331 0, 332 DSL_STREAM20x16, 333 SR_MHZ(1), 334 SR_Mn(1), 335 0, 336 0} 337 }, 338 339 {0x2A0E, 0x0021, "DreamSourceLab", "DSLogic Basic", NULL, 340 "DSLogicBasic.fw", 341 "DSLogicBasic.bin", 342 "DSLogicBasic.bin", 343 {CAPS_MODE_LOGIC, 344 CAPS_FEATURE_VTH, 345 (1 << DSL_STREAM20x16) | (1 << DSL_STREAM25x12) | (1 << DSL_STREAM50x6) | (1 << DSL_STREAM100x3) | 346 (1 << DSL_BUFFER100x16) | (1 << DSL_BUFFER200x8) | (1 << DSL_BUFFER400x4), 347 SR_KB(256), 348 0, 349 DSL_STREAM20x16, 350 0, 351 0, 352 DSL_STREAM20x16, 353 SR_MHZ(1), 354 SR_Mn(1), 355 0, 356 0} 357 },

与此版本的DSView配合使用的分析仪版本将像您拥有真正的Plus一样运行。

同时,我将梦想一堆Spartan6 + FX3 + DSView。