我不知何故不能简短地表达自己的想法。 去年秋天,人们希望更详细地介绍我掌握的PSoC架构,从而产生了一系列有关它的文章。 现在,我参与了为Redd远程调试中心准备硬件的工作,这里已对此进行了介绍,我想以文本形式介绍积累的经验。 我还不确定,但是在我看来,这不仅是一篇文章,而且是一个周期。 首先,这是我将记录开发的开发方法的方法,这些方法可能对使用复杂系统的人有用,并且通常而言,其次,其次,该概念仍然是新概念,尚未完全确立。 也许在讨论文章的过程中,会出现一些评论,从中可以画出一些东西来扩展(甚至改变)它。 因此,我们继续。

详细介绍

我真的不喜欢理论化,宁愿一次布置一些实际的东西。 但是在第一篇文章的开头,没有任何地方进行详细介绍。 在其中,我证明了当前的开发方法是正确的。 一切都围绕一件事:工时是非常昂贵的资源。 而且,问题不仅仅在于为项目分配的条款。 他身体上很贵。 如果花在最终产品的开发上,那么,如果没有它,您将无能为力。 但是,我认为将其用于辅助工作是不好的。 我记得我与一个开发人员发生过争议,该开发人员说,自己制作原型,他会为自己的本地公司省钱。 我提出一个论点,就是他将在制造上花费大约3天。 那是24个工时。 我们用这些时间的薪水,加上“雇主支付的”社会税,以及这些时间的办公室租金。 我们很惊讶地看到侧面的订购板可以降低成本。 但这就是我,我夸大了。 通常,如果可以避免人工成本,则应该避免。

Redd复合体的“固件”的发展是什么? 这是一项辅助工作。 主项目将永远幸福地生活;应该尽可能高效地进行,并进行出色的优化等。 但是,将时间和精力花在开发之后将存档的辅助内容上是浪费的。 正是基于这一原则,才进行了Redd设备的开发。 如果可能的话,所有功能都被实现为标准功能。 SPI,I2C和UART总线在标准FTDI微电路上实现,并通过标准驱动器进行了编程,没有任何多余的装饰。 卷轴的管理以虚拟COM端口的格式实现。 可以对其进行修改,但是至少已完成所有操作,因此不会出现这种需求。 通常,所有标准(如果可能)均以标准方式实施。 从项目到项目,开发人员只需要快速编写典型代码即可让PC访问这些总线。 对于开发微控制器程序的人来说,C ++的开发技术应该是显而易见的(我们将在另一篇文章中讨论一些技术细节)。

但是FPGA在复杂系统中独树一帜。 当需要实施具有高性能要求的任何非标准协议时,会将其添加到系统中。 如果需要这些,则必须为其执行“固件”。 那是关于FPGA编程的,我想专门谈一谈,只是出于相同的目的-减少辅助工具的开发时间。

为了不使读者感到困惑,我将这种想法写成一个框架:

不必在每个项目中都进行FPGA开发。 如果有足够的总线控制器直接连接到中央处理器以与目标设备一起工作,则应使用它们。

FPGA增加了用于执行非标准协议的复杂系统。

复杂的方框图

让我们看一下复杂的框图

电路的底部是“计算器”。 实际上,这是带有Linux的标准PC。 开发人员可以用C,C ++,Python等编写常规程序,这些程序将由计算机执行。 右上方是标准轮胎的标准端口。 左侧是用于标准设备的开关(SPI闪存,SD卡和几个低电流固态继电器,例如,可以模拟按钮按下情况)。 而正好是该部分的中心部分,计划在本系列文章中考虑与之相关的工作。 它的核心是FPGA类FPGA,从中可以引出直线(可用作差分对或普通的非缓冲线),具有可配置逻辑级别的GPIO线以及通过ULPI芯片实现的USB 2.0总线。

继续介绍FPGA编程方法

在开发用于FPGA的高性能控制逻辑时,通常状态机会为His Majesty演奏第一把小提琴。 在机器上可以实现高速但复杂的逻辑。 但是,另一方面,自动机的开发速度比处理器程序要慢,并且自动机的修改是另一个过程。 有些系统可以简化机器的开发和维护。 其中之一甚至是由我们公司开发的,但是,任何一种复杂逻辑的设计过程都不是很快。 当开发的系统成为最终产品时,就可以进行准备,设计好的控制机器并花一些时间实施它。 但正如已经指出的那样,为Redd进行开发是一项辅助工作。 它旨在简化流程,而不是使其复杂化。 因此,决定开发将不是自动的,而是处理器系统。

但是另一方面,在开发硬件时,迄今为止最时尚的选择是采用ARM内核的FPGA。 首先,出于价格原因。 基于Cyclone V SoC的原型板价格适中,但奇怪的是,单独的FPGA要贵得多。 最有可能的是,为了吸引开发人员使用FPGA数据而放弃了原型板的价格,并且这些板是单独出售的。 该系列赛将不得不采取单独的筹码。 但是除此之外,还有一个“第二”。 其次,当我试验Cyclone V SoC时,事实证明该处理器系统并非如此,并且在单次访问端口时效率很高。 批处理-是的,工作很快。 如果以925 MHz处理器内核的时钟频率进行单次访问,则可以以几兆赫兹的频率访问端口。 对于每个人,我建议调用在UART块的FIFO中输入数据的标准功能,该功能检查队列溢出,但是在队列明显为空时调用,即没有任何干扰。 我的工作效率从每秒一百万次提高到每秒五十万次(当然,使用内存的速度是正常的,所有高速缓存都已调整,即使没有检查FIFO是否溢出的功能变体也能更快地工作,只是正在讨论的功能混杂在一起)从端口写入和读取)。 这是FIFO! 实际上,发明了FIFO是为了将数据丢失并忘记! 快速退出! 而且性能不高,在925 MHz的处理器频率下每秒少于一百万次运算...

延迟是罪魁祸首。 处理器核心和设备之间有3个或更多的桥接器。 此外,对端口的访问速度取决于上下文(连续的几条记录会很快执行,但是第一次读取将停止该过程,直到完全卸载缓存的数据为止,由于写入缓冲区已用完,连续的太多记录也将减慢速度)。 最后,检查调试缓冲区中累积的迹线表明,由于复杂的缓存系统,

Cortex A架构可以在不同的时钟周期内执行相同的部分。 总而言之,考虑到所有这些因素(价格,使用设备时的性能下降,设备访问速度的不稳定性,对上下文的总体依赖性),决定不将这种芯片放入复杂设备中。

赛普拉斯PSoC的实验表明,

Cortex M内核可以提供更可预测和可重复的结果,但是这些控制器的逻辑容量和最大工作频率与技术规格不符,因此也将其丢弃。

决定安装廉价的典型Cyclone IV FPGA,并建议使用合成的NIOS II处理器内核。 好吧,如果需要的话,可以使用任何其他方法(自动机器,硬逻辑等)进行开发。

我将单独提及(甚至重点介绍这一段),该复合系统的主处理器是x86(x64)。 是他是系统的中央处理器。 在它上面执行复合体的主要逻辑。 将在下面讨论的处理器系统旨在简单地提供FPGA中“闪存”设备的操作逻辑。 此外,仅当开发人员没有足够的全职模块直接连接到中央处理器时,才出售此设备。

开发和调试“固件”的过程

如果Redd复合体运行的是Linux,则并不意味着应该在此OS中进行开发。 Redd是一个远程执行器,无论使用什么操作系统,都应在您的计算机上进行开发。 拥有Linux的人会更容易,但是熟悉Windows的人(我曾经非常不喜欢WIN 3.1,但是我被迫工作,但是到了WIN95 OSR2的时候,我已经习惯了它,现在对它已经无用了,更容易接受) ,这些可以继续引领其中的发展。

由于我与Linux的友谊未能解决,因此我不会逐步说明如何设置Linux下的环境,但我将只限于一般性的话。 可以使用此操作系统的人就足够了,其余的就足够了。相信我,联系系统管理员会更容易。 最后,我做到了。 但是尽管如此。

您应该下载并安装与开发环境相同版本的Quartus Prime Programmer和Tools。 如果版本不匹配,可能会感到惊讶。 我花了整个晚上来理解这个事实。 因此,只需下载与开发环境相同版本的工具即可。

安装后,输入安装程序的目录bin子目录。 通常,最重要的文件应该是jtagconfig。 如果您在不带参数的情况下运行它(顺便说一句,我一直要求输入./jtagconfig,只有这样),然后将显示系统中可用的程序员和与其连接的FPGA的列表。 应该有一个USB Blaster。 系统引发的第一个问题是访问权限不足以使用USB。 此处介绍了如何不使用sudo来解决它:

radiotech.kz/threads/nastrojka-altera-usb-blaster-v-ubuntu-16-04.1244但是这是显示的设备列表。 现在您应该写:

./jtagconfig --enableremote <password>

之后,服务器可以启动,可以从网络的任何位置进行访问。

一切都会好起来,但是系统防火墙不会让任何人看到此服务器。 在Google上进行的检查显示,每种类型的Linux(其中有很多)都以自己的方式打开防火墙中的端口,因此必须使用许多拼写法令,我希望与管理员联系。

还值得考虑的是,如果jtagd没有在自动运行中注册,那么当您打开远程访问时,将被告知无法设置密码。 为了防止这种情况的发生,必须不是通过jtagconfig本身来启动jtagd,而是在其之前启动。

一般来说,萨满教是萨满教。 让我来解决这个问题:

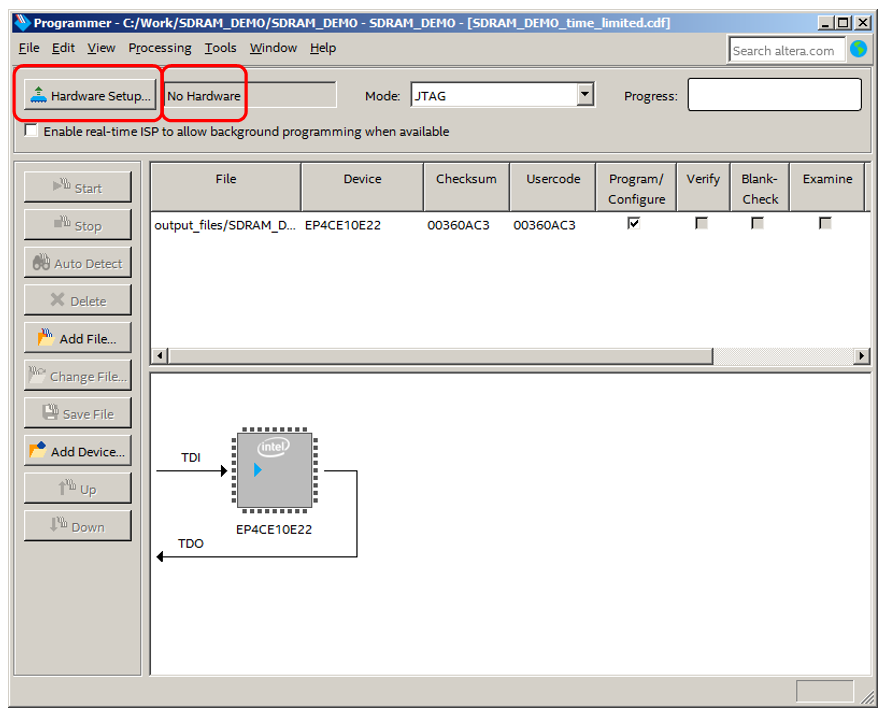

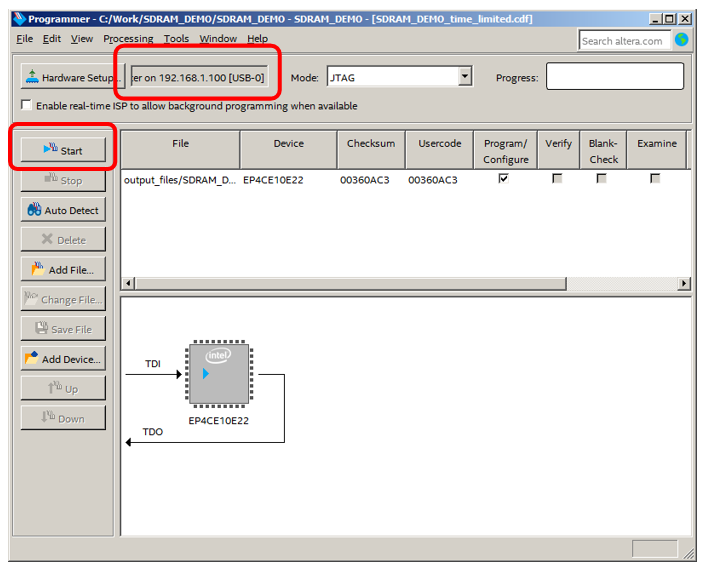

当然,通过GUI界面也有类似的路径,但是批量执行所有操作更合乎逻辑。 因此,我描述了一个批处理版本。 当所有这些内容都已完成(并且系统管理员已经完成)后,我们在计算机上启动编程器,我们看到一条有关设备不足的消息。 单击硬件设置:

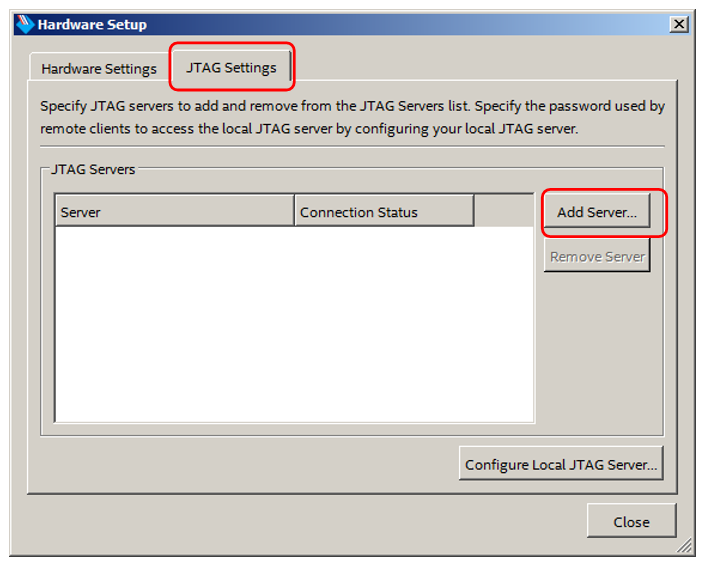

转到“ JTAG设置”选项卡,然后单击“添加服务器”:

我们输入Redd的网络地址(对我来说是192.168.1.100)和密码:

我们确保连接成功。

我花了五个假期来实现这一目标,然后管理员决定了一切。

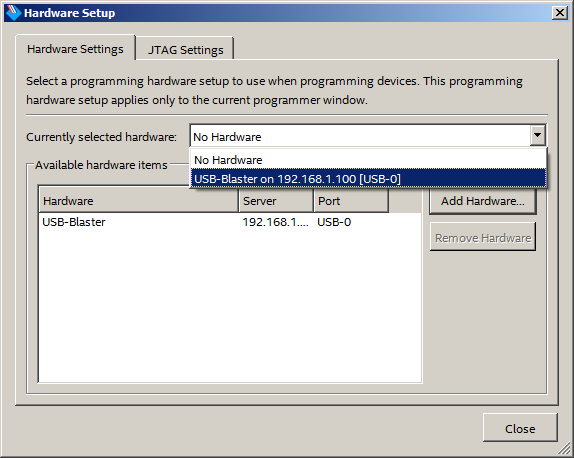

切换到“硬件设置”选项卡,打开下拉列表并在此处选择远程编程器:

一切都可以使用了。 “开始”按钮被解锁。

第一个“固件”

那好 为了使本文具有实际的实用价值,让我们分析使用上述方法制作的最简单的“固件”。 我真正设法实现的最简单的操作是对SDRAM芯片的测试。 这里就这个例子和实践。

有许多业余内核可以支持SDRAM,但是它们都以某种方式很棘手。 掌握所有技巧都是劳力。 我们将尝试使用可插入NIOS II计算系统中的现成解决方案,因此我们将使用标准SDRAM控制器内核。 内核本身在《

嵌入式外围设备IP用户指南》中进行了描述,并且在说明中有很多空间专门用于SDRAM相对于内核时钟的时钟移位。 给出了复杂的理论计算和公式,但是没有特别报道如何做。 该操作可以在

使用Verilog Designs在Altera的DE0板上使用SDRAM的文档中找到。 在分析过程中,我将运用本文档中的知识。

我将在Quartus Prime 17.0的免费版本中进行开发。 我专注于此,因为在组装过程中,他们告诉我,将来

SDRAM控制器的内核将退出免费版本。 如果您的开发环境中已经发生了这种情况,那么没有人会费心下载免费的第17版并将其安装在虚拟机上。 无论您在哪里使用,都可以完成主要工作,带有SDRAM的Redd的固件版本为17。 好吧,那就是如果您使用免费选项。 没人威胁要把它扔掉。 但是我分心了。 创建一个新项目:

我们称它为SDRAM_DEMO。 应该记住这个名字:我将进行超快速开发,因此处理器系统本身应该是顶级的,没有任何Verilog层。 为此,处理器系统的名称必须与项目的名称匹配。 所以记住这一点。

在几步中同意默认值后,我们开始选择晶体。 我们选择在综合大楼中使用的EP4CE10E22C7。

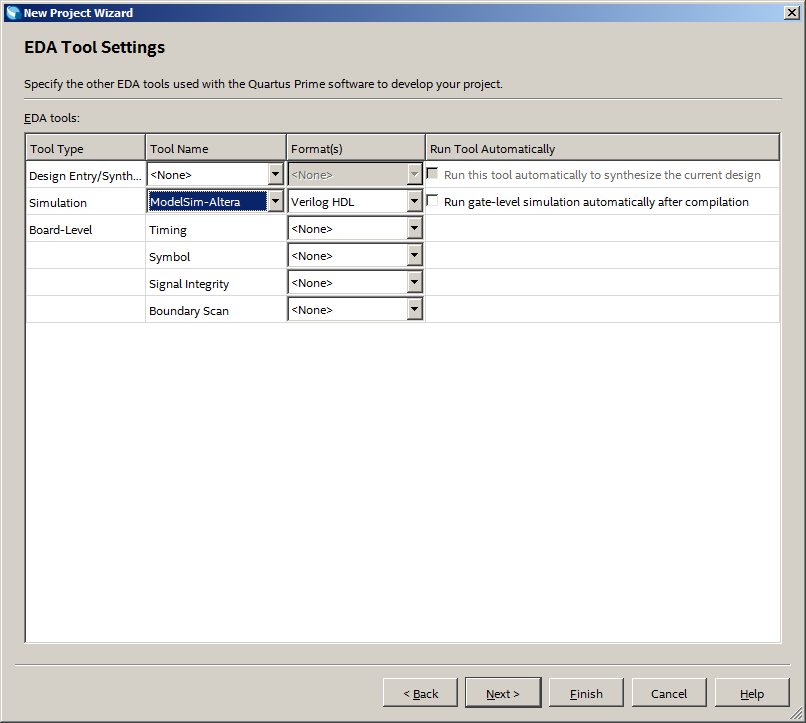

在下一步,出于习惯,我选择在ModelSim-Altera中进行建模。 今天,我们将不建模任何东西,但一切都可以派上用场。 养成这样的习惯并遵循它:

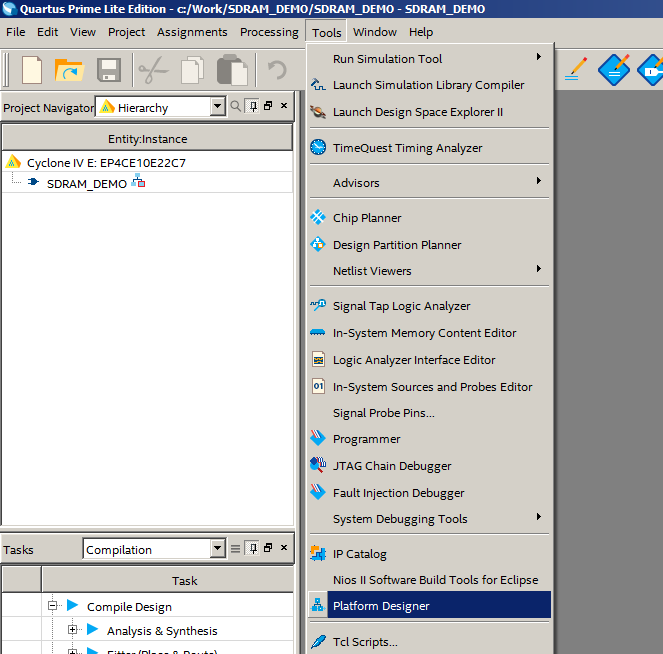

项目已创建。 立即转到处理器系统的创建(工具->平台设计器):

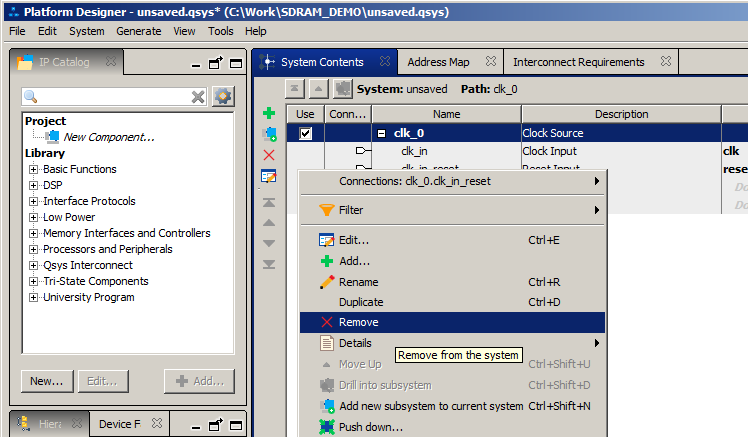

我们创建了一个包含时钟和重置模块的系统:

但是正如我已经提到的,SDRAM内核需要特殊的时钟。 因此,标准模块被无情地丢弃了

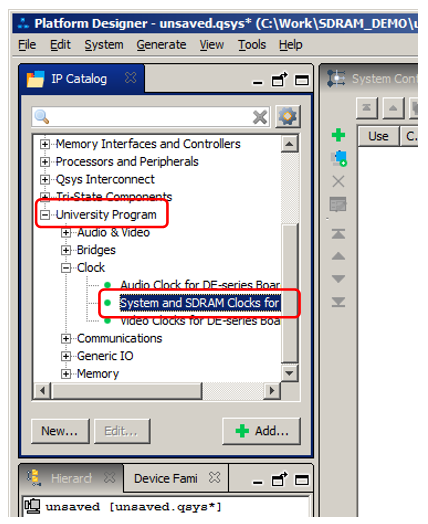

相反,添加用于DE系列板块的University Program-> System和SDRAM Clock:

在属性中,选择DE0-Nano,因为从此面包板获得了SDRAM开关电路的灵感:

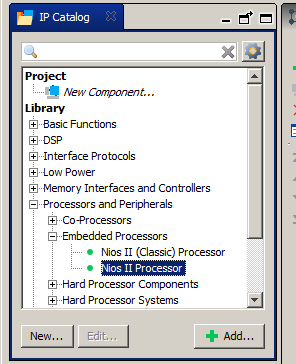

我们开始填充处理器系统。 当然,要添加的第一件事是处理器核心本身。 让它成为处理器和外围设备->嵌入式处理器-> NIOS II处理器。

对于他来说,我们尚未填写任何属性。 即使我们已经形成了一系列错误消息,也只需单击“完成”。 到目前为止,还没有能够消除这些错误的设备。

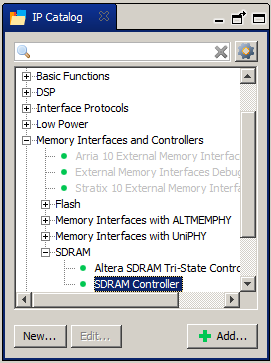

现在添加实际的SDRAM。 内存接口和控制器-> SDRAM-> SDRAM控制器。

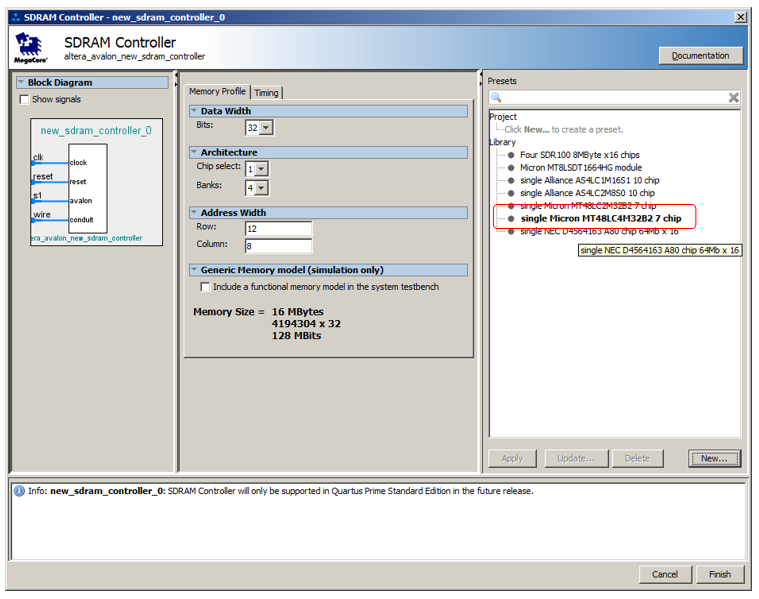

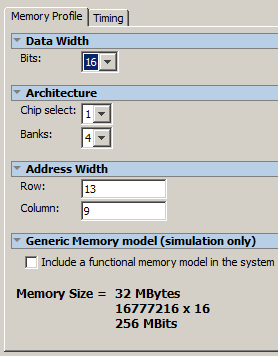

在这里,我们必须坚持填写属性。 从列表中选择最近的组织类似的微电路,然后单击Apppy。 它的属性属于“内存配置文件”字段:

现在,我们将数据总线的宽度更改为16,将地址线的数量更改为13,将列的更改为9。

我尚未调整时间,也许将来会更改此建议。

处理器系统意味着程序。 该程序必须存储在某个地方。 我们将测试SDRAM芯片。 目前,我们不能相信她。 因此,要存储程序,请基于Block RAM FPGA添加内存。 基本功能->片上存储器->片上存储器(RAM或ROM):

卷...好吧,让它成为32 KB。

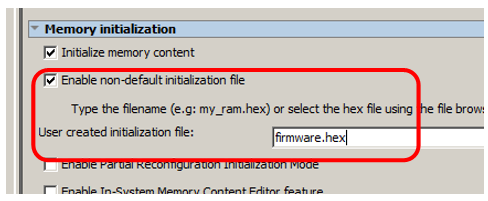

该内存必须从某个地方加载。 为此,请选中“启用非默认初始化文件”框,然后输入一些有意义的文件名。 假设firmware.hex:

这篇文章已经很复杂了,因此我们不会超载。 我们将简单地以PASS / FAIL行的形式输出测试的物理结果(并且通过我最喜欢的JTAG调试,我们将看到逻辑结果)。 为此,请添加GPIO端口。 处理器和外围设备->外围设备-> PIO(并行IO):

在我们设置2位的属性中,我也想选中用于单独控制位的框。 也只是一个习惯。

我们得到了一个带有很多错误的系统:

我们开始消除它们。 首先,我们将中断时钟并重置。 在时钟和复位单元,必须丢弃输入。 为此,有些字段显示“双击导出”:

我们单击,但提供或多或少的简称。

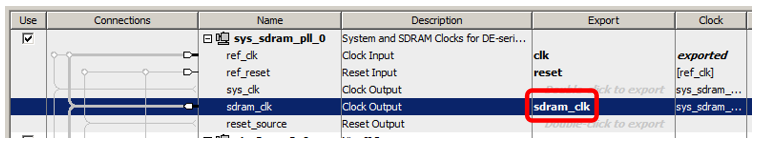

您还需要丢弃SDRAM时钟输出:

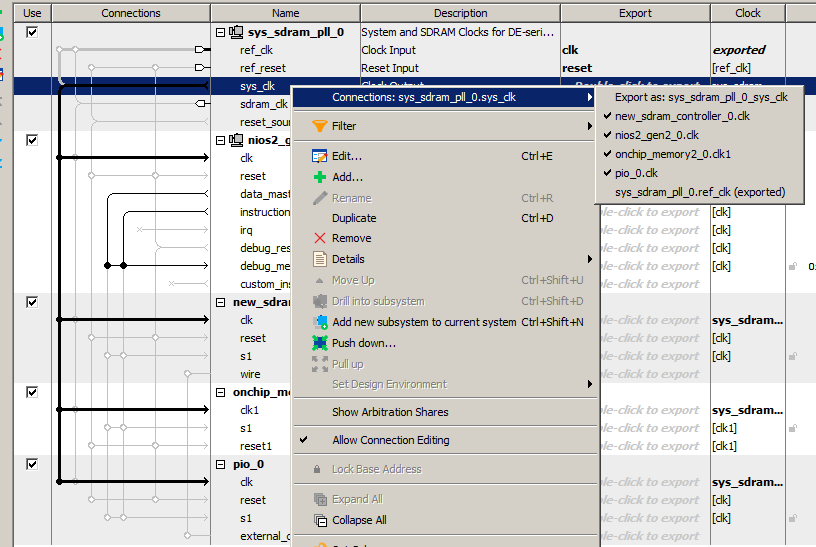

现在,我们将sys_clk分配给所有时钟输入,并将reset_source分配给所有复位线。 您可以用“鼠标”轻触连接相应线的点,或者可以转到相应的出口,按鼠标右键,然后转到下拉菜单中的“连接”子菜单,然后在其中选择连接。

然后,我们将轮胎连接在一起。 我们将Data Master连接到所有设备的所有总线,并将Inctruction Master连接到几乎所有设备。 不需要将其连接到PIO_0总线。 从那里,绝对不会阅读说明。

现在您可以解决地址冲突。 为此,选择菜单项“系统”->“分配基本地址”:

当我们获得地址时,我们也可以分配向量。 为此,请转到处理器核心的属性(指向它,按鼠标右键,然后选择“编辑”菜单项),然后在此处配置Onchip Memory上的向量。 只需在下拉列表中选择这种类型的内存,数字将自己替换。

没有错误了。 但是仍然有两个警告。 我忘了出口SDRAM和PIO线。

正如我们对重置和时钟模块所做的那样,双击所需的支路,并为其指定最短(但可以理解)的名称:

一切,没有更多的错误或警告。 保存系统。 此外,该名称必须与项目的名称一致,以便处理器系统成为项目顶层的元素。 还没有忘记我们所说的吗?

好吧,我们按下最重要的按钮-生成HDL。

一切都创建了处理器部分。 单击完成。 提醒我们,最好将此处理器系统添加到项目中:

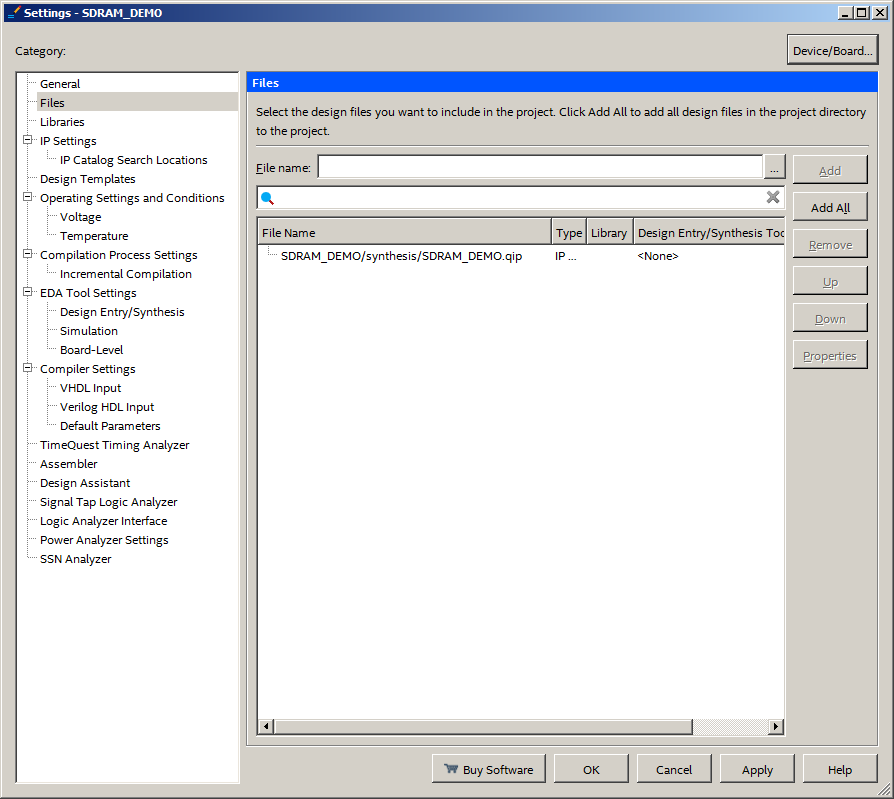

添加:

在那里,使用“添加”按钮,我们得到了以下图片:

SIP文件尚未创建。 是的,在本文的框架中我们不需要它。

h 迈出了第一步。 我们起草项目,以便系统找出项目层次结构和使用的分支。 编译错误并不可怕。 只是在该环境的免费版本中,才创建了仅在连接JTAG适配器时才起作用的内核。 但是在Redd大楼中,它始终是相连的,因为它在同一块板上离婚了,也就是说,我们没有什么可担心的。 因此,我们将忽略这些错误。

现在回到SDRAM内核的描述。 它表示未使用CKE线,并且始终与设备连接。 实际上,在复杂的框架内,FPGA支路不仅昂贵,而且是宝贵的资源。 而且,总是将腿伸到单元中也是很愚蠢的(在DE0-NANO板上也没有离婚)。 会有一个Verilog层,可以在那里剪切相应的链,但是我节省了时间(紧张的笑声,看着已经获得的文档的数量,但是如果不保存,结果可能会更多)。 因此,没有层。 如何成为 转到工作分配编辑器。 就在其中,因为在Pin Planner中,根据描述判断,没有类似的功能。

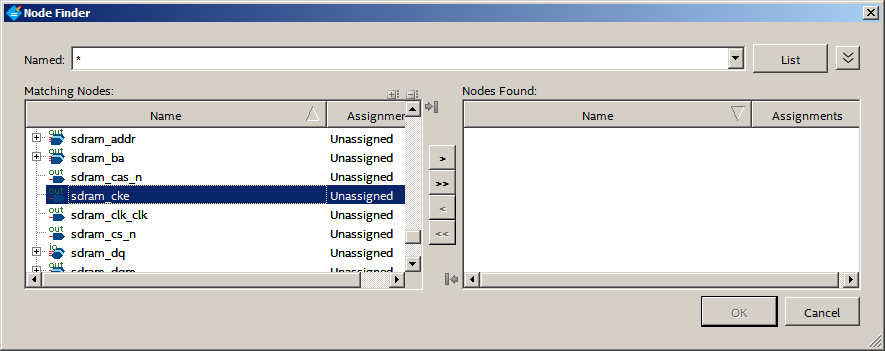

仍然没有线。 好啊 创建一个新的

我们选择以下图标:

在我们设置的搜索系统中,单击“列表”,然后在搜索结果中找到我们的CKE:

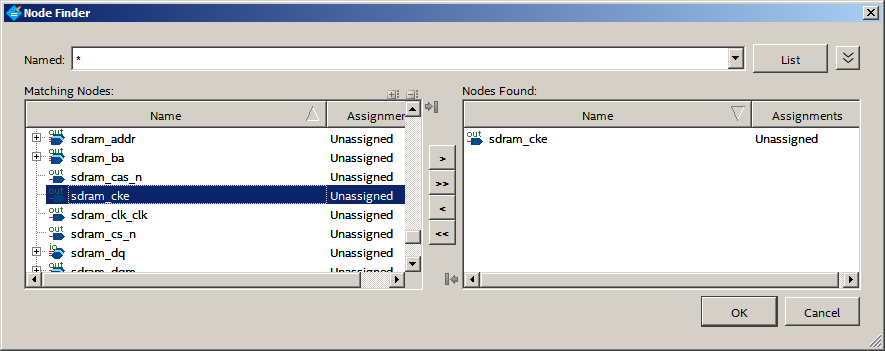

将其添加到右列,单击确定。

我们得到以下列表:

在黄色字段中,单击下拉列表,然后找到虚拟引脚。 我们选择。 黄度移至另一个单元格:

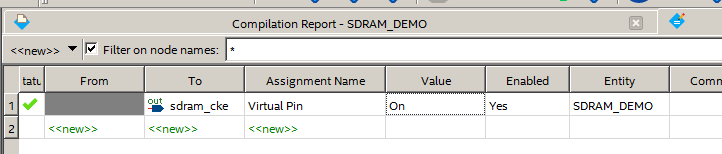

在这里,我们选择开:

所有的黄都消失了。 现在,该链被标记为虚拟链,这意味着它不需要物理分支。 因此,我们不能将其分配给FPGA的物理结论。 关闭作业编辑器,打开引脚计划器。 您可以参考该图指定腿,也可以从* .qsf文件中获取列表,该文件是项目的一部分,我将在本文中附加该列表。

就是这样,关闭Pin Planner,我们执行项目的最终编译。 硬件已经准备就绪,我们将继续开发用于最终处理器系统的软件。 但是这篇文章实在太大了,我们

下次再做。