您有一个梦想:发现自己正在参加考试或在特定的听众面前讲话,突然间您意识到自己根本没有做准备,现在必须即兴创作。 正是在这种情况下,而不是在梦想中,而是在现实生活中,我在莫斯科遇到了五月的假期。我从那里飞往加利福尼亚,为来自领先的莫斯科物理学校的精心挑选的学童进行为期三天的研讨会。 在RUSNANO的主持下,在RUT体育馆(MIIT)中,并有来自MIET,MIREA,MEPhI,MPEI和HSE MIEM的老师在场。

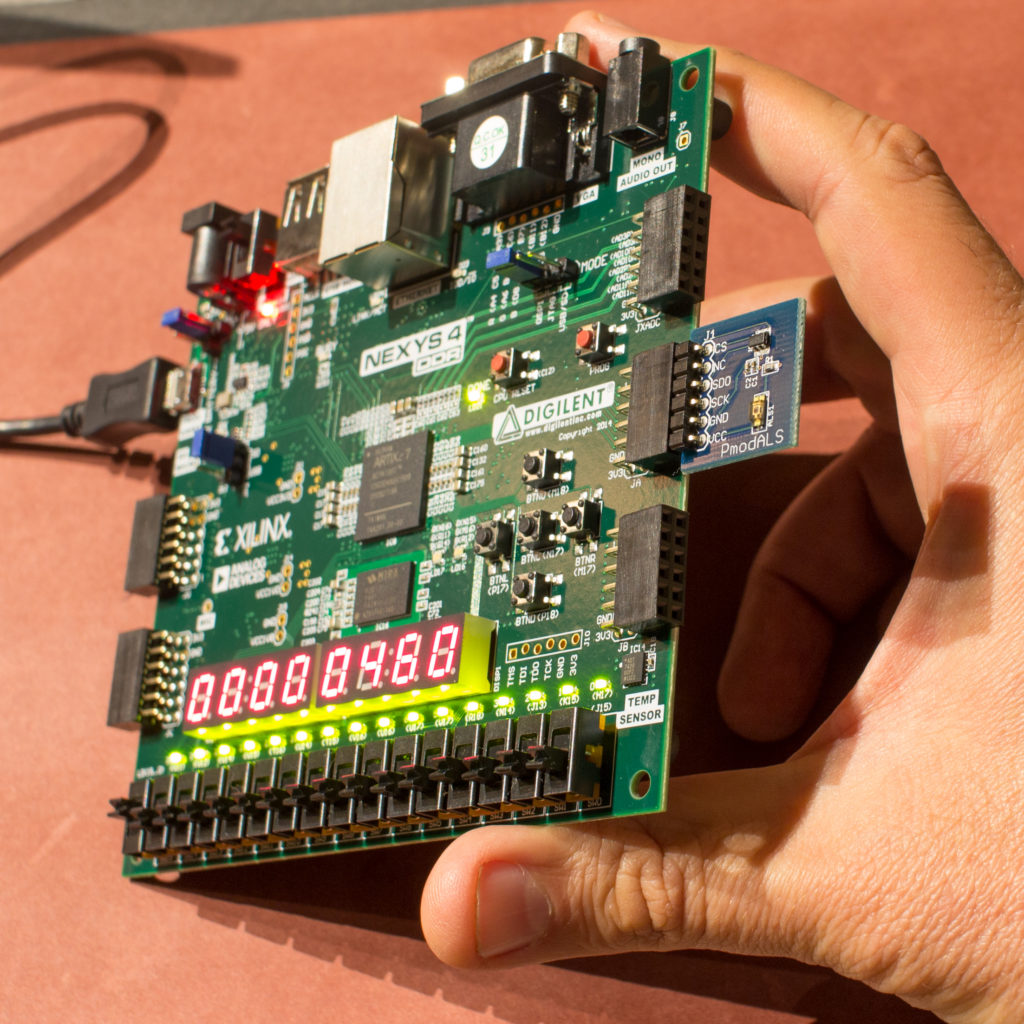

我在莫斯科的同事们都依靠我,从理论上讲,我应该在具有可重配置逻辑微电路的电路板上逐步学习说明和进行各种练习的示例。 实际上,我为其他董事会提供了一些示例,但在航班和其他事件的混乱情况下,我并没有做出任何贡献。

因此,我举了一个通用的例子,我一年半前坐在一架Alma-Ata-Astana飞机上,将例子的所有内容扔掉了,并开始在没有艰巨计划的情况下让小学生充满它。 奇怪的是,它奏效了。 在填充过程中,出现了数字电路和Verilog硬件描述语言的说明性时刻,而这在计划期间是不会出现的。

6月4日,我和我在Wave Computing的同事将在拉斯维加斯举办一次类似的研讨会,但仅限成年人参加。7月8日至19日,我将帮助MIET在Zelenograd举办暑期学校。 这些活动的计划(不是最终计划,而是由一组教师和工程师进行讨论,包括Habré上的内容)-在帖子末尾。

为什么我们需要为学童开设FPGA研讨会? 在使用硬件描述语言在寄存器传输级别研究数字电路的设计时,可编程逻辑集成电路(FPGA或FPGA-现场可编程门阵列)是在实践中巩固知识的传统方式。 换句话说,开发iPhone的关键技术-iPhone内部的微芯片就是这样设计的。 俄罗斯落后于iPhone的原因还在于,FPGA,微体系结构和硬件描述语言是在1990年代初期在伯克利和麻省理工学院引入的,而在俄罗斯则是由于苏联解体的较晚时期。

上一届Rosnanov研讨会之所以出乎意料地顺利,主要是因为参加该课程的学生初步参加了理论性的在线课程,并针对现代微电路设计方法进行了职业导向的调查。 在线课程适用于奥林匹克类型的高级学童,它由三个模块组成:

“从晶体管到微电路” ,

“数字电路的逻辑端”和

“ 数字电路 的物理端” 。 在本课程中,学生将熟悉所谓的RTL2GDSII路线-一组技术,工程师在电子公司中使用这些技术来设计大芯片(专用集成电路-ASIC)。 FPGA / FPGA用于原型ASIC,包括Intel,Apple和NVidia等公司。

自从学生参加在线课程以来,他们已经学习了D触发器,状态机,逻辑综合和跟踪。 他们还在在线课程中看到了硬件描述语言。 现在,只需要恢复就可以被动地保留在他们的记忆中。

现在,我将永远在独联体国家举办任何研讨会(除了已经计划的研讨会之外,我还建议在明斯克,索契和雅库茨克举办),为东道国通过在线课程的三个模块预先批准学童或学生提供条件,因为之后只有动力十足的人已经经历了所有繁琐的工作,而纯粹的创造力仍然需要加强,这是最后一刻,例如苹果掉到牛顿的脑袋。 此外,在线课程将所有这些活动与成人职业联系起来,下一阶段,提出了一个遥远的目标。

总的来说,在飞往莫斯科之前,我在加利福尼亚州桑尼维尔的家中举了一个普遍的榜样。

示例代码 :

在研讨会的第一天,我们在面包板上练习了集成度很小的微电路。 这项技术已有50年的历史了,但是在现实生活中,没有人比在模拟中提出D触发器的工作原理更好。 尽管在学校中许多现代技术老师似乎认为这已经过时且不必要,但是现在在麻省理工学院的6.111课程中,现在,在2018/2019学年,第一个数字电路实验室正以这种方式集成度很小的微电路-参见

http: //web.mit.edu/6.111/volume2/www/f2018/index.html 。

另外,以连接集成度较低的微电路与按钮为例,可以方便地说明其含义,原因以及上拉电阻的工作原理。 以及为什么不按下按钮时电位为0,这与分压器有何关系。

即使以集成度较小的微电路为例,即使LED烧坏了,学生也会获得必须在其中放置电阻器的生活经验。 如果他们在面包板的软件模拟器中的计算机屏幕上看到此内容,他们将不会获得这样的生活体验,因为您可以在屏幕上绘制任何内容,而学童将无法确定倦怠是真的。

这是在较小集成度的微电路上清晰可见D触发器的功能的方法:

第二天从一个历史性的草图开始:微芯片是50年前设计的,此后又发生了两次变化。 革命之一是苏联解体,这是俄罗斯没有iPhone的主要技术原因。

在8.45,故事讲述了苏联浮标间谍如何捕捉到美国船只在海洋中的运动及其产生的原因。

3月13日,一个博客作者约翰·库利(John Cooley)如何将整个全球行业从VHDL转移到Verilog的故事。

16.10年,微软Windows失去了Linux作为芯片设计人员的工作平台的故事。

在这一部分中,将演示如何在FPGA中运行用于合成数字逻辑和固件配置的程序。 有两种方式-通过在Linux和集成的图形外壳中运行脚本。 还简要介绍了演示内容。 在遍及欧洲的疾驰之后,学生们坐在图形外壳上进行简单的练习,从“或非”逻辑元素开始,逻辑元素的输入连接到按钮,而输出则连接到LED。 像这样:

module top (input [2:0] key, output [7:0] led); wire a = ~ key [0]; // 0, , wire b = ~ key [1]; wire c = a & b; assign led [0] = ~ c; // , 0 endmodule

在此过程中,立即出现了两个有趣的问题。 首先,起初我自己忘记了板上的按钮和LED都被颠倒了。 也就是说,当按下按钮时,电线上的0,而当未按下按钮时,则为1。当向LED馈入0时,它点亮,而当1不点亮时。 如果您不了解反转,则逻辑元素AND(led [0] =键[0]&键[1])开始表现为OR,或表现为OR-类似于I。 〜(a&b)==〜a | 〜b以及〜(a | b)==〜a&〜b。

但是,即使在一些小学生改正后,这项业务仍然可以正常进行。 然后我查看了他们的代码,发现当他们在重写我在板上编写的代码时,他们认为“〜”(波浪号)为“-”(减号)。 这给了我一个很好的理由来说明

直接代码和

附加代码之间的区别,以及为什么单位数(-0)== 0和(-1)== 1,而(〜0)== 1和(〜 1)==0。此外,为了在附加代码中计算多位数字的取反,将其按位求反并加一个就足够了:-a ==((〜a)+ 1)。

续篇-第2.3、2.4、2.5部分。

整个课程在Linux下进行,更确切地说是在Lubuntu 18.04下安装了Intel FPGA Quartus II。 Lubuntu装有SSD,并且还安装了Intel FPGA Quartus II Lite Edition 18.1。 要从SSD引导,只需将其插入USB 3.0端口,打开计算机电源,然后按F12键。 然后进入菜单并说“从USB加载”。

尽管Windows下也可以使用FPGA的综合软件,但是Linux的良好表现有两个原因:

1. Linux能够在比Windows更弱的计算机上运行。 例如,我有一台具有2 GB内存的笔记本电脑,因此用于Windows的Intel FPGA / Altera Quartus II放在上面,并且在Linux下可以正常工作。

2.苹果,NVidia和其他电子公司的所有成人批量芯片开发人员都使用Linux,该Linux运行Synopsys Design编译器,Synopsys IC编译器,Synopsys VCS,Cadence IES等程序。

为什么最好在可启动的SSD上进行所有操作而不将其放在教室的计算机上? 因为安装来自FPGA公司的软件是一个相当沉闷的过程,并且围绕Altera Quartus或Xilinx Vivado,您需要使用铃鼓运行,在/ etc中更改文件并为某些组件安装旧的32位库,尤其是免费版本的Mentor ModelSim。 有些库必须从源代码编译。 有

Stanislav Zhelnio的脚本可以自动完成所有操作,但是即使使用此脚本,在计算机上安装所有内容也将花费几个小时。

为什么不在虚拟机中做所有事情? 例如使用VirtualBox? 我们曾在莫斯科国立大学和其他地方尝试过此方法,但在那里可能会出现USB拉动故障。 带有Lubuntu的可启动SSD似乎是最佳选择。

要为车间准备固态硬盘,您需要将所有东西放到一个固态硬盘上,然后使用一个命令克隆它,该命令使您可以立即从一个固态硬盘写入三个固态硬盘:

time sudo dcfldd if=/dev/sdb bs=1M of=/dev/sdc of=/dev/sdd of=/dev/sde

在这里,您需要知道并非所有的SSD机箱都支持Linux,例如,Kingwin Data Star破坏了磁盘。 正确的外壳是Orico和Eluteng。

另外,我不建议尝试使用简单的可下载USB闪存驱动器替换SSD。 尽管它也可以在USB记忆棒上使用,但某些操作的速度令人难以置信,从而引起不适和不适。 但是,在带有USB 3.0的已加载SSD驱动器上,内部硬盘驱动器的运行速度比Linux快。

我还尝试通过在启动时按Option键将可引导的SSD驱动器粘贴到Apple Mac中,但是没有成功。 既不能通过USB 3.1端口,也不能通过3.0。 似乎Mac在启动时不希望了解Ext4文件系统或分区表。 我的读者中是否有罂粟驱动程序和linuxoids? 知道要做什么(除了使用VirtualBox或其他虚拟机的选项),将是很有趣的。

有趣的是,在研讨会之前,整个小组中只有2名学生使用过Linux。 这对我来说很奇怪,因为十年前Ubuntu变得用户友好时,我将取代俄罗斯教育部的所有俄罗斯学校,转而使用Linux。 除了Ubuntu,还可以制作一种特殊的俄语版Linux以进行教育。 Windows充斥着病毒,您需要为此支付版权费,为什么说Python编程学校课程比Windows更好? 还是Google文档不足以供学童使用,但需要Microsoft Word? 我就是不明白。

甚至韩国政府也决定在2020年改用Linux 。

无论如何,在我的研讨会上,学童对Linux没有任何问题,尽管正如我所说,大多数学生都是第一次使用Linux。

在第三天开始的时候,我很晚,因为我被邀请去三星的俄罗斯分公司做一次演讲,活动持续了3个小时(您可以下载演讲幻灯片:

1、2、3和

有关部分内容的文章 ),之后我饿了,只有在在Mumu(我在加利福尼亚确实很想念)吃荞麦和橄榄,发现我在体育馆上的课将在5分钟内开始。

然后我给MIET的Alexander Silantiev打电话,并要求在没有我的情况下开始上课。 在前一天,学生们开始使用带有七个字母的指示器进行运动,显示一个字母。 现在,如果将一个字母的输出与移位寄存器相交,则可以在多位动态七段指示器上实现输出,同时,学生将学习如何在Veril上编码顺序逻辑。

该计划取得了成功-当我进入教室时,一些小学生已经在一个动态指示器上缓慢地运行字母,因此他们合并为单词,所需要的只是提高为移位寄存器生成启用信号(启用)的频率:

然后,我请了IVA Technologies的Stanislav Zhelnio

sparf发言,他简要地概述了如何从简单的逻辑块转移到一个微小但完全真实的处理器(请参阅

Stanislav在Habr 上的 帖子和

在GitHub上的schoolMIPS的文章 ):

Stanislav Zhelnio的演讲继续研讨会在俄罗斯运输大学(MIIT)的语法学校举行。 在研讨会及其之前,Irina Grunicheva和Gleb Romanov(eNano)给予了帮助; MIET的Alexey Pereverzev,Alexander Silantiev和Yevgeny Primakov,HSE MIEM的Alexander Romanov和他的学生,NIIIS的Alexei Kochnov,机器人联盟(obraz.pro),Pavel Kirichenko(ICST,英特尔,

bhv.ru / books /

book的作者)

。 php?id = 201192 ),来自俄罗斯科学院

应用数学研究所的 Yegor Kuzmin,来自SUNTs的女学生Daria Krivoruchko在LYuP,Timofey Cherkasov(圣彼得堡数字技术学院,工程思想学院LNMO),Alexander Bakerenkov和来自Pre-University的JuliaI Shaltaimir,来自MPEI的Vorontsov,来自MIREA的Evgeny Pevtsov,来自Nautekh的Vitaliy Kravchenko,来自Arkady Poe 雅科夫和梅谢尔盖Pevchenko。

来自Amperka的Ruslan Tikhonov带来了用于集成度较小的微电路的运动用组件。

DMK出版社的出版商Dmitry Movchan向每位参与者提供了有用的书-大卫·哈里斯(David Harris)和萨拉·哈里斯(Sarah Harris)的一本厚实的综合教科书,数字电路和计算机体系结构,以及娱乐电子学的A. Hideharu轻松阅读。 数字电路。 漫画

莫斯科物理技术学院的马克西姆·马斯洛夫(Maxim Maslov)参加了研讨会,并为暑期学校捐赠了FPGA板(他们过去曾说俄罗斯在教育方面没有什么慈善用途)。

接下来会发生什么? 然后将有两个事件将扩大和加深我们在RTH语法学校所做的工作。 7月8日至26日将是Zelenograd的MIET暑期学校。 这是她的程序的建议。 她的前两周包括五个部分:

- 小集成度的微电路上数字电路的基础。

- FPGA板上的组合逻辑和顺序逻辑的简单练习。

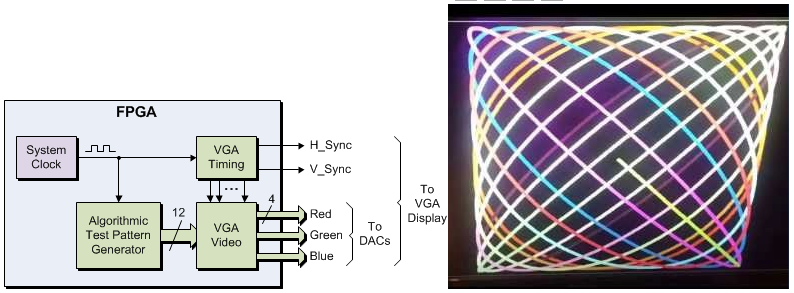

- 使用FPGA来控制图形显示。

- FPGA上最简单的微处理器的设备和实现。

- 用于制作游戏的单个项目,如简化的《愤怒的小鸟》,这两个项目完全基于FPGA硬件中的有限状态机,并具有来自FPGA中综合的最简单处理器的程序控制。

但是,在6月4日开学之前,在拉斯维加斯将有一个研讨会,在这个研讨会上我们将不讨论学校处理器,而是讨论工业设备。

Zelenograd中更详细的程序:

第1周。数字逻辑基础。

第一天。小型集成电路,组合逻辑练习

第2天。集成度较小的微电路,采用顺序逻辑进行练习

第三天,FPGA,带有按钮,开关,LED,七段指示器的练习

第4天。FPGA,将几何形状输出到VGA

第5天。FPGA,愤怒的小鸟状态机

第2周。处理器

第一天。用汇编语言编程。

第2天。一站式schoolMIPS处理器。

第3天。处理器与VGA上的几何形状的交互作用。

第4天。讲授有关中断和多任务的知识。 单个项目-在处理器上编程并输出到VGA的视频游戏。

第5天。关于传送带的讲座。 单个项目的竞争。

第1周。第1天。小型集成电路。

1.1。 具有组合逻辑的练习。

1.1.1。 CD4070上的XOR逻辑元素,不带按钮和上拉寄存器-重复演示。

1.1.2。 XOR逻辑元素,添加按钮和上拉寄存器-重复演示。

1.1.3。 单个任务-由数据仓库构建一个逻辑元素AND / OR / NOT / XOR / NOR / NAND / XNOR的演示,具有两个,三个,四个或八个输入:

1.1.3.1。 CD4081,四路2输入与

1.1.3.2。 CD4071,四路2输入或

1.1.3.3。 CD4011,四路2输入NAND

1.1.3.4。 CD4001,四路2输入或非

1.1.3.5。 CD4073,三路3输入与

1.1.3.6。 CD4025,三路3输入或非

1.1.3.7。 CD4082,双路4输入与

1.1.3.8。 CD4072,双4输入或

1.1.3.9。 CD4012,双4输入NAND

1.1.3.10。 CD4002,4输入NOR

1.1.3.11。 CD4068、8输入与与非

1.1.3.12。 CD4078,8输入NOR

1.2。 带公共阴极的7段指示器。

1.2.1。 用电阻组装在面包板上,尝试单独使用。

1.2.2。 结合7段指示器驱动器CD4511,BCD到7段锁存解码器。

1.2.3。 选项-带有公共阳极的指示器。 与逆变器CD4069,逆变器结合使用。

1.2.4。 选项-在CD4511输入上增加4个带有上拉电阻的按钮。

1.3。 组合逻辑块-一天结束时或以作业形式进行的一项单独任务:

1.3.1。 CD4532,8位优先级编码器

1.3.2。 CD4051,单8通道模拟开关,用作数字解码器

1.3.3。 CD4051,单个8通道模拟开关,用作数字多路复用器

1.3.4。 CD4052,双4通道模拟开关,用作数字多路复用器

1.3.5。 CD4053,三通道2通道模拟开关,用作数字多路复用器

1.3.6。 CD4008,4位组合加法器

1.3.7。 CD4063,4位数字比较器

1.3.8。 CD4585,4位数字比较器

归根结底,每个人都展示谁做了什么。

第1周,第2天。按顺序进行逻辑练习。

1.2.1。 组装一个基于555芯片的时钟发生器,尝试使用不同的电容器和电阻。

1.2.2。 片上CD4013的D触发器,带置位复位的双D触发器。

1.2.3。 个别项目:

1.2.3.1。 基于CD4015的移位寄存器,双4位静态移位寄存器,串行输入,并行输出。

1.2.3.2。 基于CD4035的移位寄存器,4级移位寄存器,并行输入,并行输出。

1.2.3.3。 基于CD4014的移位寄存器,8级移位寄存器,并行输入,串行输出。

1.2.3.4。 带LED输出CD4029的计数器,二进制十进制加减计数器。

1.2.3.5。 计数器通过驱动器输出到7段指示器。

1.2.3.6。 更复杂的是移位寄存器CD4035(并行输入,串行输出)和串行加法器CD4038的组合。 它需要一个CD4069逆变器。 在此之前,我将演示不带逆变器的串行加法器CD4032。

1.2.3.7。 更复杂的是移位寄存器CD4014(并行输入,串行输出)与串行加法器CD4038的组合。 它需要一个CD4069逆变器。

第一周,第三天,FPGA,带有按钮,开关,LED,七段指示器的练习

1.3.1。 组合逻辑中的逻辑元素从按钮输入,然后输出到LED。

1.3.2。 在七段指示器上输出一个字母。

1.3.3。 最简单的多路复用器是字母输出,具体取决于所按下的键。 使用“?”,“ If”,“ case”构造实现。

1.3.4。 移位寄存器。

1.3.5。 该字通过移位寄存器显示在八位动态七段指示器上。

1.3.6。 个人项目,也许是周末的作业:

1.3.6.1。 LED矩阵上的形状。

1.3.6.2。 蛇在七段指示器上运行。

1.3.6.3。 声频信号产生,声音器官。

1.3.6.4。 从16键键盘输入。

1.3.6.5。 密码锁-状态机识别键序列。

1.3.6.6。 与测距仪传感器集成。

1.3.6.7。 与角度编码器集成。

第4天。FPGA,将几何形状输出到VGA

第5天。FPGA,愤怒的小鸟状态机

第2周。处理器

第一天。用汇编语言编程。

第2天。一站式schoolMIPS处理器。

第3天。处理器与VGA上的几何形状的交互作用。

第4天。讲授有关中断和多任务的知识。 单个项目-在处理器上编程并输出到VGA的视频游戏。

第5天。关于传送带的讲座。 单个项目的竞争。

第3周。可编程收音机。 块程序包括三个主要部分:

-电动力学和无线电波传播的基础知识(理论部分);

-收发器路径的工作原理(理论和实践);

-数字信号处理的基础知识-滤波,频谱分析(理论和实践)。

第一天。电动力学和无线电波传播的理论基础。 传输路径的结构图,组件的功能。 信号(谐波,矩形)。 使用NI Elvis进行信号练习。

第2天。将信号传输到高频。 使用Matlab进行频率传输的数学依据。 使用NI Datex进行频率传输的实践练习。

第3天。信号的放大和发射。 练习使用NI Datex。 天线方向性的演示。

第4天。过滤信号。 练习使用NI Datex。 Matlab中的数字信号滤波

第5天。将信号传输到低频。 练习使用NI Datex。 总结所涵盖的材料,进行总结。

关于暑假的其他日子,在暑期学校的组委会讨论之后,更多细节将在单独的帖子中。 如果您想作为学生或教师参加Zelenograd MIET的暑期学校,则

组织者刚刚发布了联系方式和注册信息 。 如果您是学生,则必须在7月前完成Rosnanov在线课程的所有三个模块(

“从晶体管到微电路” ,

“数字电路的逻辑端”和

“数字电路的物理端” ),这一点很重要。 这种做法将很困难,并且我们将无法停止找出该值在D触发器的输入或输出处的周期。 这并不马上就适合您,但是如果您参加在线课程,对您来说会更容易。

有关6月4日在拉斯维加斯举行的研讨会的

有关6月4日在拉斯维加斯举行的研讨会的一些详细信息:

最初是为俄罗斯开发并在俄罗斯(包括MIPT),乌克兰和哈萨克斯坦进行测试的工程研讨会然后在拉斯维加斯举行的电子设计自动化会议上发生的,这种情况很少发生。 在俄罗斯和乌克兰,它被称为MIPSfpga研讨会,在设计自动化会议上,它被称为MIPS开放开发者日。 将于6月4日在拉斯维加斯天堂路3600号希尔顿会议中心大使馆套房举行,您将参加一场表演,表演者包括莫斯科国立大学,莫斯科物理与技术学院,莫斯科工程物理学院,泽勒诺格勒MIET,圣彼得堡ITMO,托木斯克州立大学,基辅KPI,阿拉木图AlmaU和位于阿斯塔纳的纳扎尔巴耶夫大学的一部分。

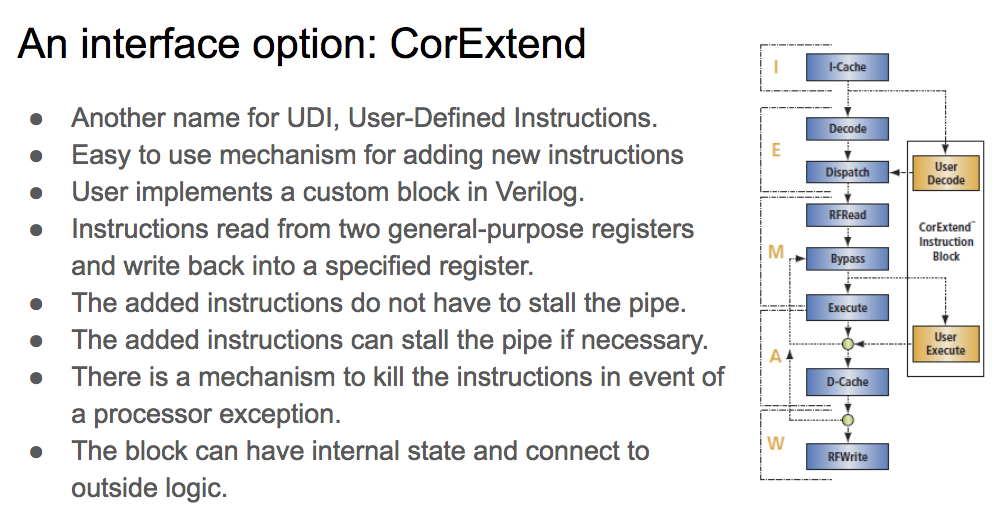

MIPSfpga是一个软件包,在Verilog的源代码中包含处理器核心,您可以更改,添加新指令,观察缓存和管道的操作,构建多处理器系统,同时更改软件和硬件,等等。 在研讨会的新版本中,您将在处理器中添加协处理器以加速人工智能算法。

此外,在研讨会的新版本中,我们将展示如何从MIPS microAptiv UP软件包配置内核并将其插入MIPSfpga绑定。 配置后,您可以创建外来处理器选项,例如具有16组32个寄存器的处理器。 您可以在进入中断时自动切换这些设置,从而快速更改上下文,而无需从内存中保存/恢复上下文,这在普通的RTOS中大约需要一千个周期。

MIPSfpga并非旨在从绝对零注入到对象中。 为了有效地使用它,学生有必要已经了解数字电路的基础知识,能够用C语言和汇编语言进行编程,并且还提出了微体系结构的概念-传送带,管道冲突等。 这是我们在Zelenograd中使用的schoolMIPS正在研究的内容。

这是有关向MIPS microAptiv UP处理器添加指令的机制的幻灯片:

在6月4日于拉斯维加斯举行的研讨会上,可能是在7月8日至26日在Zelenograd的MIET举办的年轻电子工程师暑期班上,我的女儿Elizabeth Panchul将帮助我(如果她按时获得签证)。 由于伊丽莎白是半俄半俄/乌克兰人,她只会说英语。 因此,俄罗斯教官(莫斯科物理技术学院,莫斯科国立大学等的学生或研究生,他们随时准备帮助我们与伊丽莎白和MIET进行学校合作)可以从她那里学到正确的英语口音,也可以从他们那里学到英语的基本口音。 除了研究Verilog,MIPS,体系结构,微体系结构以及在图形屏幕上显示时,还可以将DMA组织到内存中:

我们在所有研讨会上以及在委员会中为您创建程序都在等您!