10 nm IceLake的可能照片。 来源

10 nm IceLake的可能照片。 来源处理器市场正在发生奇怪的事情。 英特尔方面的全球领导者已经努力尝试转向10纳米制造工艺,这已经是第五年了。 最初,他们宣布在2015年过渡到10 nm,然后在2016年,2017年……在2019年,而英特尔系列中的10 nm仍然不存在。 好吧,不,有一些实验/工程样品,但是高产量是个问题。 真正的过渡预计

不会早于2022年 。

实际上,这就是市场上英特尔处理器短缺的原因。 为了克服这个问题,该公司扩大了修改后的14 nm处理器的生产范围(仅在外形上与该Lake相同),甚至恢复到22 nm。 似乎回归很明显。 目前,韩国三星,台湾台积电和AMD已将它们与ZEN 2平台一起加入,据报道它们将引入7纳米,并将转换到5纳米。 他们从尘土飞扬的内阁中拿出了“摩尔定律”,并宣称它比所有人都活着。 很快就会有3 nm,2 nm甚至1 nm(

原文如此 )-pourquoi pas?!

怎么了 真正

狡猾的亚洲人在关键行业击败了

该死的笨蛋吗?

我可以开香槟吗?免责声明:我是偶然发现

这篇文章的 ,并且惊奇地发现它多么能干和详尽地揭示了现代微电子学的问题,尤其是摩尔定律和市场营销的消亡。 曾几何时,我本人涉足于有关

芯片制造的文章撰写,而

在“ Inside Look”系列文章中,我什至查看了其中的内容,也就是说, 这个话题对我来说非常有趣。 自然,我希望原始文章

的作者将其发表在哈布雷(Habré)上,但出于就业方面的考虑,他允许我将其转移到这里。 不幸的是,Habr规则不允许直接复制粘贴,因此我添加了到源代码,图片的链接和一些插科打and,并尝试使文本更直一些。 是的,我了解并尊重非

生物学领域有关该主题的文章(第

1和第

2条 )。

因此,让我们一起解决问题。 我们将尽可能多地研究物理和技术,而不是细微差别(其名字叫团!)。 下面的描述是简化的,有时是示意图。 写评论,我们将尝试进行建设性的讨论。

前言

“不是所有事情都那么简单……”一位军官的女儿曾经说。 如果看一下晶体管的密度,那么英特尔的14纳米技术和台积电的7纳米技术几乎是相同的(

糟糕! )。 甚至英特尔将其回滚到22纳米都不会对性能产生重大影响。 什么鬼 按照所有规则,从14 nm技术过渡到7 nm技术应使晶体管的密度增加多达4倍。 这是根据戈登·摩尔(Gordon Moore)的戒律而制定的,戈登·摩尔(Gordon Moore)刚刚庆祝

了该法律成立50周年 ,而纪念日则是其55周年!

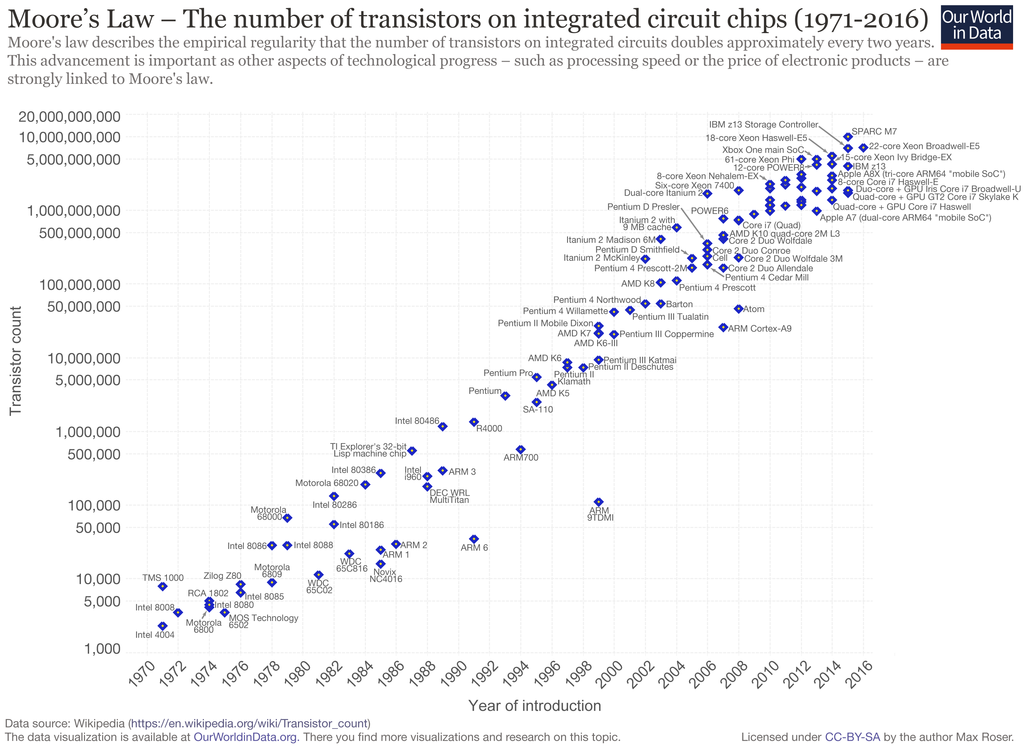

摩尔定律是铁定律。 如您所见,我们已经在现场“标记”了大约5年。

摩尔定律是铁定律。 如您所见,我们已经在现场“标记”了大约5年。同时,正在做出混合陈述。 有人认为“摩尔定律”比以往任何时候都更重要,微电子将像以前一样发展。 出色的科学家,设计师和工程师将克服任何限制,甚至克服物理定律。 人们需要新的成就,他们不会花很长时间。

其他人则说所有的人都达到了身体极限,我们会舔什么,但这是正常的。 长期以来一直对此提出警告。 因此NVIDIA的负责人

在CES 2019上表示,摩尔定律已死,现在必须更改发展的向量(黄不应该在向量中,而应在张量中)。 AMD和GlobalFoundries的光刻专家

都同意他的

观点 。

实际上,所有这些单位和数十纳米的技术标准早已脱离了物理尺寸,已成为更多的营销要素。 至少最近15年:从130 nm过渡到90 nm之后。 那时是第一次面对的不是技术限制,而是基本的物理限制。 顺便说一下,专家们谈论了这个问题,但根据

Leni ... Moore博士的戒律,营销人员的虚假广播淹没了他们安静的声音,他们假装什么都没有发生,一切都按照自己的方式进行。

不幸的是,对于营销人员,也许对我们来说幸运的是,摩尔定律不是自然定律,而是英特尔创始人之一戈登·摩尔(Gordon Moore)于1965年提出的经验观察。 根据他的观察,新系列的微电路每隔一年就会出现一次,而其中的晶体管数量却增长了约2倍。 1975年对法律进行了修改;据此,每24个月应翻一番。 从那时起,将近40年来,摩尔定律已经提高到了数字微电子制造商的标志和旗帜的位置,有时它们被扭曲了(24个月变成了36个月,现在停滞不前-参见上图)。

在此过程中,出现了各种技术限制,从而减慢了该过程(通过衍射极限的相同过渡)。 或突破使小型化急剧增加。 对于外部观察者而言,在完全遵守摩尔定律的情况下,一切似乎都在稳定增长,尤其是营销人员的努力。

“ Silicon下硅”的物理学

我将从硅极开始。

硅只是微电子制造商的天赐礼物。 不仅如此,从字面上讲,硅还是具有非常合适参数(就电,能和物理特性的组合而言)的良好半导体。 纯硅几乎是一种电介质;电导率完全取决于杂质的浓度。 它具有高导热性,技术先进,并能抵抗侵蚀性环境。

Likbez适合初学者常温下的硅是具有立方晶格的半导体。 硅原子的4个外部电子被“社会化”,即 属于晶格的所有原子。 它们不是自由的,但并不牢固地附着在原子上。 这是半导体的特征。 有一阵子,这些电子围绕它们的原子旋转,然后被转移到相邻的电子,而相邻的电子到达它们的位置。 因此,外部(价)电子在整个晶体中从一个原子到

另一个原子随机传播(

注意:并非如此,电子本身不传播,它们仅通过相互相互作用传递能量 )。 有时,某种电子与原子完全脱离,并开始(准)在晶格之间自由移动。 取而代之的是带有未填充电子空位的正硅离子-“空穴”。 下次电子从邻居处转发时,空位被填充,但它出现在邻居处,然后出现在他的邻居处,依此类推。 孔也开始随机穿过晶体。

如果我们现在施加电场,则自由电子将从负飞到正。 价电子也受场的作用,并开始迅速向正侧填充空位,并且空穴空位将流向负侧。 这种行为看起来像空穴是仅带有正电荷的自由电荷载流子(例如自由电子)。 用与电子相同的公式描述空穴的行为,并针对较大的“

有效质量 ”进行校正。 因此,它们通常不蒸腾,为简单起见,将孔视为带正电荷的普通基本粒子。

在室温下,每万亿个硅原子有一个电子-空穴对(浓度10

-12 ),在室温下纯硅是绝缘体(有条件的:电子和空穴相互an灭的速度太快,没有时间到达晶体的末端)。

如果现在将具有5个外部电子的原子(例如磷)引入到硅晶格中,则该原子将包含在4电子交换中,而第五个电子则变为自由。 我们从自由电子中获得正磷离子和嵌入硅中的“电子气”。 具有这种杂质的硅的电导率线性增加;每百万个硅原子(

ppm )中一个磷原子的

浓度已经大大改变了电性能。 磷的混合物称为施主,半导体本身称为

N型导电率 。 除磷外,它还可以是砷或锑。

现在,我们将具有3个外部电子的纯硅原子添加到其中,例如硼。 它也包含在4电子交换中,但只能产生3个电子。 在邻近的硅原子上,出现了一个“洞”,并在穿过晶体的过程中引燃。 我们得到负硼离子和带正电的空穴气体。 这种杂质称为受主,半导体为

P型 。 除硼外,受体还包括铝,镓和铟。

顺便说一下,极难获得纯硅(因此它是绝缘体)。 硼的存在

总是使硅成为p型半导体。

硅的好处是其氧化物-二氧化硅SiO

2 。 它是几乎完美的电介质,具有高强度和硬度,可抵抗除氢氟酸(HF)之外的所有酸。 同时,氢氟酸本身不会溶解硅,因此您可以不怕腌制过量的硅。 即使在室温下(自然,在空气中),氧化硅薄膜也会形成在硅表面上。 为了获得厚的氧化膜,可加热硅或使用含硅气体的低温沉积。 当晶体中已经沉积了层时,将使用沉淀,并且加热将导致拓扑结构的“拖尾”。

化学家的烦恼,周期性系统每年一次:向右移动-P,磷,氧化物形成磷酸,向左移动-Al,铝,金属,向上-C,碳,氧化物-气体,向下-Ge在地壳中的普及率较低(千现在费用〜1k $)。

尽管一直在谈论硅时代即将结束和向其他半导体的过渡,例如结构A

3 B

5 (砷化镓,磷化镓或氮化镓),碳化硅,金刚石,

石墨烯等,因为它们具有更高的有效电子迁移率和空穴,较低的温度依赖性,较高的热导率,硅在大众微电子领域占统治地位。

是的,对于A

3 B

5,可以创建

异质结 。 此时,晶体管内部的面积不仅导电类型不同,而且物理结构也不同,这提供了更多的机会。 在其他条件相同的情况下,氮化镓微电路可以在更高的频率下工作,耐高温并提供更好的散热。 但是,尽管这些材料仅用于分立元件和小型微电路。 对于大型微电路,该技术的复杂性使其价格比硅高几个数量级。 是的,并且没有获得“其他相等”。 因此,替代的非硅微电路的专业化范围狭窄。

场效应管

考虑一下数字微电路的主要组成部分-具有感应沟道的平面场(flat)晶体管。 他是

MOS (金属氧化物半导体),他是MIS(金属介质半导体),他是MOS(金属氧化物半导体),他是

MOSFET 。

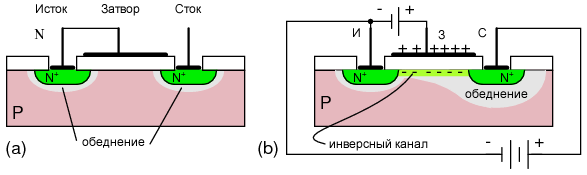

n沟道晶体管的剖面示意图

n沟道晶体管的剖面示意图工作原理说明我们有一个p型导电性的硅基板。 它创建了2个n型层-源极和漏极。

双极型晶体管的发射极和集电极的类似物。 在它们之间,被电介质层(通常是氧化硅)与硅隔开的电极是栅极。 百叶窗下面的区域称为底部。 如果在源极和漏极之间施加电压,将不会有电流,因为它们之间将存在反向偏置的

pn结 -晶体管关闭。 从原理上讲,这是一个锁定二极管的模拟。 正确连接后,这是基极和漏极之间的过渡。

现在将正电压施加到栅极。 电场穿过氧化物,穿透硅,从空穴的表面层排斥空穴(+),并吸引自由电子(-)。 后者在p型衬底中虽然很少,但存在。 在栅极的某个电压下,在电子的表面层中,它变得比空穴更多。 发生反转,并且在氧化物层下方出现n型沟道。 电流将从源极流到漏极-晶体管断开。 开路晶体管是一个逻辑单元,闭路晶体管是一个逻辑0。嗯,反之亦然,具体取决于实现方式。

对于p沟道晶体管,n和p区域互换,并且晶体管在负栅极电压下打开。

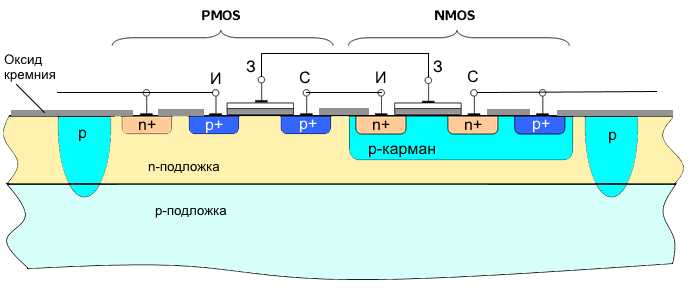

MOS晶体管的优点是紧凑。 但是还有一个严重的缺点-高功耗,因为在断开状态下,直通电流流过晶体管。 因此,自1970年代以来,

CMOS晶体管 (

互补MOS )一直在数字技术中占主导地位。 这些是具有组合门的串联p沟道和n沟道晶体管。 通常在一个单元格中完成。

如果我们给门加信号-n沟道晶体管打开,则p沟道关闭。 没有直通电流,输出端为负。 如果我们给栅极加一个负号-n沟道晶体管关闭,则p沟道打开。 再也没有直通电流,再加上输出。 即 该元件还可以用作逆变器。

这是最节能的技术。 在静态状态下,该元件不消耗任何电流(杂散泄漏电流除外),仅消耗开关电流。 功耗几乎与芯片频率(充电周期数)成正比。 低功耗和紧凑性决定了CMOS技术在数字电子产品中的主导地位。

双极晶体管电路最初提供了更高的性能,但更复杂,占用更多空间并消耗了一个数量级以上的能量。 我必须说,支持CMOS的选择已完全奏效。 在其他技术上获得当今处理器这样的特性几乎是不可能的。 虽然看不到替代方案。

拓扑功能

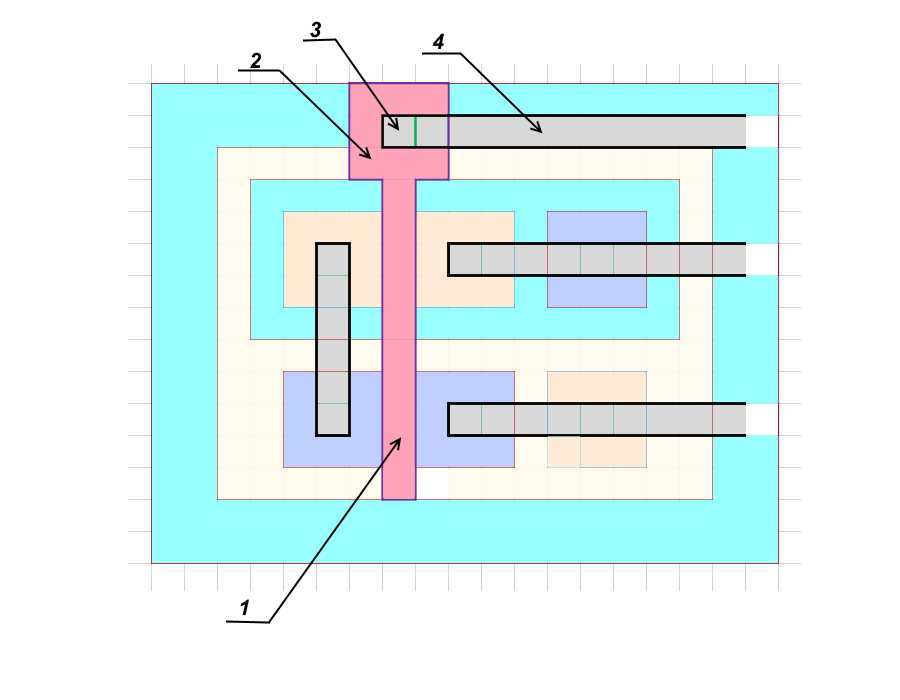

芯片的芯片拓扑通常可以表示为单元中的一张大纸,其中区域的边界沿线绘制,技术尺寸就是单元的尺寸。 实际上,对于非关键元素,您也可以缩进半个单元格(两个lambda的规则),但这是细微差别。

详细的拓扑设计让我们从精神上追溯到1980年代末,那时这些技术仍然简单易懂。 考虑一对真正的CMOS晶体管。 窗口n +和p +高度掺杂(每数百甚至数十个硅原子1个杂质原子),即 杂质水平比n和p高几个数量级。

假设我们被赋予TK来在孤立的口袋里画出这样一对晶体管的拓扑。 由于不会有大电流流过晶体管,因此我们将基于最小的技术规模(即所谓的技术许可)进行计算。 称它为d。

个人资料

个人资料 顶视图

顶视图让我们从n沟道晶体管

(1)的源极的接触窗口开始。 我们将其设为最小的

d * d 。

这样,源

(2)的大小将为

3d * 3d (您需要至少从窗口的边缘后退)。

基座

(3)由最小宽度

d 制成 。

此外,具有其接触窗口的原料

(4)也是

3d * 3d 。

最后一个元素是与p基接触的高合金区

(5) ,以及

3d * 3d 。 需要使源极和基极的电压相等,以便不会出现通道的自发出现。

从绘制的窗口绘制p口袋本身

(6)的边界,即另一个

d 。 p窗口的大小为

5d * 13d 。

下面我们画一个p沟道晶体管。 我们通过这种安排将整个元素近似为正方形-组装起来更容易。

我们更改源极和漏极的位置。 这种布置使接触金属轨道的长度最小化。 让我们从排水管

(7)的接触窗口开始,其大小最小

-d * d 。

漏极

(8)将为

3d * 3d ,其基极

(9)的宽度为

d并与n沟道晶体管的基极对齐。 源

(10)和与基部

(11)的高度合金化接触面积也将为

3d * 3d 。

最后一个大小是分隔路径

(12)的最小缩进量,即另一个

d 。

总计接收到晶体管对

11d * 15d的尺寸。 在我们的情况下,单独的走线是另一个p型区域,与n衬底形成反向偏置的pn结。

还有另一种选择,可以使用介电二氧化硅SiO

2或蓝宝石Al

2 O

3进行绝缘。 后一种选择是可取的,但明显更昂贵。 在这种情况下,可以靠近分割路径形成区域,并且单元之间的泄漏电流将为零。 通常,分离轨道的宽度略大于外延层的厚度(在下文中有更多说明),并且等于

2d 。

划分路径中间的总有效像元大小为

13d * 17d 。

然后,在氧化物的顶部绘制一个闸板

(1) ,去除闸板靠近分割路径的接触区域

(2),并形成一个接触窗

(3) 。

最后阶段是金属化和接触路径

(4) 。 铝最初用作栅极和接触路径的材料(尽管

在某些设备中仍使用铝),后来栅极由高度合金化的多晶硅制成,接触路径由铜制成。

假设我们生活在

3微米制程技术中。 然后,如上所述,我们的两个晶体管单元

11d * 15d将具有

33 * 45微米的尺寸。 但是后来我们陷入麻烦,转而使用

1.5微米的新工艺技术。 我们的电池尺寸变成

16.5 * 22.5微米 。

以前一个单元可以容纳的地方,现在最多可以容纳四个。同时,这四个电池消耗的电流多达一个旧电池(在相同的频率和电流密度下)。连同每个晶体管的线性尺寸,其寄生电容和电阻减小,并且开关期间的瞬变时间减少。这样的晶体管可以在较高的频率和较低的电源电压下稳定地操作。而且,将大量元素整合到一个晶体中可以最大程度地减少访问慢速外部总线的需求。 我们知道,减小晶体管的尺寸是一项纯粹的好处,并且没有危害。这就是为什么自微型微电子技术问世以来,微型化已成为其主要任务的原因。技术许可限于什么(这也是设计规范)?为此,您需要稍微了解一下芯片制造技术。

我们知道,减小晶体管的尺寸是一项纯粹的好处,并且没有危害。这就是为什么自微型微电子技术问世以来,微型化已成为其主要任务的原因。技术许可限于什么(这也是设计规范)?为此,您需要稍微了解一下芯片制造技术。技术流程

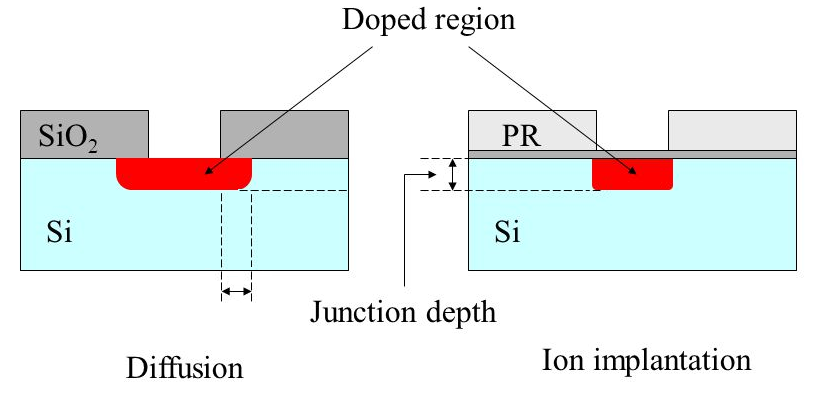

通过从熔体中缓慢拉伸的方法(Czochralski方法)获得单晶硅。必要的杂质被添加到熔体中,以确保均匀的合金化(注:我会与原始作者争论,因为根据Czochralski的说法,纯硅(相对)是生长的,所以他们非常害怕坩埚中的杂质,并且仅在以后产生所需的合金化水平例如,通过离子注入板本身。Cornelius Agrippa纠正:实际上,当板生锈时,杂质可以直接添加到熔体中,因此它们会立即使板掺杂有杂质(KEF,KDB,具有不同的电导率)稍后在制造芯片的阶段使用离子注入。在输出处,获得圆柱状的毛坯(直径为200或300毫米),然后将其切割成厚度约为0.5-0.7毫米的薄板(即 晶片)。后来,在一个技术周期内就在它们上形成了数十个微电路。试图切换到直径为450毫米的印版,但是到目前为止,它还没有运行。很难在板的中心和边缘保持相同的工艺条件(温度分布,杂质等)。然后,在板的工作侧,建立具有不同类型导电性的硅薄层-外延层。建造方式不同:例如,通过还原气态四氯化硅(SiCl 4)在这种情况下,将掺杂剂添加到气体中。所得层延续了晶体板的结构,但是具有不同类型的导电性。在上面的示例中,我们有一个p型硅衬底和一个n型外延层。有时,在外延生长之前,会在基板上形成n型或p型袋。所谓隐藏层。然后是在外延层中创建源极,漏极,p基极,接触和划分区域的过程。工艺流程的本质是在正确的位置去除氧化物,打开硅本身,并向其中引入必要的杂质。通过扩散或离子注入引入杂质。在扩散过程中,将带有清除了氧化物的窗口的硅晶体放置在包含气态杂质的气氛中,然后加热到700摄氏度以上的温度。通过用b加热开始振荡硅原子约 PROC EED振幅和杂质原子被逐渐引入到结晶硅晶格作为会溶解。掺入速率与温度成指数关系。原则上,该过程也将在室温下进行,但是等待仅需数年。通过调节温度和持续时间,可以获得所需的层深度和浓度。在后续操作中加热会腐蚀已经形成的层,因此,它们会在过程开始时尝试执行所有高温操作。扩散方法的优点是其简单和低成本。不利的一面是,在扩散过程中,杂质不仅被引入到晶体的深处,而且还被引入到氧化物下方。因此,底座的实际宽度小于我们绘制的宽度。如果过度加热,栅极下方的源极和漏极将关闭,晶体管将变成电阻器。对于数百纳米的元素,不使用扩散。 在离子注入过程中,杂质原子被电离,被电场加速,并轰击硅晶体。选择离子的速度和氧化物的厚度,以使离子渗透到硅中达到所需的深度,但不能穿透氧化物层。杂质离子将硅原子从晶格中撞出或卡在晶格之间。注入之后,加热晶体以由于原子的热振动而恢复晶格结构。加热温度低于扩散过程中的温度;因此,氧化物下的杂质进入明显减少。

在离子注入过程中,杂质原子被电离,被电场加速,并轰击硅晶体。选择离子的速度和氧化物的厚度,以使离子渗透到硅中达到所需的深度,但不能穿透氧化物层。杂质离子将硅原子从晶格中撞出或卡在晶格之间。注入之后,加热晶体以由于原子的热振动而恢复晶格结构。加热温度低于扩散过程中的温度;因此,氧化物下的杂质进入明显减少。 有时,它用于需要高合金均匀性的特殊应用中,例如在功率半导体中,在核反应堆中使用注入。感谢tnenergy为我们

有时,它用于需要高合金均匀性的特殊应用中,例如在功率半导体中,在核反应堆中使用注入。感谢tnenergy为我们快乐的核童年启蒙运动。平版印刷

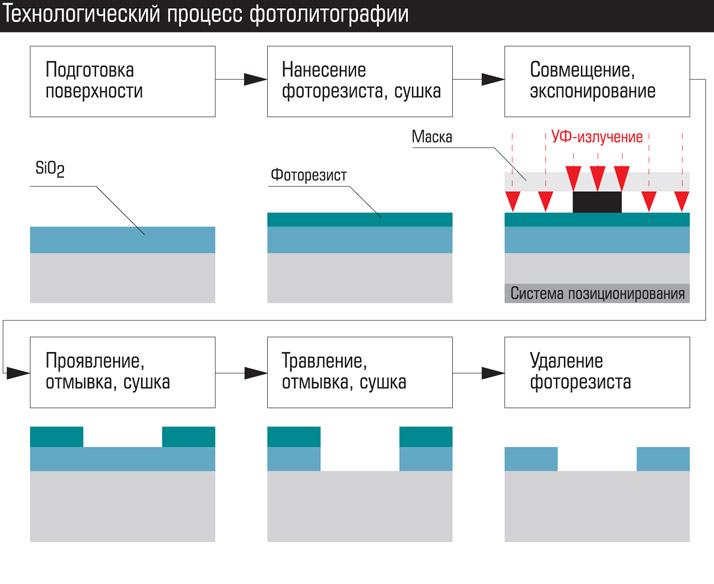

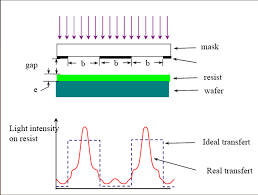

现在介绍主要和最有趣的过程-光刻。使用它,可以在硅表面上形成层图案。考虑最简单的接触式光刻技术(photolithography)。 主要步骤:

主要步骤:- 在硅晶片的表面上形成氧化膜。

- 在氧化物-光致抗蚀剂的顶部上施加特殊的糊剂。该板在离心机中旋转,以使光致抗蚀剂均匀地分布在表面上。

- . – . , , p- . ( .: -) .

- . . , ( ) ( ). .

- – .

- . . , , ( shadowing effect).

- .

在操作结束时,我们获得了一块去除了氧化物部分的板,可以将其发送出去进行扩散,离子注入或金属沉积(

注意:或电沉积)。 在形成该层之后,通常从板的整个区域蚀刻氧化物,并沉积新的氧化物。

Windows从宽到窄创建。 在我们的情况下,顺序如下-分离区域,p型腔,p +层,n +层,带有金属化层的接触窗,施加挡板,挡板的接触区,第一层金属走线以及第二层下方的接触区,第二层金属化层等。 。 在现代处理器中,金属化可达10-15层。

接触光刻技术是在微电子技术诞生之初使用的。 现在最主要的是投影光刻。 这是将透镜和反射镜系统放置在辐射源和光掩模之间以创建变窄的光子束的情况。 下图示意性地显示了不同的光刻方法:带间隙的接触式光刻,通过透镜的投影,镜面投影。

光刻的优点是高速和低成本。 整个板区及其所有微电路都立即暴露在外,整个过程需要几分钟。 或者是几个微电路的平方,然后是极板移位。

除了光刻之外,还有其他类型-电子,X射线和离子。 最有趣的是电子光刻(例如

BarsMonster 撰写的Mapper项目)。

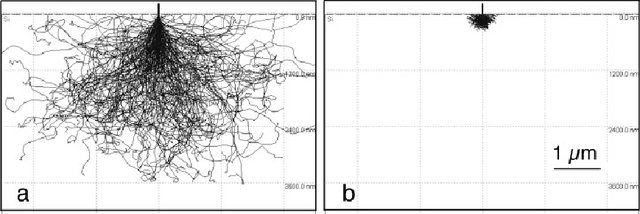

对于电子光刻,抗蚀剂的曝光不是通过光而是通过电子束进行的。 最简单的形式类似于

CRT显像管上的图像形成。 在所有类型的光刻中,电子光刻可提供最清晰的图像和最高分辨率。 缺点是曝光时间长。 在现代技术中,电子束的厚度为几纳米甚至几分之一纳米,板直径为300毫米。 自然,不使用一个捆绑包,而是由计算机控制的数万个捆绑包。 但是需要非常强大的总电子通量。 为了进行比较,紫外线辐射量子的能量为几

eV ,光束中的电子能量为几千电子伏特。

另外,电子带电并相互排斥,这导致电子束发散。 当然,可以提高电子的速度,但随后电子将穿透抗蚀剂或在任意方向上以高速反射,从而导致二次辐射(

Secondary Electrons )并因此引起曝光。 所有这些限制了技术的使用。

电子光刻用于创建光掩模。 一个光掩模的曝光时间为几天。 因此,光刻在微电路的生产中占主导地位。

一套用于处理器的现代化光罩要花费数千万美元。 毫不奇怪,鉴于现代处理器包含数十亿个晶体管,并且板上有数百个处理器。 另外,现代光掩模中的窗户不仅是材料中的孔,而且通常是具有特定光学特性的其他材料。 一组真实的光罩包含数十个光罩。 在最新的制造工艺中,超过50(

sic! )。

但是它们使您可以像热蛋糕一样压印微芯片。 在其生命周期中,一组照片模板可让您在输出中获得数十万甚至数百万个微芯片。

那么,什么限制了工艺技术的规模呢?

可以有条件地区分4组因素:

- 硬件和技术。 与硬件分辨率关联。

- 技术过程的物理。 它是由特定过程的物理局限性决定的,可以通过更改技术或材料来避免这种局限性。

- 物理的。 这些限制是无法避免的,但其影响可以最小化。

- 极端的身体。

硬件和技术限制

这种限制在微电子学的早期阶段起着决定性作用。 主要是指生产“无尘室”,用于工艺流程的精密设备,仪器仪表(对产品质量控制很重要)。 例如,光刻需要超精密的光学器件,强大的显微镜,将掩模和平板结合起来的精度为纳米级的机构,超纯气氛或曝光期间的真空等等。 必须非常准确地承受工艺过程的参数-温度,持续时间,大气成分,辐射功率,表面处理。

现在,设备的精度不再是限制因素。 不是因为这是一个简单的问题。 查看现代投影图或镜面光刻的图足以了解复杂程度。 但是,对于有才华的设计师和工程师来说,没有障碍的情况确实如此。

技术问题通常与第一个系列有关。 随着工艺过程规范的改变,不仅水平尺寸,而且垂直尺寸,杂质浓度和活性区的比例也改变。 现在,随着每个新步骤的出现,过程的物理原理也在发生变化。 自然,所有参数都是预先计算和建模的,但实际情况总是会进行调整。 因此,对于第一个系列,通常认为合格电路的合格率是3%(不良率为97%)。 逐步优化了工艺流程,适合最后一个系列的收率超过90%。

工艺过程物理

直到最近30多年来,这些因素一直在限制。 我已经列出了这些限制中的一些限制-扩散过程中进入氧化物下面的杂质,蚀刻过程中腐蚀在光致抗蚀剂下面的氧化物,以及热处理过程中已经沉积的层的腐蚀。

解决方法也被部分描述。

扩散被离子注入代替。 另外,对于最小的层,杂质材料也发生了变化-使用磷代替砷,砷而不是硼镓。 它们的原子更大,更重,因此在相同温度下它们在硅中的溶解性更差(最重要的是,它们扩散起来更困难!)。 对于离子注入来说,这并不重要,但是在随后的加热中,这些层的侵蚀要弱得多。

通过加热产生的氧化物已经代替了气体中的低温催化沉积。 使用加热,但仅在刚开始时加热,此时晶体是干净的。 在一些操作中,使用氮化硅(Si

3 N

4 )或连续的氧化物和氮化物层代替氧化物。

液态酸蚀刻变为离子蚀刻。 酸仅用于去除整个区域的氧化物。

另一个问题是用于栅极电介质的超纯氧化物的生产。 该氧化物作为芯片上的工作元素保留下来,并且对纯度和均匀性有很高的要求。 局部的氧化物厚度小于10个原子层。 小缺陷会导致穿孔或击穿。 这使百叶窗与基座电气闭合,从而使元件失效。 一段时间以来,使用了一层氧化物和一层氮化硅的交替层。 在90 nm技术中,氧化ha HfO

2被用作栅极电介质。

顺便说一句,在苏联时期,正是获得高质量氧化物的问题拖慢了向CMOS的过渡。 因此,寻找替代路径和数字微电子学的普遍滞后。

最关键的操作是光刻。 如此之多,以至于到目前为止,许多人已经将整个技术过程的分辨率与光刻技术的分辨率放在一起。 自1980年代后期以来,光刻的主要问题是光的衍射。 更确切地说,紫外线辐射虽然原理相同。 毫不夸张地说,在过去的30年中,减少工艺流程规模的斗争主要是与衍射的斗争。

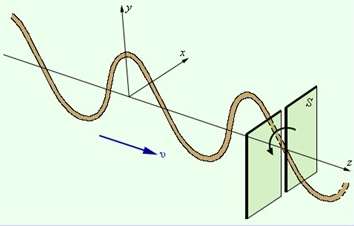

光的衍射是光学创始人的祖先在18世纪发现的:

当穿透孔时,光线和任何其他电磁辐射(EMP)偏离直线路径,发散并穿透到阴影区域。 在接近波长的孔尺寸处观察到该现象。 与波浪相比,孔越小,色散越强。 该规则在四分之一波长间隙之前有效。 孔小于波长的四分之一,EMP光束只是“看不见”,并以很小的间隙从表面反射,例如从实心的间隙反射。

硅LED的波长约为1μm(近红外),可见光的波长为780 nm(红色)至380 nm(紫色)。 小于380海里,紫外线(UV)开始。 如今,光刻中使用的发射器具有248 nm和193 nm的波长,这是受激准分子激光的辐射(例如,

在XeF 2上 )。 因此,在克服了3微米的技术要求之后,衍射问题上升到了其最大高度,而在800 nm之后,它们成为了主要问题。 由于曝光过程中的衍射,UVI进入不透明掩膜下的区域并照亮阴影中的光刻胶。 结果,我们得到一个模糊的煎饼,而不是一个清晰的正方形。

除了腐蚀窗户之外,对于间隔很小的窗户,还会产生重叠(干扰)侧波的影响。 耀斑的峰值出现在光罩反射部分的下方。

光学-无情的你...有什么方法可以解决这种现象?

光学-无情的你...有什么方法可以解决这种现象?第一步是使用投影光刻。 如果大大简化,则在光掩模和板之间安装一个透镜,该透镜会收集发散的光线并将其聚焦在光刻胶上。

另一种方法是减小曝光辐射的波长。 一次,他们开始使用辐射波长为436 nm的弧形汞灯-这是蓝光。 然后是405 nm(紫),365 nm(近紫外线)。 在此,汞灯时代的结束,准分子激光器的使用开始了。 首先是248 nm(中紫外),然后是193 nm(深紫外)。 在这个过程中陷入僵局。

事实是它们达到了石英光学器件的传输极限。 短波吸收石英。 有必要要么切换到镜子系统,要么使用其他材料的镜头。 基于氟化钙光学元件在157 nm处进行了实验安装。 但是,他们从未参加过该系列赛。 由于存在优化193 nm光刻的方法。

激光上的视觉图表。

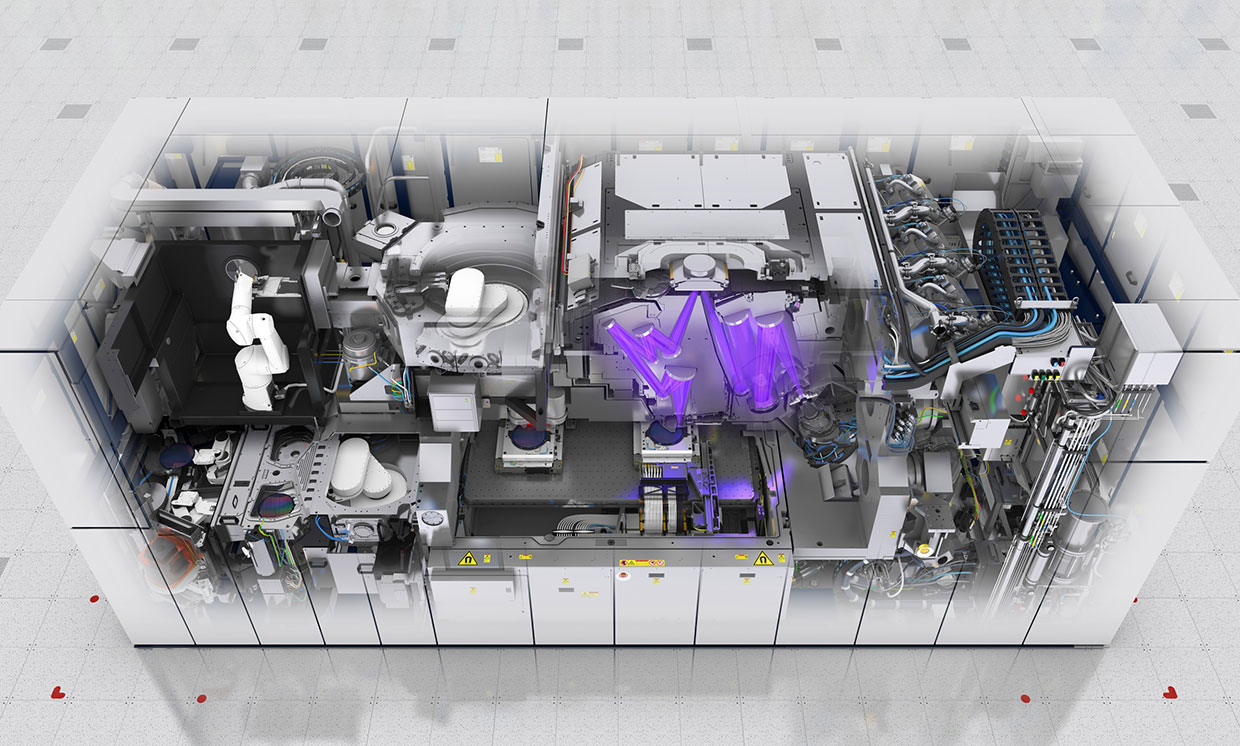

来源EUV光刻

在1990年代中期,他们开发了一种标准的波长为13.5 nm的极紫外光

刻 (

EUV光刻 )。 该波长使得可以给出以nm为单位的分辨率。

到2000年代初,出现了第一批实验样品。

在2000年代末,技术应运而生。 最后,有消息传出,三星和台湾台积电将于2019年改用EUV光刻。 不到15年的时间(

sic! )。 尽管英特尔最初是EUV光刻的发起者之一,但它却成为EUV光刻的主要对手。 他们意识到所有可能的东西都从193 nm UVI中挤出来,于是他们宣布过渡到126 nm(哈哈!)。

拒绝的原因是什么?事实是13.5 nm实际上已经是X射线辐射。 通常认为UVI和X射线之间的边界为10 nm,但是紫外线在13.5 nm的行为方面与软X射线没有区别。 因此,EUV光刻技术更像X射线。 这种波长的透镜在自然界中

是不存在的,因此,有必要从金属的异质层切换到反射镜。

除了产生非常薄和复杂的结构外,金属镜还吸收大部分辐射。 初始辐射功率的百分比单位到达光刻胶。 如果我们考虑到发射器本身的效率也只有百分之几,那么要获得正常的曝光时间,就

需要高功率和高能耗(

糟糕! )。

这是ASML EUV扫描仪

这是ASML EUV扫描仪辐射源是等离子体。 非常易变的物质,很难从中获得均匀的流动而没有脉动。 即使空气也能主动吸收13.5 nm,因此只能在真空中进行曝光。

光致抗蚀剂的选择问题。 波长越短,光子能量越高。 以前的能源以电子伏特为单位提供能量,这是化学反应的通常能量。 13.5 nm波的光子能量为92电子伏特。 这是深电子的结合能。 吸收了这样的光子,电子变得非常“热”,开始涌动,辐射出多余的能量,并导致远离窗口的二次曝光。 因此,选择具有所需参数集的光致抗蚀剂也是困难的任务。

电子在硅中以20和5 eV的能量运动的蒙特卡洛模拟结果。 来源

电子在硅中以20和5 eV的能量运动的蒙特卡洛模拟结果。 来源这些困难决定了他们将过渡到EUV的时间推迟到最后的原因。

对抗衍射的实际方法

因此,直到最近,波长为193 nm的相同UVI仍被用作辐射源。 高达10 nm和7 nm的技术。 现在我们回想起,如果辐射线的宽度小于波长的四分之一,则辐射无法穿透该间隙。 对于193nm是48nm。 问题来了-

怎么办?!这是工程师所做的小奇迹。 他们使用了辐射偏振法。

我们采取一个矩形的窄缝隙(宽度小于波长的四分之一),将光引导向它,沿着轴偏振。 光将穿过间隙;即使横向衍射也可以忽略不计。

现在我们有2个垂直插槽:水平和垂直。 首先,我们通过垂直缝隙,然后通过水平缝隙,用偏振光照射两组分光致抗蚀剂。 仅出现被辐照2次的区域。 就像所有的巧妙。

没错,您将不得不使用2倍的照片模板和2个曝光过程来创建一个窗口。 但是,您可以使用多年的老式石英光学器件和经过验证的光刻胶。

这是一个转折!还有其他方法可以抵抗衍射...

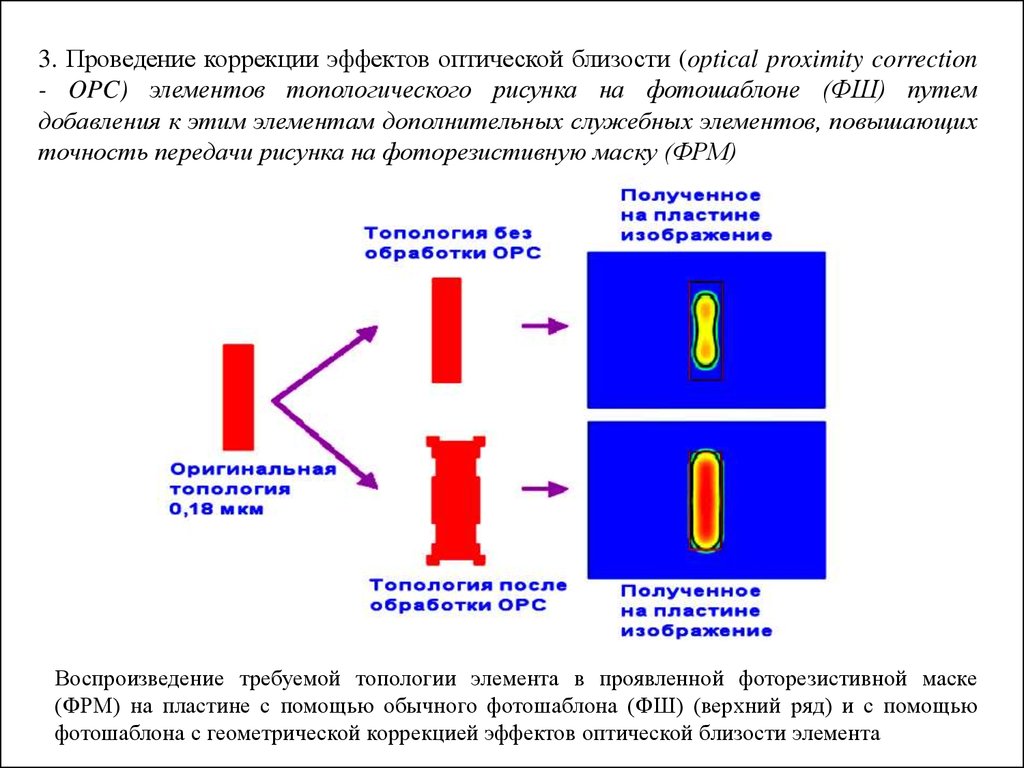

光学邻近校正。 使光掩模的窗口的形状为非矩形以补偿衍射期间的缺陷。

光学邻近校正方法原理图...

使用相移掩模。 在光掩模主窗口的侧面上做辅助,辅助材料的材料会改变波的相位。 施加波(

干扰 )后,它们会部分地相互抵消横向位移。

离轴照明。

离轴照明。 光束不垂直于平板表面落下,而是从两个源以微小角度落下。 在施加光源时,横向位移会得到部分补偿。

多重曝光。 例如,我们需要对附近的六个窗户进行曝光。 首先,我们驱动1、3和5个窗口的曝光。 然后是2、4和6。这将曝光周期和照片模板的数量增加了2倍,但总比没有好。 给定水平和垂直极化,我们得到4个曝光周期来创建一层。

因此,如果我们看看现代的光掩模,那么我们将看不到显式形式的微电路区域。 将有一组水平和垂直图形,叠加后将给出图片。 实际上,中文字符扎实:也许这就是为什么中国人占领微电子产品的原因?!

45 nm之后,他们切换到浸没式光刻。 这是当极端透镜和光致抗蚀剂之间的空间充满液体时。 起初是水。 现在,具有高折射率(高达1.8)的特殊流体。 液体会降低有效波长,并中和介质界面处的光折射。

这就是它们达到〜10 nm分辨率的方式。 但这似乎是193 nm光刻的极限。

用于24 nm技术的第一个金属化层的照片。 左侧是通过193 nm光刻技术创建的,右侧是实验13.5 nm(EUV)。 如您所见,从以前的透明矩形形状来看,只有记忆。 仍然有效。

用于24 nm技术的第一个金属化层的照片。 左侧是通过193 nm光刻技术创建的,右侧是实验13.5 nm(EUV)。 如您所见,从以前的透明矩形形状来看,只有记忆。 仍然有效。关于物理限制,它们如何影响以及如何

在第二天的第二部分中改变产量-请继续关注!

不要忘记订阅

博客 :这对您来说并不困难-我很高兴!

是的,请写出PM中文本中指出的缺点。