在异步科学中,核心位置是电路的特性,即速度独立性,在英语中是速度独立性(以下简称SI)。 据信,该特性是异步电路与逻辑元件的延迟的独立性的模拟。 毫不奇怪,几乎在所有异步工作中都提到了术语SI。 但是定期对此术语会产生一些模糊的疑问。 这个术语越来越多地被另一个称为自同步的术语代替,这并非巧合。 对消息来源的上诉将有助于澄清这种情况。 我们正在谈论的

是R. Miller的《开关电路理论》一书的

第二卷,或者更确切地说,是第10章,称为《开关电路理论,与速度无关》。

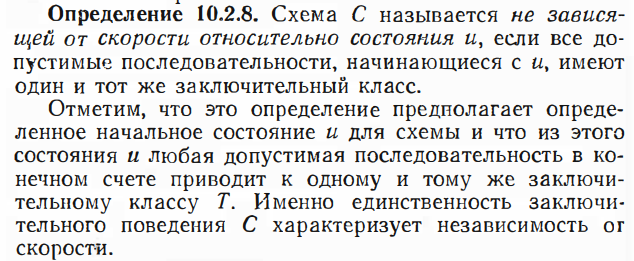

因此,这里是与速度无关的电路的定义。

类(等效性)是电路的一组允许状态的完整集合,因此对于该组中的任何状态,都存在一系列从给定状态开始并包含给定组的所有状态的允许状态序列。 换句话说,您可以从类的任何状态进入同一类的任何状态。

如果不可能从给定类的状态传递到属于另一个类的状态,则一个类(对等)是最终的。

例如,所有生活模式(行为)均与速度无关。 而且,它们不取决于电路的速度,电路的速度最终必定会停止,并且处于单一状态。

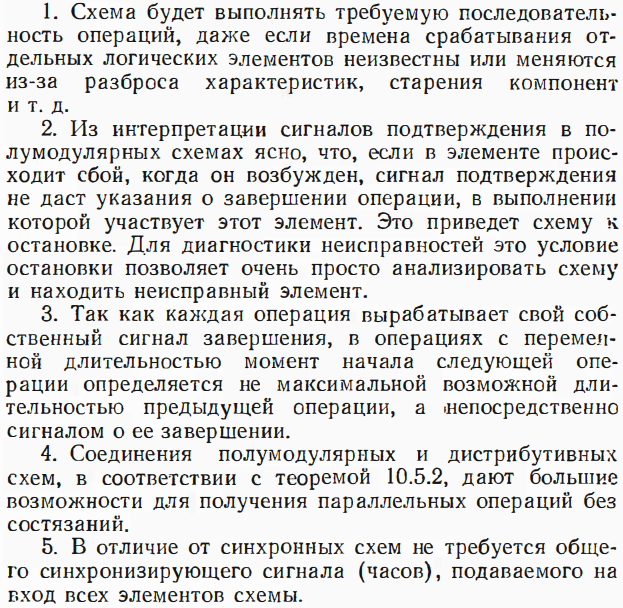

此外,作者一方面建立了SI方案之间的联系,另一方面建立了半模块化顺序分配方案。 最后,他列举了一系列电路的非凡特性,这些特性与速度无关。

第一点特别有趣。 只是说与速度无关的电路不依赖于逻辑元件的延迟。 不幸的是,案文没有明确说明得出这一结论的理由。 也许这就是后来对SI术语产生误解的原因。 实际上,这个结论是完全正确的。 在第10章开始时,作者提供了计算后续状态的规则。

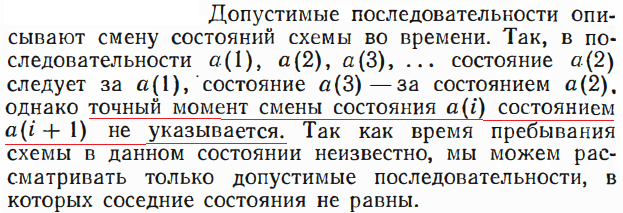

电路到下一状态的转换是切换某些逻辑元件的输出(或几个元件的输出)的结果。 即,在用于切换逻辑元件(激励)的条件的创建与其切换本身之间的时间间隔不受任何限制。 并且这样的时间段是逻辑元件的延迟。 即,从一开始,作者就从逻辑元件的延迟可以任意大的假设出发。 确实,下面的内容会写得更远。

好吧,为消除所有疑虑,请引用第10章第一页的内容。

因此,建立了一个无可争辩的事实:独立于逻辑元件的延迟不是电路的属性,而是研究该电路的模型的属性。 也就是说,以与R. Miller所述相同的方式研究的任何电路(SI或非SI)均与逻辑元件的延迟无关。 同时,可以在具有有限延迟的模型中研究任何电路。 在这种模型中,当在具有无限元素延迟的模型中考虑相同方案时,可允许状态集合是可允许状态集合的子集。 在检查具有有限元素延迟的模型中的电路时,电路可能与速度无关,并且同时取决于元素延迟。

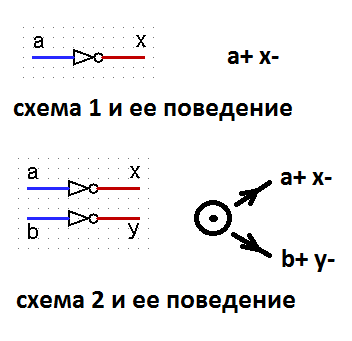

因此,事实证明,电路与逻辑元件的延迟的独立性与SI特性绝不相关。 那么问题就来了:引入对速度独立性的定义有什么意义? 实际上,请考虑两种模式及其行为。

输入两个电路的信号a,b,输出信号x,y。 两种方案都实现了完全合理的行为。 但是同时,电路1不依赖于速度,并且电路2不具有这种特性。 是的,我们可以说引入了SI的定义,而没有将信号分为输入和输出。 但是,这暗示了作者的这种信号分离,并且在文本中有关于此的评论。

仅结合半模量性质来揭示引入SI性质的定义的意义和合理性。 对于具有半模块化特性的电路,每个信号只能通过切换来消除其激励。 物理实现过程中的非半模块化方案充满了故障和亚稳态。 只有半模块化方案可以被认为是稳定的。

但是,半模块化性质与速度独立性之间的联系是单方面的。 也就是说,半模块化方案与速度无关,但是事实并非如此。 SI电路可能不是半模块化的。 即,根据稳定性真正重要的特性划分电路是半模块化。 重要的是要理解,如果我们在具有有限延迟的模型中考虑半模块化电路,则它们也可能取决于逻辑元件的延迟。

但这还不是全部。 还为自治电路定义了半模块化属性,即,不将信号分为输入和输出。 因此,自由选择方案(行为)不符合半模块化的标准。 同时,这些方案可以像半模块化一样稳定。 例如,以上方案2不是半模块化的,但是就稳定性而言,它绝不亚于方案1的半模块化。

摆脱这种僵局是有办法的。 本书J. Cortadella,M。Kishinevsky,A。Kondratyev,L。Lavagno,A。Yakovlev“异步控制器和接口的逻辑综合”定义了输出持久性(OP)属性的定义。

OP属性是将方案(行为)分为稳定状态和不稳定状态的实际属性。 应该是OP属性代替SI属性。 不应忘记,独立于逻辑元件的延迟是研究电路(行为)的模型的属性。 如果在有限延迟模型中考虑,OP电路也可能取决于元件延迟。

尽管以前有很多批评,但R. Miller并没有抱怨。 他的工作没有逻辑错误。 半个多世纪的错误归咎于误解R. Miller著作的读者。

最后,从上述内容得出的结论很令人愉快。 STG行为模型为逻辑元素提供了无限的延迟。 更改标记,提取真值表的规则是根据无限延迟元素的假设制定的。 因此,通过使用STG(使用真值表或直接使用图形)计算逻辑功能而获得的任何电路显然都与逻辑元件的延迟无关。 的确,必须理解,对生成的方案进行进一步的操作可能会导致这种宝贵质量的损失。