与查尔斯·韦瑟利(Charles Weatherly)的早餐持续了四个小时。 最后,女服务员从帕洛阿尔托的一家餐厅问我们,说餐厅排队很长,我们从早上八点开始坐在这里。 在这段时间里,我们讨论了很多有趣的事情:Charles在Livermore Lab和Oracle中的工作,面向对象和函数式编程,编译器和硬件描述语言,处理器的书签,神经网络的效率低下以及令人遗忘的Prolog,Charles到俄罗斯访问,使用状态机进行文本处理学童在硬件协处理器中进行开发,并在FPGA上创建视频游戏。

查尔斯·韦瑟利(Charles Weatherly)的四个小时的内容足以在哈布雷(Habré)上发表五十篇文章,因此,我将主要列出主题,此后,我将提供其中三个主题的一些细节:

- 面向对象和函数式编程。 单项赋值,函数值,摆脱突变,摆脱时机。

- 数据结构和编译器算法。 Muchnik SSA和有关优化的书。 Bob Morgan(Compass)构建优化编译器。 向量化编译器和Randy Allen(关于其他公司的我的Wave同事和Charles同事)。

- 在Synopsys中,Yacc解析器,Ada语言内部(DIANA)和VHDL前端的发展。

- 在我看来,定语语法在MIPT编程语言实施理论(TRNP)培训手册中的使用不成功。

- JOVIAL编程语言和Ada标准化。 IDL语言。

- 在Livermore计算实验室为CDC 7600和Cray-1上的物理学家和化学家编程。 Livermore Fortran是Fortran-77的扩展,具有结构和动态内存分配。 微缩胶片的使用,包括自动搜索和动画制作。 哈里·尼尔森 以及魔方魔方是如何在进入实验室之前就进入实验室的。

- 苏联克隆Cray-1 Electronics SS BIS。 IPM中的Fortran编译器和我们在MIPT上工作的C编译器。

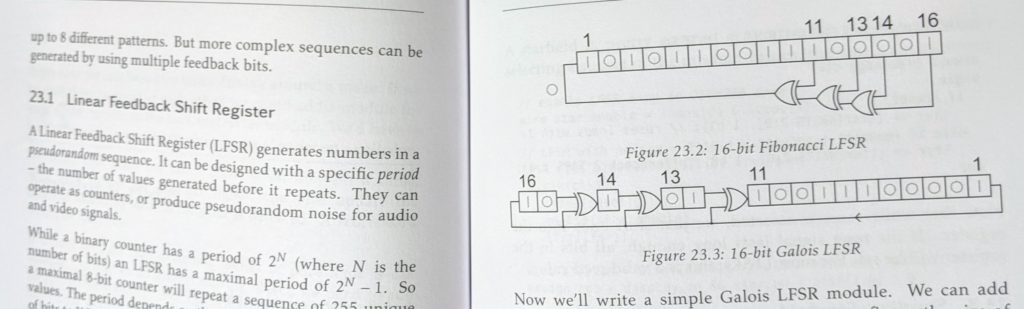

- 在Synopsys VCS中对随机数生成器进行反向工程。 带寄存器移位的同余生成器。 LSFR。

- 神经网络效率低下和被人们遗忘的Prolog语言。

- 应用Prolog中的方法进行程序文本的静态分析。

- 包括对用Verilog或VHDL编写的处理器代码的分析,以便在其中查找书签。 在寄存器传输级别分散在处理器描述的不同部分中的书签。 查找“规范”之外的“冗余”代码。 例如,一个有限状态机正在等待关键字,对程序员可见的寄存器中的文本,然后处理器切换到特权模式。

- 混合代码分析方法-动态执行,并从某个执行点对状态空间进行后续静态调查。

- 麻省理工学院的Hakmem列表。

- 生活中的大多数程序员仅使用五种算法-快速排序,二进制搜索,哈希,列表插入和其他一些算法(AVL二进制树插入?)。

- 贝尔实验室的Unix troff的历史。

- Charles Wazerell在Oracle SQL上的工作。

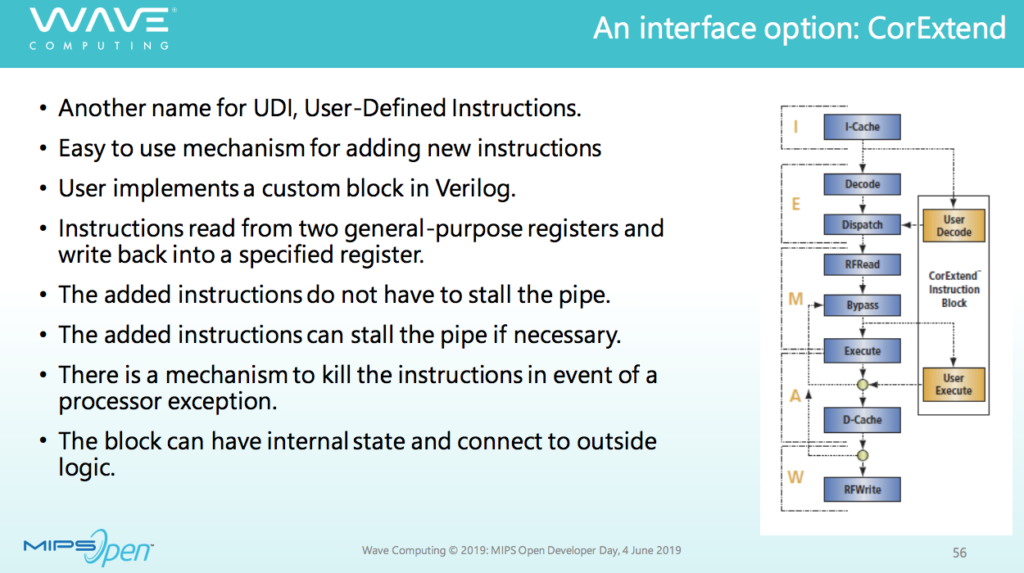

- 用户定义指令是将硬件协处理器用于MIPS CorExtend / UDI的一个很好的例子。 向协处理器内部添加状态机,并向处理器添加指令以进行快速词法分析,并保持各个指令之间的状态。 自IBM / 360转换测试和CDC STAR以来的背景知识。

- 在将机器学习算法应用于数据流之前,使用硬件协处理器预先清除数据流。

- Game Rogue,美国各州和苏联的《科学美国人》。

- 新西伯利亚暑期青年程序员学校和其中的蚊子(根据我的回忆和同事查尔斯·韦瑟利的故事)

- 查尔斯如何在莫斯科度过36个小时,在圣彼得堡度过两个星期。 冬宫。 在圣彼得堡大学,他没有讲课。

- 他建议查尔斯七月或秋天在其他地方(莫斯科州立大学?MIPT?ITMO?)去MIET / Zelenograd的一所暑期学校上学。

- 对学童和年轻学生的教育。 需要退出模板(例如,顺序编程)并在FPGA上学习Verilog是退出此类模板的一种方法。

- 在FPGA练习之前,使用集成度较小的微电路,以便小学生或学生直观地理解Verilog代码是对电子电路的描述,而不是程序(指令链)。

- 7月在MIET / Zelenograd暑期学校使用FPGA进行RTL的一个例子是一个自学习的有限状态机,它可以计算“石头剪刀”游戏中对手的动向。

- 另一个例子是有限状态机(动物)的竞争,这些有限状态机将玩家移动到地图(地球)上的目标。 地图上的物体有“气味”-正极(食物)或负极(可能撞击的电)。 使用扫描生成模块在FPGA中设计卡,VGA上的播放器输出和子画面。

在这里,我们研究了最近在哈布雷关于OOP的争议。 在适用的情况下,Charles致力于OOP和函数式编程。 我给Charles展示

了一个示例,我在两个

不成功的类设计项目中看到了

一个示例 ,这些项目

无法表示解析树的节点并对该树进行了优化 ,此后Charles说,当然,树变换算法不应以这种方式分散到小类中,而应使用快速抛出一个控制流程图,在该流程图上可以使用基于静态单项分配的表驱动转换,但有一些例外。 查尔斯启发了我关于Muchnik,Bob Morgan和Randy Allen的向量化:

然后我告诉查尔斯,后天我们将

在拉斯维加斯举行的一次电子设计自动化会议上举行研讨会 ,我需要他的建议,以基于CorExtend / UDI协议-用户定义的指令的协处理器的一个很好的例子为基础。 该协议用于MIPS内核。 CorExtend / UDI允许您在处理器中嵌入一个块,该块对主要系统指令进行解码并执行其他指令,这些指令可由系统设计人员在芯片上确定。 该模块可以合成并成为微电路的一部分,或者在FPGA / FPGA中进行配置。

附加指令与主要指令一起沿处理器管线移动。 它们从程序员可见的通用寄存器接收数据,并将结果返回到寄存器。 这些指令还可以将某些状态保存在协处理器中。 如果发生异常,它们可以被异常杀死,例如,在此指令之后的管道中:

后天,在

研讨会的

演讲中,我将使用一个带有简单卷积指令的神经网络示例。 但是在这种情况下所获得的加速效果并不令人印象深刻,只有两次。 有可能做一个更好的例子吗?

Charles立即想到了一个更好的例子:硬件词法分析。 可以在协处理器中放置状态机,该状态机将确定文本流中的数字,标识符和注释。 通过在将文本从寄存器传输到机器的各个命令之间存储状态,可以节省时间。 当前分析的结果(标记文本)也将返回到寄存器。

查尔斯还告诉我自IBM / 360转换测试和CDC STAR以来解析文本的说明。 他还告诉我,这样的协处理器可用于机器学习,在将机器学习算法应用于数据流之前预先清理数据流。

然后,我告诉查尔斯·萨加(Charles Saga),一群工程师和老师如何在俄罗斯各所大学中翻译和实施

戴维·哈里斯(David Harris)和莎拉·哈里斯(Sarah Harris)的

教科书“数字电路和计算机体系结构” (请参阅Habr。1,2,

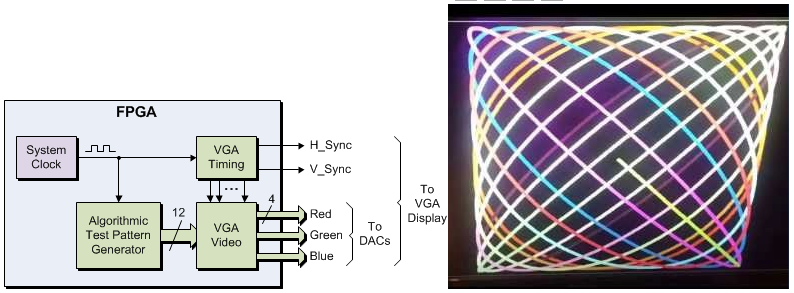

3)。 现在,在MIET,RUSNANO,MEPhI和其他大学的老师的共同努力下,我们计划在MIET开设一所暑期学校,在那里,高级学童将FPGA上的视频游戏投影到图形屏幕上(

物理与编程之间的章节)。 为此,使用了2018年12月15日Steven Hugg撰写的《在Verilog中设计视频游戏硬件的设计》一书中的想法:

游戏既可以以纯硬件有限状态机的形式开发,也可以以FPGA上的硬件图形与简单处理器核心schoolMIPS上的程序的组合开发,这

在Habr上的Stanislav Zhelnio的

帖子和

GitHub上schoolMIPS的

Wiki中进行了描述 。 在FPGA上,您可以非常简单地

生成VGA扫描 ,显示内存中的卡并移动带有图形的精灵:

查尔斯建议,除了使用坦克和种族进行的游戏外,还应进行有限自动机(动物)竞赛,将玩家移动到地图上的目标(地球)。 地图上的物体有“气味”-正极(食物)或负极(可能撞击的电)。 学生可以在查看环境的veril上编写有限的机器,将它们嵌入绘制图形和支持地图的代码中,然后与谁更富裕进行竞争:

要生成伪随机行为的元素,可以使用LFSR硬件块:

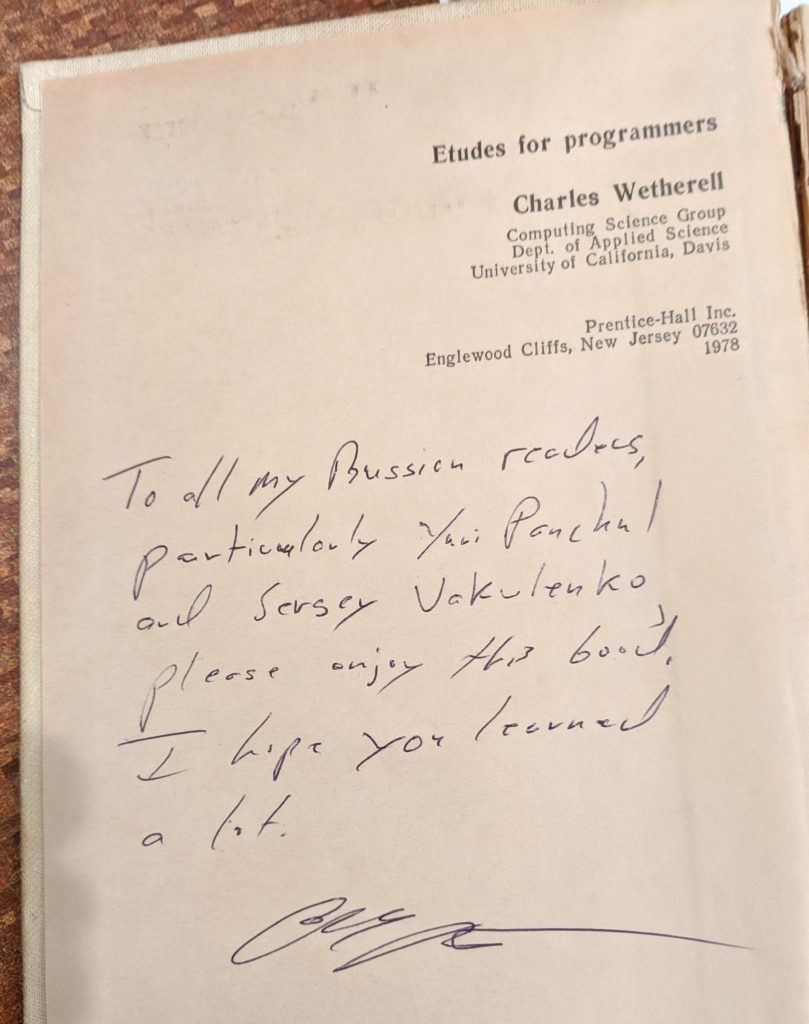

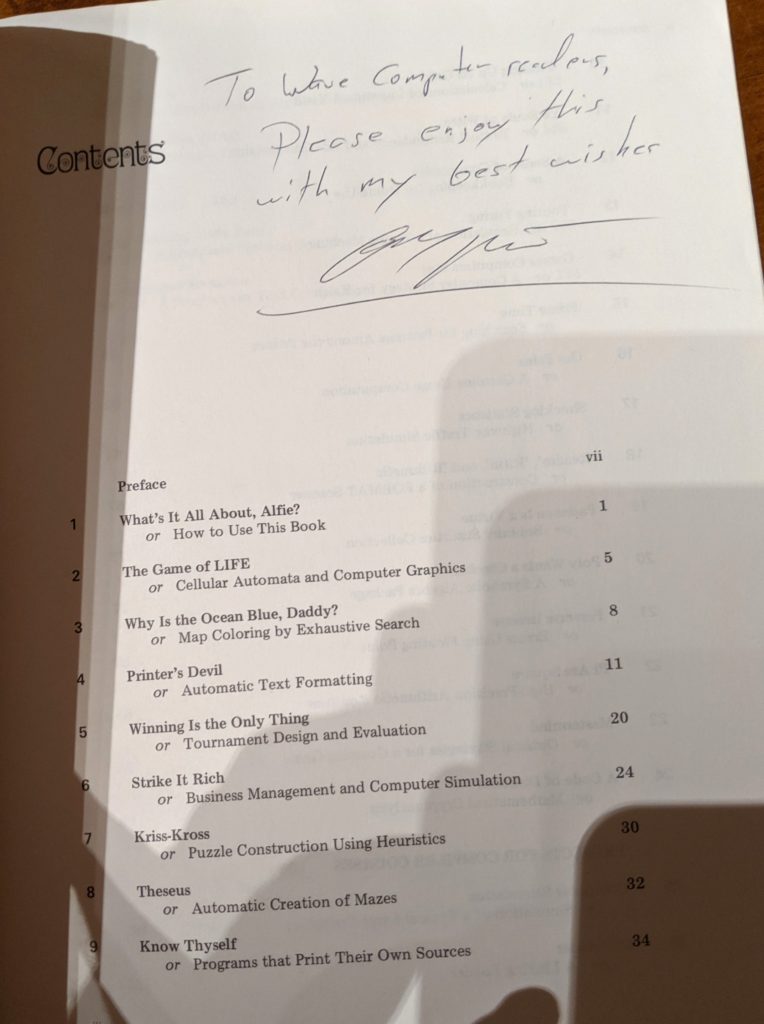

最后,查尔斯留下了两个亲笔签名-给俄罗斯读者(我从

Sergey Vakulenko借了俄语书)和我们公司Wave Computing的读者,我从其内部图书馆借了英文原版书: