在

第一部分中,我们简要介绍了硅物理,微电子技术和技术局限性。 现在,我们来讨论影响晶体管中元件尺寸的物理限制和物理效应。 其中有很多,所以让我们看一下主要的。 在这里,您必须进入物理学,否则就什么都不是。

免责声明:很久以前,我涉足撰写有关

芯片制造的文章,

在“ Inside Look”系列文章中,我什至查看了其中的内容,即 这个话题对我来说非常有趣。 自然,我希望原始文章

的作者将其发表在哈布雷(Habré)上,但出于就业方面的考虑,他允许我将其转移到这里。 不幸的是,Habr规则不允许直接复制粘贴,因此我添加了到源代码,图片的链接和一些插科打and,并尝试使文本更直一些。 是的,我了解并尊重非

生物学领域有关该主题的文章(第

1和第

2条 )。

微电子学中的物理效应

硅的基本数量顺序

晶体中硅原子的浓度为10

22 cm

-3室温下本征电子和空穴的浓度-10

10 cm

-3来自轻掺杂区的杂质原子浓度-10

16 -10

18 cm

-3来自重掺杂区的杂质原子的浓度-10

19 -10

20 cm

-3在非常重掺杂的区域中,杂质原子的浓度为10

21 cm

-3 。 在这种情况下,人们已经在谈论

退化的半导体 ,因为这种浓度(每10个或更少的硅原子一个杂质原子)会改变晶体的能量结构。

硅特性的温度依赖性

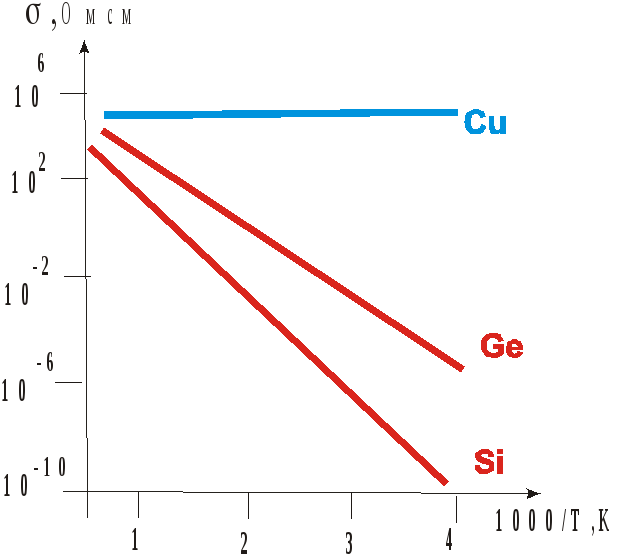

从第一部分开始,我们记得在室温下纯硅是一种电介质。 电子空穴对仅在万亿个案例中出现,但该分数随温度升高呈指数增长。 有这样的事情-使自己的电荷载流子浓度加倍的温度。 对于硅,约为9度。

即 将温度提高9度,硅原子衰变的百分比增加2倍。 18度-4倍; 27度-8倍; 36度-16倍; 45-32次; 90-1024次; 180-10

6次; 270-10

9次。

铜,硅和锗的热导率比较。 来源

铜,硅和锗的热导率比较。 来源我们得到的结果是,加热到200度(上图中的〜2.1)时,电子-空穴对的本征浓度变为10

16 ,这等于轻掺杂层的杂质浓度。 在300度(〜1.75)已经10

19时 ,这是重掺杂层(n +和p +)的浓度。 在此温度下,硅实际上变成了导体,晶体管失去了可控性。

问题将更早开始。 芯片中的温度不均匀。 通常在芯片中间有局部加热区。 如果小区域的温度超过200度,则由于硅的本征电导率增加,漏电流开始增加。 这导致更多的热量,并且进一步增加了泄漏电流并扩大了过热区域。 这个过程变得不可逆转并且蓬勃发展。 而且是不可挽回的。 因此,在所有大型微电路上,都设置了自动过热保护功能。

这就是为什么不允许强烈加热晶体如此重要的原因。

为了比较,在室温下的氮化镓中,本征电子和空穴的浓度低几个数量级,并且使本征载流子的数量加倍的温度约为25度。 氮化镓中的上述问题始于大约600-700度。

隧道电流

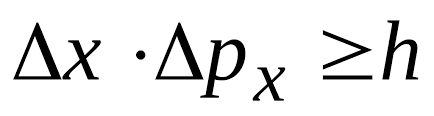

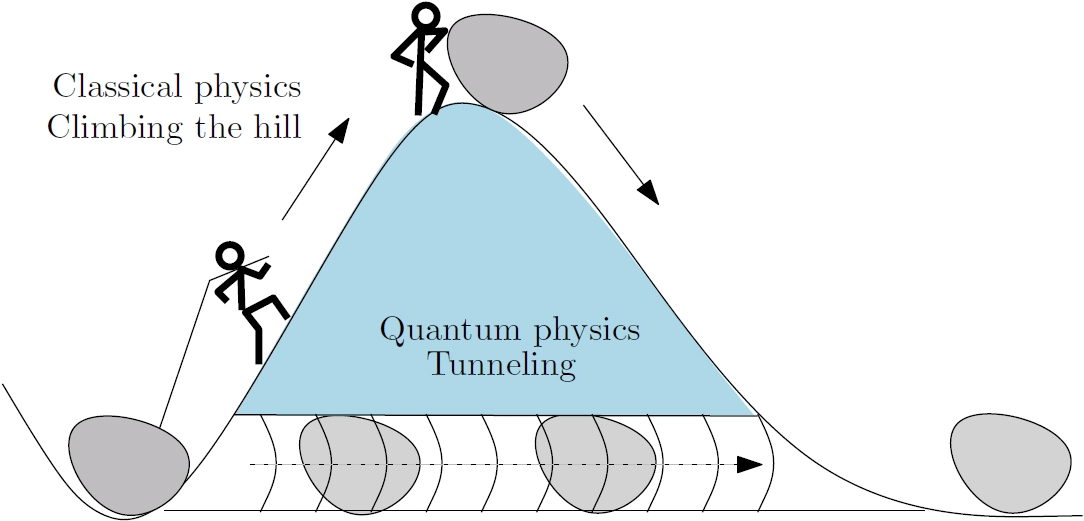

同时,这种现象既复杂又简单。 根源在于电子的量子性质。 电子受量子力学定律的影响,而从经典物理学的观点来看,这并不总是可以理解的。 根据这些定律,电子不仅是粒子,而且是波,其行为只能以一定概率来计算。 有一个这样的海森堡公式:

也称为

海森堡不确定性关系 。 由公式得出,不能以大于一定值(普朗克常数)的精度确定电子的空间参数。 在方程的极端情况下,如果我们知道电子的确切位置,我们将不会对它的速度和运动方向一无所知。 如果您确切地知道速度和方向,那么对他的下落一无所知。 事实证明,电子就是这样一种粒子,它在空间中具有存在概率峰值的模糊。 在任何时候,电子都可以在宇宙中的任何地方而不受任何外部影响。 的确,它出现的可能性与当前位置相去甚远,而这种可能性很小。

现在想象一下金属-电介质-半导体n型(MIS)的结构。 在金属中,自由电子的浓度大约等于原子的浓度(10

22 / cm

3 )。 它们不能渗透到电介质中,因为对于来自金属的电子来说,这是一个禁能区域。 在电介质内部,像金属一样具有能量的电子波将开始干涉(自身破坏)。 但是它们可以在n型半导体中实现,在该半导体中,存在一个允许能量的区域。 电子仅仅由于其概率性质,就通过氧化物层从金属传递到半导体而没有任何外部影响。 这是

隧道电流 。 该过程本身称为隧穿或量子隧穿(听起来更酷!)。

为了“经典”渗透到氧化物中而必须添加到电子中的额外能量称为势垒。 示意地,电子咬穿穿过势垒的隧道。

有相反方向的流动-从半导体到金属。 但是,由于半导体中自由电子的浓度要低几个数量级,因此逆流成比例地变小。

用于金属电子的p型半导体也是禁带。 但是,在这里可以进行相反的处理-价电子从半导体到金属的隧穿,并在硅中出现空穴。 看来孔是从金属中挖出来的。 在其他条件相同的情况下,该强度比自由电子的隧穿大约低十倍。

距离大于1μm的隧道电流可以忽略不计。 可能性太低,过渡太少见。 随着距离的减小,自发跃迁的可能性急剧增加。 在单位为nm的距离处,接近0.2 nm时,隧道电流增长10倍。

类似的机制适用于npn硅层。 对于来自n区域的自由电子,p区域是禁能带,不会发生跃迁。 但是,如果将p基极的宽度设置得太窄,电子将开始直接从源极传输到吸收极。 这将理论最大基极宽度限制为8 nm。 在较小的尺寸下,由于隧穿电流,源-漏晶体管原则上变得不可控。

对于pnp结构,情况类似,但空穴(价电子)隧穿。

在禁能带中的退化半导体(重掺杂)中,存在允许能量的孤岛。 对于他们来说,可以选择通过这些岛进行隧道建设。 关于如何通过跳上巨石来克服溪流。

空间电荷区(SCR)

空间电荷区域(SCR),它也是一个耗尽区域,它也是空间电荷区域,是在n和p区域的边界处形成的带电层。

轻轻地连接2个硅片,一个是n型,另一个是p型。 在n层中有许多自由电子,在p层中有许多空穴;它们随机移动。 部分自由电子进入p层,部分空穴进入n层。 结果,未补偿的正离子保留在n层中,而负离子在p层中未被补偿。 沿区域边界出现局部电场,开始阻止进一步的跃迁。 场强在边界处最大,并随距离逐渐减小。 最后,场强变成使得空穴和电子的传输停止并且建立平衡状态。 对于硅,这种内部场的电压约为0.5伏。 取决于两侧的杂质浓度。 依赖性很弱,浓度变化10倍时约为0.1伏。

除了在边界处出现电场外,自由电子和空穴的浓度也降低了。 直接在层的边界处为零。 因此,第二个名字-“枯竭地区”。 该区域的宽度取决于过渡电压和杂质浓度。 对杂质浓度的依赖性是反二次的,即 当浓度增加100倍时,SCR的宽度减小10倍(实际上,由于结处的电压增加,所以宽度稍小)。

这是不向结构施加外部电压的状态。

如果施加外部电压,则将其与内部向量化。

我们向结点施加一个小的正向电压,即 加号(+)到p层,减号(-)到n层。 内部和外部磁场指向不同的方向,并开始相互补偿。 减小了过渡电压和SCR宽度。 当外部磁场的电压高于内部电压时,SCR消失,pn结完全打开。 对于半导体二极管,甚至有这样一个参数-阈值电压。 这是二极管完全断开时的正向电压。

现在,施加反向电压:对p层施加负(-),对n层施加正(+)。 外部和内部磁场加在一起,结点的电压和SCR的宽度增加。

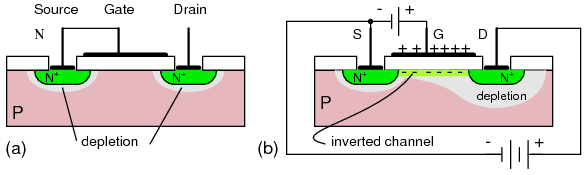

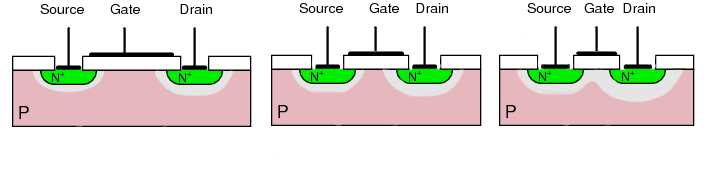

如果我们将此模型转移到我们的场效应晶体管,则会得到下图:

浅粉红色表示耗尽区域(SCR)。 我们得到由栅极电压控制的

有源基极的实际宽度小于源极-漏极距离。 也就是说,基极的大小减去SCR过渡的宽度。 在没有电源电压的情况下,源极和漏极的SCR宽度相同。 如果施加工作电压,则漏极的SCR的宽度会增加,因为它处于反向偏置状态。 活跃的基础正在进一步缩小:

如果基极太短,则漏极和源极的SCR已连接。 有源基极的宽度变为0,直通电流从漏极流到源极,晶体管打开。 无论快门上的电压如何。 晶体管变得不可控。 这种作用称为“基础穿刺”(

注意: 正如 F376 正确指出的那样 ,很可能是我们所说的“基础穿刺”)。

当SCR没有关闭时,还有一个中间选择,但是从源到径流SCR边界的距离小于8 nm。 然后,在SCR中,电子开始从源中隧穿。 一旦进入SCR,它们就会被电场抛入漏极。 简而言之,一个相当大的隧道电流将从源极流到漏极。

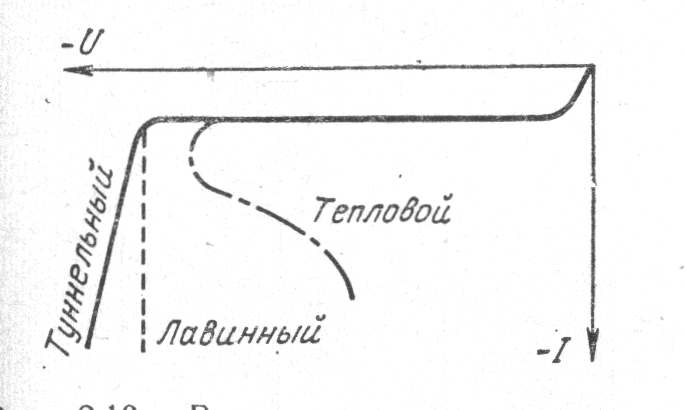

雪崩击穿

如果SCR内的电场变得太高,则意外飞入其中的电子会加速得如此之快,以至于它将电子从中性原子中去除。 出现2个电子,它们再次加速并从其后剥离电子,依此类推。 该过程类似于雪崩,因此得名。 导电通道出现在SCR中,电流流过该通道。 晶体管自发地打开。

栅极电介质中可能发生类似情况。 如果场强高于阈值,则从金属中飞出的“快速”电子会加速并引起雪崩。

清楚比较不同类型的故障。 来源

清楚比较不同类型的故障。 来源为了避免这种雪崩击穿,有必要防止超过击穿值的场强过大。 场强=应力/长度。 即 必须降低电压并增加SCR的宽度(或电介质的厚度)。

电阻面积

这已经是经典的电气工程。 漏极,源极,沟道,甚至导电金属走线都有自己的电阻。 电阻越高,图的长度越大,横截面积越小。

假设我们将晶体管的所有元件按比例减少2倍。 通过减小长度,该部分的电阻

减小了2倍 ,而通过减小宽度和高度将其

增大了4倍 。 总之,这使

元件的电阻增加了2倍 。 随着电流的通过,电阻会导致电压下降。 对于1 V及以下的晶体管电压,即使很小的压降也很关键。

对于金属化,这个问题可以简单地解决-第一窄金属层仅连接电池内部的元素。 其他所有东西都被带到了较高的金属化层:那里的氧化层更厚,走线更宽。 然而,接触窗和金属化轨道的尺寸不能无限减小。

对于硅面积,电阻的增加被杂质浓度的增加所补偿。 至少直到最近,直到隧道效应和击穿效应开始影响。

另一种方法是“拉伸硅”或“应变硅”技术。 其本质是在硅衬底上沉积一层锗。 锗是与硅相同族的元素,晶体结构相似。 然而,锗原子分别更大,它们在晶格中的距离更大。 然后,在锗上形成外延硅薄膜。 薄膜中的硅开始重复锗的晶体结构,晶格中的台阶将不仅存在于锗中,而且也将出现在普通硅中。 事实证明,硅在所有方向上都是一样的。 因此得名。 这增加了电子和空穴的迁移率。

物理效应的综合效应

现在一起考虑这些效果的效果。

晶体管小型化的主要威胁是穿刺基础。 要删除它,您需要减小SCR的宽度。 可以通过减少外部应力和增加碱中杂质的浓度来降低它。

电源电压无处降低,它已经在1V的范围内-大约两个阈值。 如果做得更少,那么由于电阻,我们就有冒着“糊状”打开晶体管的风险。

您可以增加数据库中杂质的浓度,但是我们得到:

- 从漏极到基极的隧穿漏电流急剧增加;

- 发生雪崩分解的风险增加;

- 增加了用于感应沟道的电压阈值,并有导致栅极电介质击穿的风险。

由于这些限制,

碱中杂质的

浓度固定为10 18 -10 19 。

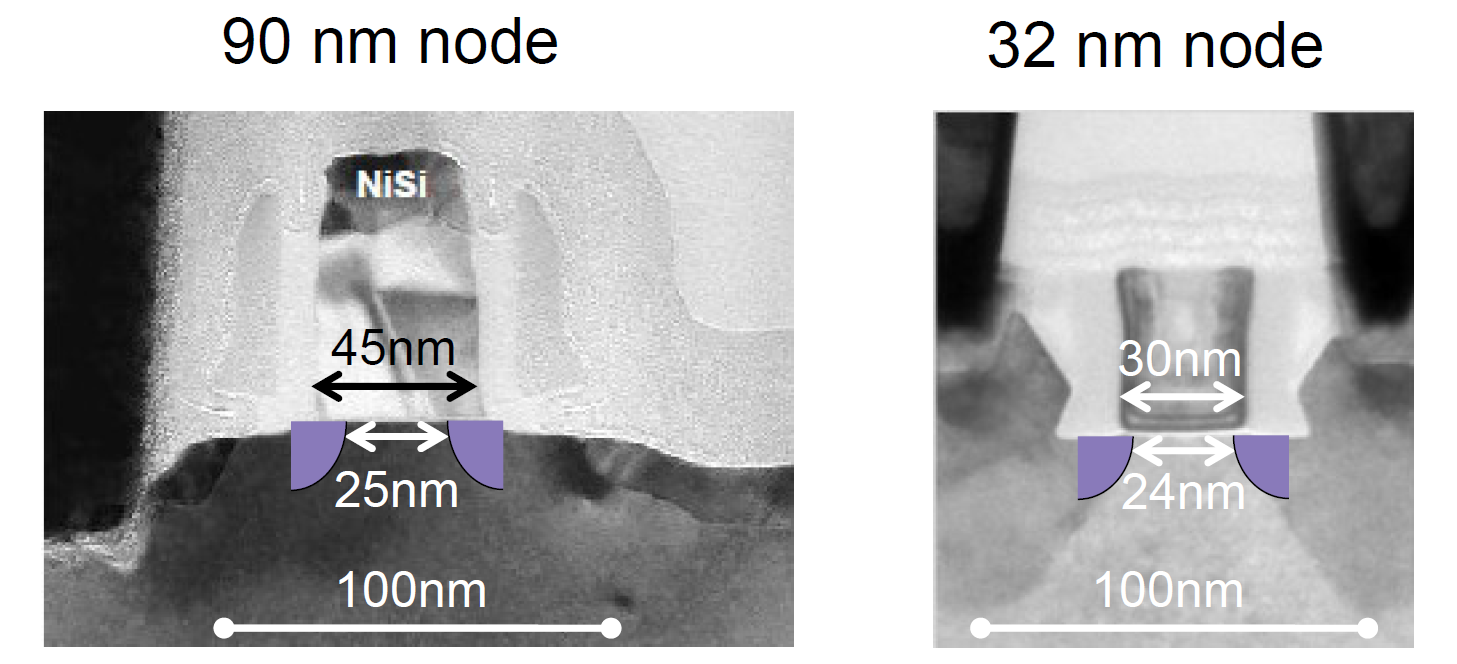

所有这些因素和未提及的因素将

硅MOS晶体管的

最小基极宽度限制在

25 nm左右 。 可能少一些,但泄漏电流不足,并且故障的可能性呈指数增长。

使用90 nm和32 nm工艺技术制造的晶体管的显微照片。 缩放和比例相同。 来源

使用90 nm和32 nm工艺技术制造的晶体管的显微照片。 缩放和比例相同。 来源可以看到,金属触点的尺寸已经变小了,但是底座的宽度没有改变。 都相同的25 nm。 而且,对于使用14 nm,10 nm和7 nm技术的晶体管,它是相同的(

糟糕! )。

从130 nm移至最初的90 nm系列时,首次遇到这种情况。 然后,他们第一次无法与其他所有尺寸成比例地减小底座的宽度,但仍保持约35 nm。 后来,它仍然减小到25 nm,但是从那时起,基座的宽度不再受技术的限制。 晶体管越小,这种现象越明显。

有必要更改技术流程的标准。 你干了什么 大多数人什么也没做。 他们继续颁发光刻许可作为工艺流程的规范。 或将金属化路径的最小宽度表示为最简单直观的操作。 然后我们继续进行营销...

最具创意的营销人员来自英特尔。 他们开始根据元素的大小来计算技术处理速度,例如,基于静态存储器的六晶体管单元的面积。 在具有65 nm光刻分辨率的技术中,该分辨率为0.77μm2,在40 nm分辨率下为0.37μm2。 如果像以前一样按比例减小晶体管的尺寸,则相当于45 nm技术。 因此,我们假设我们拥有45 nm技术。 这就是Intel技术与其他技术之间的差异的出处-全部为28 nm,英特尔为32 nm; 全部20纳米,英特尔22纳米; 全部为10 nm,英特尔为14 nm。

如后来的历史所示,英特尔最终比竞争对手更诚实。

漏电流的影响

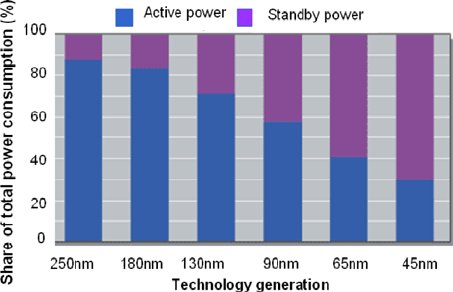

2010年已有一篇文章提供了精彩的时间表:

来源

来源该图显示了工作和杂散能耗的百分比。 蓝色-充电电流(工作电流)释放能量,紫色-泄漏电流(杂散电流)释放。 这是考虑到已采取的减少杂散电流的措施。

处理器时钟速度停止增长的原因显而易见。 3 GHz的第一批处理器(例如

Pentium 4 )出现在2000年代初期。 所以在这个水平上留下来。 通常,这可以通过以下事实来解释:内核数增加了,逻辑变得更加复杂,流水线得到了加深,因此对千兆赫兹的稳定性(通常来说,幸福感)的要求越来越高。 部分正确。

但是!以前,他们以某种方式设法将所有这些因素与频率增加结合起来。事实是,随着晶体管尺寸的减小,出现了能量消耗的储备。例如,技术规范减少了2倍,晶体管的数量增加了4倍,每个晶体管的平均功耗减少了6-7倍。事实是,CMOS晶体管在切换时会消耗电流,并且晶体管数量的增加主要是由于高速缓存的增加。存储器晶体管的切换相对很少。因此,它们消耗的能量少于处理器的活动元素。这种差异使得可以在相同热量下提高时钟频率。在从180 nm到130 nm的范围内,漏电流会占用该增量。从那以后,尽管有很多花招,但它们并没有加分。全部吞噬了该死的象鼻虫吃的漏电流。例如,节能处理器不得不降低频率,甚至降到某个地方。如果消除了奇迹,那么对于45 nm技术,增加频率将获得三倍的余量。实际上,在2000年代,一个安静的压盖物发生了优先级的变化。以前,当务之急是减小晶体管的尺寸,现在是为了减少泄漏。关于泄漏控制技术

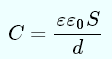

栅氧化层材料变化

随着切换到High-k,电介质还必须改变栅极材料。他们代替多晶硅,开始重新使用金属,通常是硅化镍NiSi。氧化硅仍用于与第二和另一金属化层分离。简要介绍高k电介质. . , . , , . – – .

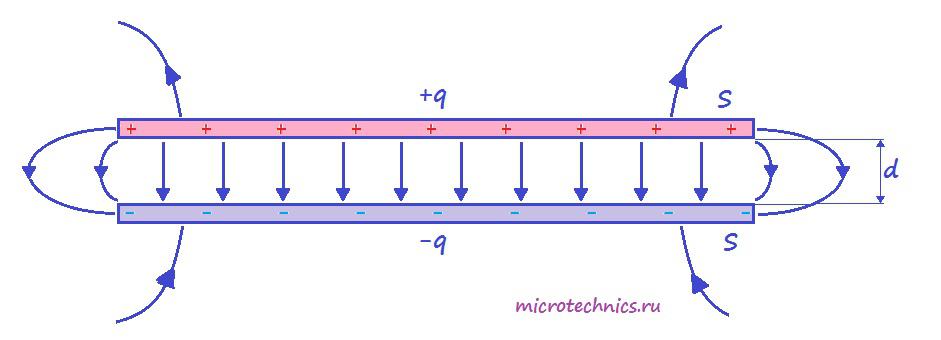

— . . , . . . :

S – ,

d – ,

ԑ – , 1, 1,

ԑ

0 – .

, . , . 1,2 (

sic! ). 6

(!!!) . . 5 , .. 1 , 10 (

!!! ) ( 10 0,2 ). .

– . — High-k . HfO

2 Ta

2 O

5 . 3.9, High-k 25-30. , , - .

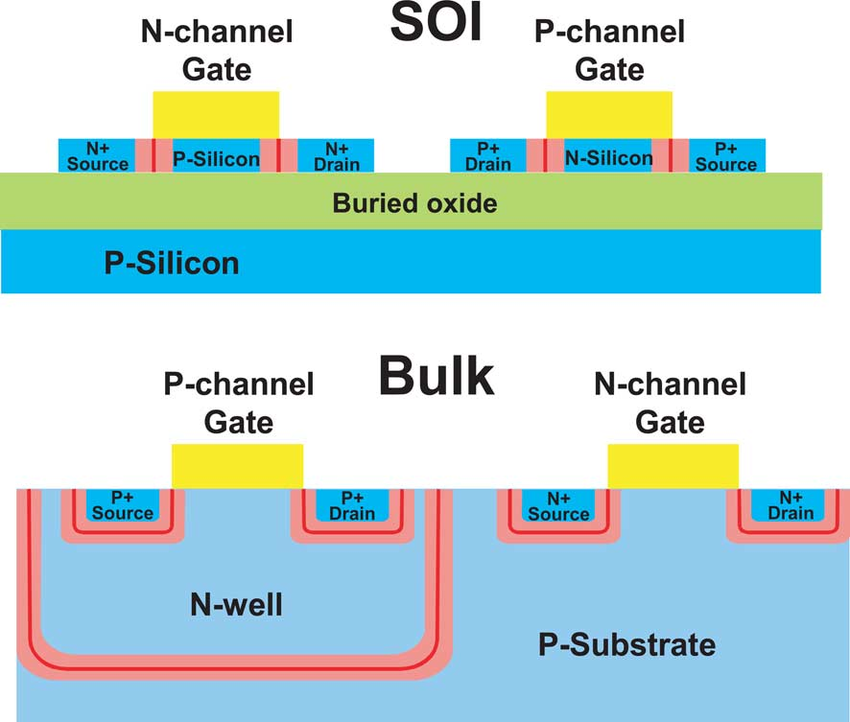

绝缘体上的硅(SOI)

绝缘体(又名SOI,又名SOI)上的硅技术以前曾用于隔离细胞。在这里,我们走得更远:在硅基板的顶部形成氧化层,并外延生长硅层(UPD:显然,作者在某种程度上简化了SIMOX和Smart Cut工艺)。 从原理上讲,SOI技术与常规平面MOS的区别在于该技术可显着降低泄漏电流。但是也有缺点。SOI技术仍然非常复杂且昂贵。另外,由于薄的隔离基极,存在足够数量的电子或空穴的积累以形成沟道的问题。通道很窄。另一个问题是散热。氧化硅的热导率低,并且难以从膜到基板的整体上散热。替代地,代替氧化硅,可以使用蓝宝石Al 2 O 3;其导热率更高。理想情况下,氧化物应位于漏极和源极下方,但不应位于基极下方。然后,结合High-k电介质,可以增加基极中的杂质浓度并将沟道宽度减小到15 nm。但是,尽管使用此技术受到限制。

从原理上讲,SOI技术与常规平面MOS的区别在于该技术可显着降低泄漏电流。但是也有缺点。SOI技术仍然非常复杂且昂贵。另外,由于薄的隔离基极,存在足够数量的电子或空穴的积累以形成沟道的问题。通道很窄。另一个问题是散热。氧化硅的热导率低,并且难以从膜到基板的整体上散热。替代地,代替氧化硅,可以使用蓝宝石Al 2 O 3;其导热率更高。理想情况下,氧化物应位于漏极和源极下方,但不应位于基极下方。然后,结合High-k电介质,可以增加基极中的杂质浓度并将沟道宽度减小到15 nm。但是,尽管使用此技术受到限制。FinFET晶体管

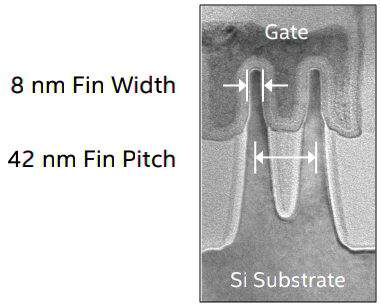

英文Fin的名字-鳍,冠。该技术首次用于22 nm技术,目前在处理器生产中占主导地位。底线是外延生长的不是氧化物顶部的完整硅层,而是区域中的各个脊清除了氧化物。UPD:从a5b到FinFET 的良好链接,最初蚀刻硅晶片以生产鳍片。像这样 来源

来源 与平面技术的原理图比较-晶体管变为三维。 来源该技术中的百叶窗从三个侧面围绕通道流动。当我们在栅极上施加电压时,它会从深处吸引电子(空穴)到脊的顶部,并在其中形成沟道。因此,漏极,源极和栅极的整个有源区都进入了脊,并且更深的电流泄漏到基板中的可能性很小。在这种情况下,脊不与基板热隔离,并且热量自由散发。通常使用两肋或三肋(三栅极)晶体管。在这样的尺寸下,制作如图所示的矩形脊是不现实的,其形状实际上是截锥。

与平面技术的原理图比较-晶体管变为三维。 来源该技术中的百叶窗从三个侧面围绕通道流动。当我们在栅极上施加电压时,它会从深处吸引电子(空穴)到脊的顶部,并在其中形成沟道。因此,漏极,源极和栅极的整个有源区都进入了脊,并且更深的电流泄漏到基板中的可能性很小。在这种情况下,脊不与基板热隔离,并且热量自由散发。通常使用两肋或三肋(三栅极)晶体管。在这样的尺寸下,制作如图所示的矩形脊是不现实的,其形状实际上是截锥。 来源

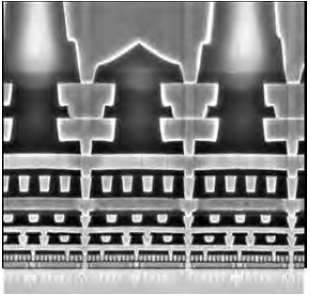

来源 相同的

相同的鸡蛋晶体管,顶视图。氧化物上方伸出的是纳米冰山的一角。脊的底部宽得多,在这里看不见。 来源下方是我们的CMOS晶体管。我们看到6个脊,n沟道3个,p沟道3个(图中用Fin表示),在栅极(Gate)的中间,沿着边缘有漏极和源极的接触。晶体管的尺寸取决于脊之间的距离,脊的数量,沟道宽度(均等于25 nm或更大),漏区和源区的大小。通过减小脊之间的台阶的可能性,光刻的分辨率对晶体管的尺寸间接地影响。例如,在22 nm技术中,脊之间的间距为54 nm,14 nm-42 nm,10 nm-34 nm。如您在这里看到的,没有线性相关性。现在,全球只有3家公司掌握了该技术。这些是美国英特尔,韩国三星和台湾台积电。甚至AMD的前女儿GlobalFoundries也退出了这一程序。AMD目前正在从台积电订购处理器,并已与三星达成协议。关于金属化的一点

一直试图将第一,最底层金属化层中的金属轨迹最小化。事实是,金属化路径与硅形成相同的平面金属-电介质-硅电容器。但是与快门不同,它是一个杂散电容器。在千兆赫频率处具有大电容时,可能会在不应该出现的地方发生杂散的电气通信。为了减少杂散电容,您需要减小走线的面积。因此,使第一金属化层中的迹线尽可能短和尽可能薄。出于相同的原因,他们尝试以直角重叠不同的金属化层-首先制作纵向轨道,然后再制作横向轨道。层越高,其下的氧化物越厚,轨道越宽。我为什么呢?由于第一金属轨道的厚度是最小的,因此通常被指示为工艺过程的规范。在FinFET技术中,脊之间的空间充满了氧化物。高k介电层,栅极,凸脊和波谷顶部的相当厚的层。将第一金属化层去除到槽上方的这些堵塞处。迹线本身应做得更宽以减少电阻并补偿凸起。即

最小的轨道宽度和实际情况也有所不同。 层压金属派

层压金属派即

过程标准越来越成为虚拟的数量。因此,我们有类似的处理器,其参数标有从7 nm到22 nm的标准。 FinFET的22 nm工艺使您能够获得两个凸脊,其中7个凸脊需要3个凸脊,因此,晶体管的尺寸大致相同。但是,杂志经常继续写道,随着从10 nm过渡到7 nm,晶体管的数量将增加1.8倍。人们仍然拥有摩尔时代的旧模式...接下来呢?向体积晶体管的过渡导致出现了许多有希望的修改。例如,三星宣布将GAAFET技术用于5nm技术。 CMOS,FinFET和GAAFET的比较显而易见。 来源

CMOS,FinFET和GAAFET的比较显而易见。 来源即

梳子不应是连续的,而应分为单独的线程。问题:这场比赛值得吗?-保持开放。UPD: 正如 F376 正确指出的那样,FinFet提供了来自两方的电场输入。全方位栅极FET可从各个方向进入,效率更高。还提供环形快门,垂直快门等选项。FinFET和SOI组合。通常,与光刻相比,外延的化学过程更复杂,但线性和可预测性更高。其提供用来为更高的精度和创造更微妙的三维结构的能力。微处理器制造商现代市场的状况和前景

因此,三个领导者脱颖而出-英特尔,三星和台积电。 英特尔以自己的品牌生产,其余的主要是按订单生产。 在AMD,NVIDIA,Qualcomm,Apple,IBM等品牌下,它们隐藏了台积电或三星工厂生产的芯片。 一些老领导人跌倒或遇到障碍。 中国人试图闯入大联盟,但到目前为止还不是很成功:他们缺乏自己的技术基础,设备生产的世界领导者为中国人保留了最新的技术路线。

专家的乐观与向整体结构的过渡以及EUV光刻技术的开始使用有关。 三星和台积电已经开始在有限的范围内将其用于最精致的结构。 这使他们有机会报告达到7纳米以及将来达到5纳米的标准。 尽管,如前所述,这些数字实际上影响不大。 相同的英特尔通常放弃了EUV。 显然,他们认为这样做不会大大提高性能。

另一方面,该主题的人们知道摩尔时代已经结束,生产力增长的每个新步骤都将需要更多的精力和时间。 微电子学的快速增长结束了(

so! )。 在汽车工业和航空领域,这是怎么发生的。 爆炸性增长之后,发展缓慢。

在有希望的突破点中,可以挑出向另一种材料(不是硅)的过渡以及多层微电路的创建(3D集成-向AMD的想法致意)。 对于3D集成,您将必须大大减少热量的产生或增强散热。

这就是晶体管尺寸的全部。 生产力增长还有其他储备。 以优化架构为例。 您甚至可以采取行销行动,说具有改进架构的新处理器的工作就像是采用0.5 nm技术的旧处理器一样。 因此,我们将其标记为0.5 nm。 与他一起无花果认为晶体管的尺寸是相同的。

可以通过晶体管的组合来创建新型的单元。 例如,代替6个晶体管存储单元,而是制作2个具有相互影响的复杂物理原理的晶体管结构。 这里的体积结构提供了很多机会。

物理极限

有人可能会说作者的悲观主义是没有道理的。 他们找到了解决限制的方法。 也许没有以前那么快,但是。

事实是仍然存在无法绕过的物理过程。 主要的是由原子组成的物质,电荷载体是电子。 创建小于原子的晶体管是行不通的。 创建少于1000个原子将不起作用。 因为存在电子与海森堡的不确定性关系。 电子是非常不稳定的粒子,只有成千上万个电子阵列才可能或多或少地具有稳定的行为。 在一个电子上,您只能消灭薛定ding猫。

注意:尽管单电子晶体管(

1、2和

3 )有所发展

即使在当前大小下,由于晶体管的自发操作也会发生冲突。 如果发生碰撞的可能性是10

-9 (十亿分之一),则以十亿个元素的数量和GHz的频率为单位,则平均每个周期1次碰撞,或每秒数十亿次碰撞。 为了捕获这些错误,有一些用于监视操作完整性的系统,并且发送了可疑操作以重新执行。

随着小型化,碰撞次数开始急剧增加。 结果,我们从小型化变成零影响甚至负面影响的情况。 即 晶体管制造得更少,它们更适合晶体,但是由于碰撞和后处理周期的增加,总生产率并未提高。 甚至跌倒了。 这个门槛即将出现。

关于家用数字微电子学的几句话

与普遍的看法相反,直到1985年,苏联与领导人的滞后并不那么大。 大约3-4年。 这就是如果我们采用Zelenograd的

领先企业(请注意:

BarsMonster当时 撰写了有关Micron

的文章 )。 根据摩尔定律,即使是3到4年的延迟也会极大地影响效果。 在获得具有pn结透明性的高质量氧化物时存在问题。 如果我们对外壳的芯片包装增加保守的政策(较长的接触线并不能提高设备的生产率),以及苏联用铁板生产纸板和外壳的标准(那些拆解苏联磁带录音机的人会理解的话),我们就会开玩笑说铸铁的苏联芯片提手。

积压的原因很多。 后期初产,有限的资源,喷涂资源。 当美国人专注于CMOS时,我们继续尝试各种技术。 他们与硅替代品(主要是A

3 B

5材料)合作非常积极。 好吧,已故苏联研究机构的全面放松。

1985年以后,美国人突然开始,我们开始遇到麻烦。 然后是1990年代,当时行业的生活因惯性而温暖。 结果,他们以800纳米技术进入了21世纪,当时领导者已经进入了130纳米技术领域。 卡的大规模芯片化和政府订单赋予了该行业第二个生命。 主要生产钢材:用于SIM卡,银行卡,支付卡,运输和折扣卡以及其他消费品的芯片。 那里不需要大的千兆赫和小纳米。

注意:顺便说一句,虽然在莫斯科时间只有一张票(买来的废品,装满了工厂),但在同一中国,他们正在积极推广节约资源的技术,尤其是在地铁上可重复使用的“令牌”(即使是短途旅行) 。

尽管如此,仍试图进入微电子的“大联盟”。 发展有四个主要方向。

- “主权”技术流程。 试图在家用设备和我们自己的技术流程上形成完整的生产周期。 我们遵循领导者20年前采取的相同方法,但要考虑发现的问题和解决方案。 在后者中,开源中的系列是250 nm,实施过程中是150 nm。 这还包括尝试在13.5 nm处创建我们自己的EUV光刻设备,如果不在大型联盟中,则立即退出,然后靠近它们。

- 从领先的制造商处购买技术线。 这里的问题是,即使在最佳年份,最现代化的装置也没有卖给我们。 通常,他们出售已停产的过时生产线。 现在,在制裁方面,更是如此。 在这里,我们可以回想起史诗般的历史,Angstrom在2007年购买了180纳米制造工艺的AMD德累斯顿工厂的设备。 或从法国意法半导体(STMicroelectronics)购买美光(Micron)90 nm系列产品,然后升级到65 nm。 尽管这是俄罗斯最薄的制造工艺,但他们还是在制裁之前抢了头。 没错,现在有一种解决方法-通过中国采购。

- 在中国或台湾的工厂订购生产。 同时,我们已经全面开发了架构和拓扑,

现在我们甚至可以制作自己的光罩 。 中国人只能在自己的工厂中复制技术流程。 我们获得了更先进的生产性处理器,并在最现代化的处理器系统的开发中发展了竞争力。 在这里,不是由库里宾的科学家组成,而是由大型设计团队组成。 只有最后一部分,即生产,才退出整个周期。

注意:贝加尔湖仅根据台积电工厂的28 nm标准制造。 关于贝加尔湖出口及其分析的文章。

- 替代技术的发展。 这是有前途的技术的发展,可能会在将来广泛使用。 这包括研究A 3 B 5化合物和异质结构,主要是砷化镓和氮化物。 以及尝试优化电子束和X射线光刻以进行批量生产,这通常消除了光刻的局限性。

注意:我们从已故的Alferov继承了关于异质结构的一门强大学派,但是即使有国家的支持, OptoGaN仍未能将其延伸 ,但市场和市场条件都在失败。

总体而言,俄罗斯微电子的情况并不乐观。 但是有希望的是,领导人由于身体上的限制而不可避免地会放慢脚步,而在这里,我们慢慢地匆匆前进,逐渐落后。

在接下来的几天中,关于记忆和机会之窗

的最后决定在几天之内-敬请期待!

不要忘记订阅

博客 :这对您来说并不困难-我很高兴!

是的,请写出PM中文本中指出的缺点。