让我们谈谈通孔的设计-对于严重的电子产品,通孔的质量非常重要。 在本文开头,我重点介绍了影响信号完整性的因素,然后展示了计算和调整单通孔和差分通孔阻抗的示例。

大家好,我叫Vyacheslav。 我从事印刷电路板的开发已有5年了,在这段时间里,我不仅阅读了很多有关跟踪的规则和建议,而且还找到了源代码并与之合作。

在YADRO正在开发的复杂计算系统中,从发送器到接收器的高速信号覆盖了相当长的距离,穿过了几块板并进行了数十次层间转换。 在这种情况下,每个粗心设计的通孔都会对信号衰减产生很小的影响,因此,该接口可能无法正常工作。

信号完整性

过孔(以下称为p / o,英文过孔)是传输线中的异质性。 像其他异质性一样,它们破坏了信号。 这种影响在低频时较弱,但随着频率增加而显着增加。 通常,开发人员几乎不必理会过孔的结构:它们可以从“相邻”项目中复制,从数据表中获取,也可以完全不用CAD指定(默认设置)。

在使用计算出的结构之前,有必要了解为什么要这样构造? 盲目重复只会造成伤害。

穿过通孔时通道中信号的完整性主要受以下因素影响:

- 波阻抗变化引起的信号反射;

- 由于杂散电容和电感导致信号劣化;

- 切换到内层时来自未使用的半塑料部分的反射(以下称为英文,通过存根(stub))

- 相声(英语相声);

- 干扰电源总线。

让我们更详细地考虑这些影响的原因以及消除这些影响的方法。

系数1.波阻抗p / o

在理想设计的电路板上,阻抗在整个路径过程中都不会改变,包括切换到另一层时。 实际上,它通常看起来像这样:

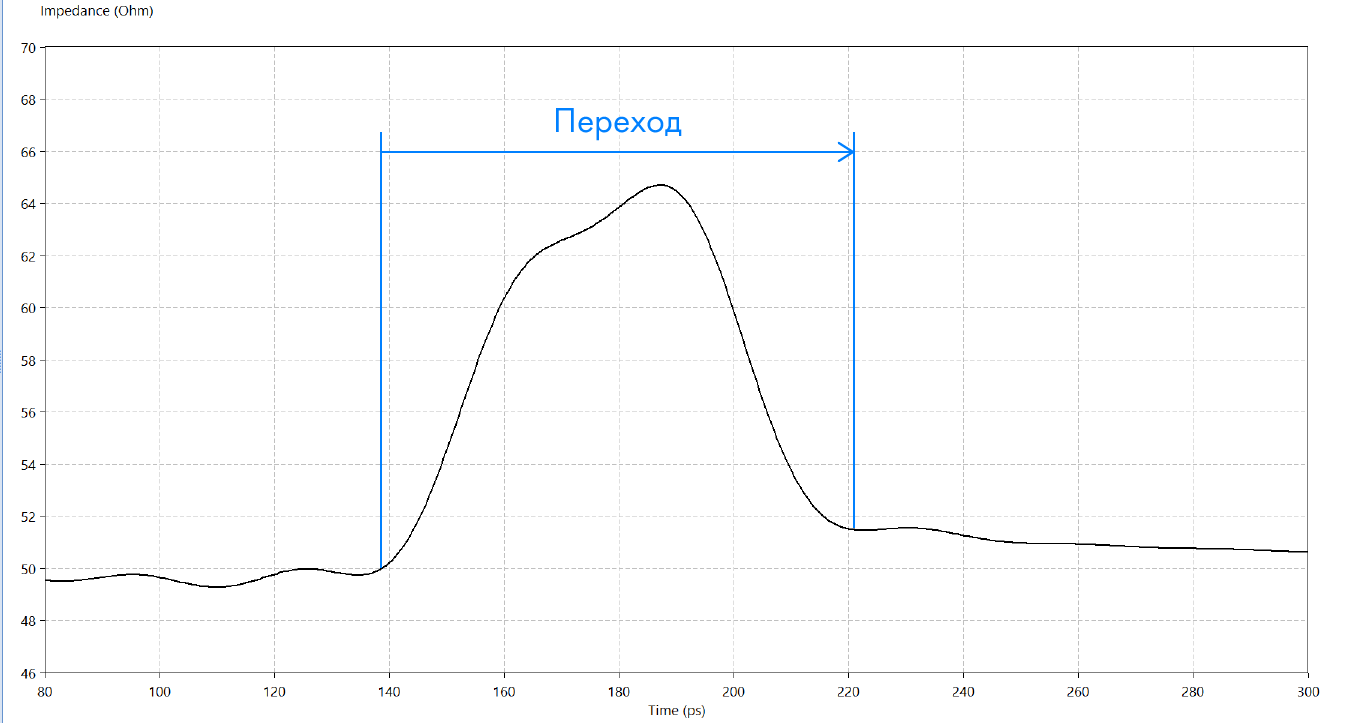

图1.过渡到另一层时的波阻抗变化。

图1.过渡到另一层时的波阻抗变化。匹配的波阻越好,信号反射越少。 如何影响呢?

考虑板上p / o的结构[1]。

图2.板上的p / o结构。

图2.板上的p / o结构。通过更改p / o元素,我们可以更改过渡的波阻。 我们的目标是使过渡结构的阻抗与导体的阻抗相匹配,以使反射最小化。 让我们考虑一下当p / o结构的元素改变时阻抗如何改变。

因子2。寄生电感和电容

印刷电路板上的导体可以制成宽范围的波阻,但通常为50欧姆。 一方面,这是由于历史上的连续性造成的:同轴电缆将50欧姆阻抗标准化,以平衡驱动器负载水平和信号能量损耗。 另一方面,在标准板上容易制成50欧姆的导体。

对于显影剂而言,重要的是波阻的具体值与其在整个传输线中的恒定性无关紧要。

为了使传输线具有固定的波阻抗值,显影剂选择轨道的宽度和到参考层的距离,即 将传输线的线性电容和电感更改为

某个值。

在p / o中,电感分量非常重要。 首先,我们必须在合理的框架内,尽可能减小杂散电感,然后更改p / o参数以获得

给定的电容,从而获得

给定的阻抗。

半波电容的过度减小将导致阻抗局部增加,并因此导致信号反射。

因素3。通过存根

当信号通过短截线通孔时会发生什么?

图3.带有短截线的过渡孔,在1/4波长处共振。

图3.带有短截线的过渡孔,在1/4波长处共振。在我们的示例中,信号从顶层从顶部传播到底部。 到达内部信号层后,信号被分离:一部分沿内部层的路径移动,一部分继续沿通孔向下移动,然后从底层反射出来。 反射信号到达内层后,再次分离,一部分沿路径移动,一部分返回源。

反射后的信号将与原始信号相加并使其失真,这将以眼图上的窗口变窄以及插入损耗(Eng。Insertion Loss)的增加来表示。

在最坏的情况下,TD段将等于信号波长的1/4,然后反射信号将以一半周期的延迟到达内层的路径,与原始信号反相重叠。

分析完整性时,建议考虑带宽为5奈奎斯特频率的带宽。 一个好的近似值可以被认为是可以接受的短截线,在7次谐波及以上时产生谐振[2]。

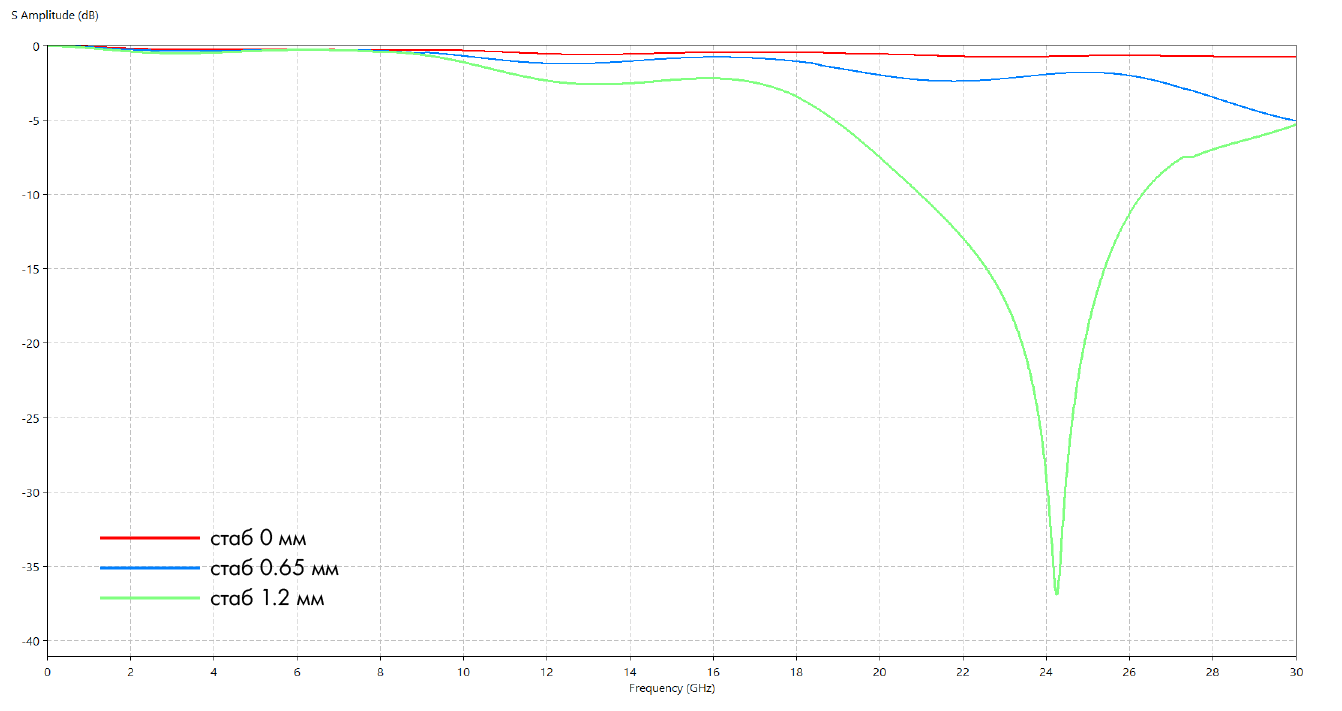

图4.存根为0、0.65、1.2 mm的p / o的插入损耗水平图。

图4.存根为0、0.65、1.2 mm的p / o的插入损耗水平图。图4显示了在24 GHz左右的频率下的巨大谐振。 我们可以得出结论,如果我们的信号工作在2-3 GHz的频率上,那么我们就无法消除短截线,因为在7个谐波之内“一切都很平静”。

您可以在

Polar计算器中快速评估存根

的重要性 :

图5.来自polarinstruments.com的图像。 对于上升时间超过500 ps的信号,短截线长度为2.5 mm是可以接受的。

图5.来自polarinstruments.com的图像。 对于上升时间超过500 ps的信号,短截线长度为2.5 mm是可以接受的。文献[2]中给出的公式得出的结果略为准确。 它们考虑了p / o几何形状,并允许计算沿Z轴的介电常数。

您可以使用“反向钻孔”操作(英语反向钻孔)或使用微转换(英语盲孔和埋孔)来消除存根。 选择取决于项目的功能。 反向钻孔更容易,更便宜。 在制造板之后,使用较大直径的钻头,将短桩钻到预定深度。 要求开发人员在钻孔区域中设置拓扑的其他缩进,并且制造商还可以在设计文档中指定钻孔要求。 现代CAD系统支持此功能。

微连接主要用于高密度板(英文HDI),但在某些情况下,可以通过拒绝拒绝追溯和减少板上层数的高昂成本来使用它们。 在开发HDI板时,需要牢记以下几点:

- 每种新的工资单都会增加董事会的成本;

- 对于激光钻孔,使用经过优化的特殊预浸料,其性能可能会有所不同。

- 盲孔的金属化增加了内层铜的厚度。

强烈建议事先与制造商商定板的结构。

因素4。串扰

串扰-从一条线到另一条线的有害信号传输。 之所以发生这种转移,是因为两个紧密间隔的导体具有电容性和电感性耦合。

信号导体和p / o的串扰性质稍有不同。

信号在n / a中没有参考层,返回电流沿相邻的n / a流动,形成一个大环路。 由于电感成分,n / a中信号的串扰。

通过增加p / o之间的距离,可以最大程度地减小串扰。 但是,拓扑学家通常没有太多空间。

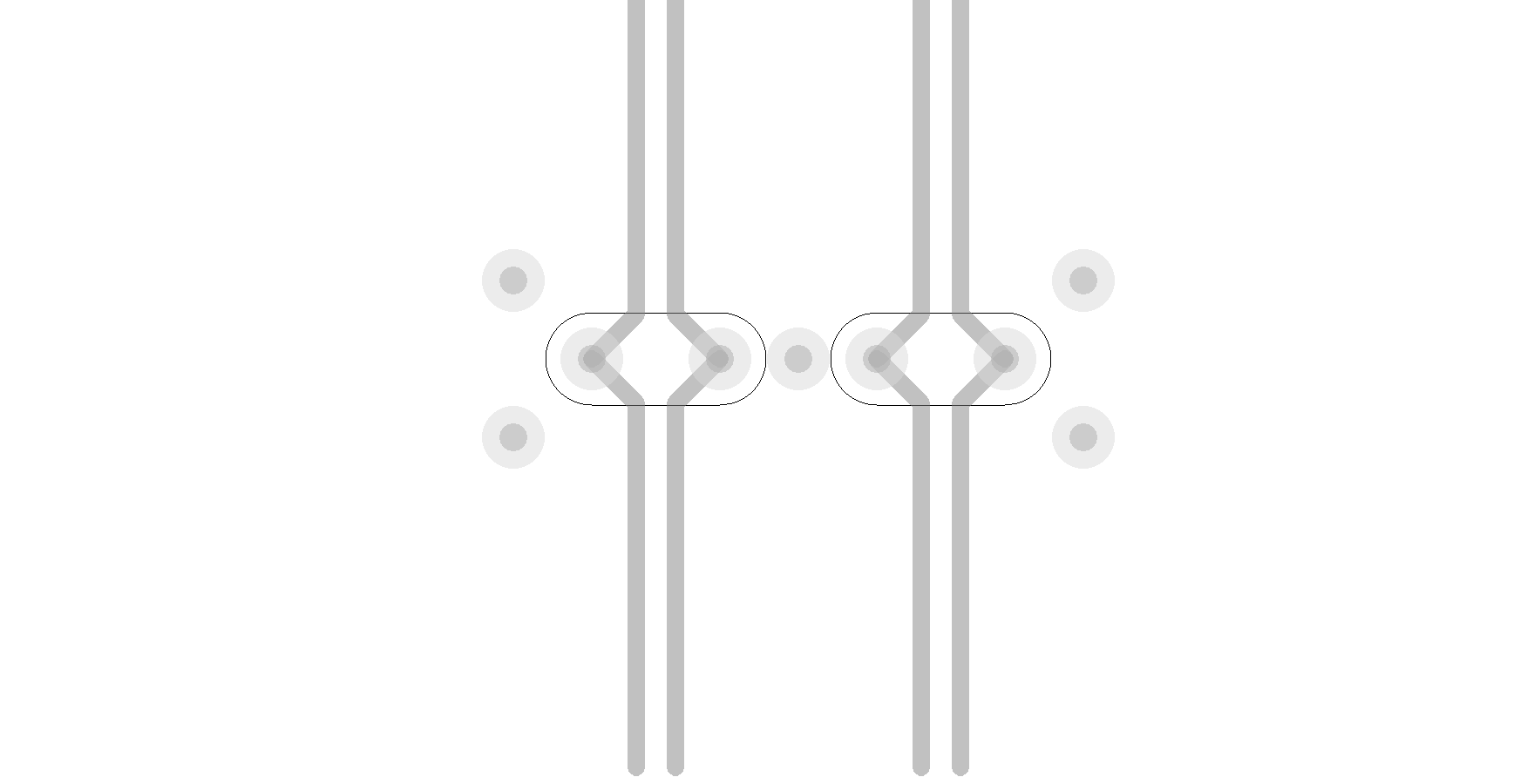

p / o在差分对中的收敛不仅减小了占用面积,而且对抗噪性有积极的影响[3]。

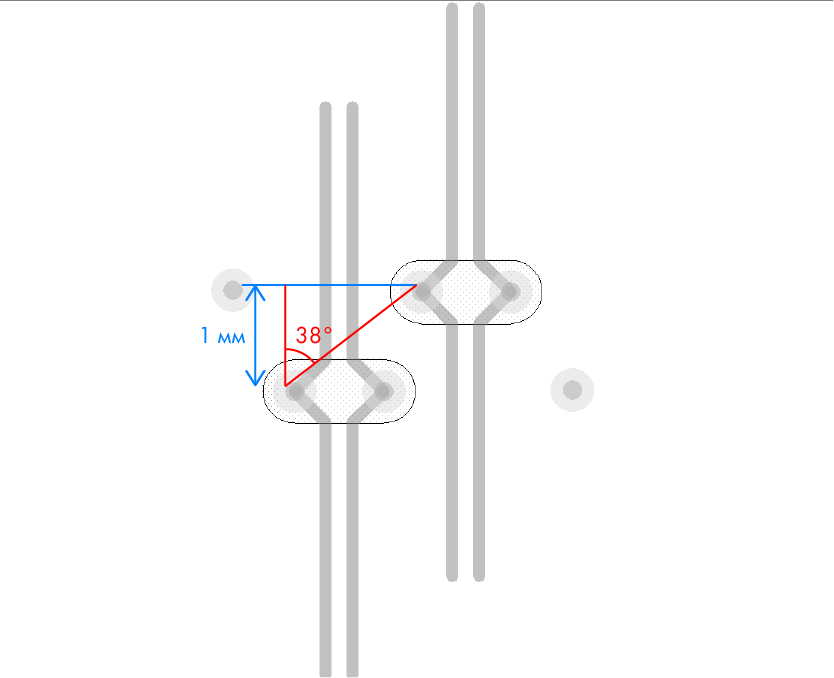

最小化相邻信号p / o之间的串扰的常用方法是在它们之间放置一个屏蔽p / o。 使用这种方法,有必要以大约2 mm的增量传导信号(图6)。 如果没有足够的空间,则可以使用较小的步长进行平移(英式交错模式),如图7所示。使用模拟,可以选择理想的平移角[4]。

图6.使用屏蔽半线将串扰降至最低。

图6.使用屏蔽半线将串扰降至最低。 图7.使用对角线“棋盘格”移位来最小化串扰。

图7.使用对角线“棋盘格”移位来最小化串扰。串扰也可以通过外来方法来减少,例如通过长截线(由于电感电容平衡p / o的位移)来减少[5]。 同样,可以在设计芯片外壳的阶段减少干扰[6]。

因素5。电源总线干扰

除了相邻的信号电路之外,信号质量还可能受到内部层干扰的影响。

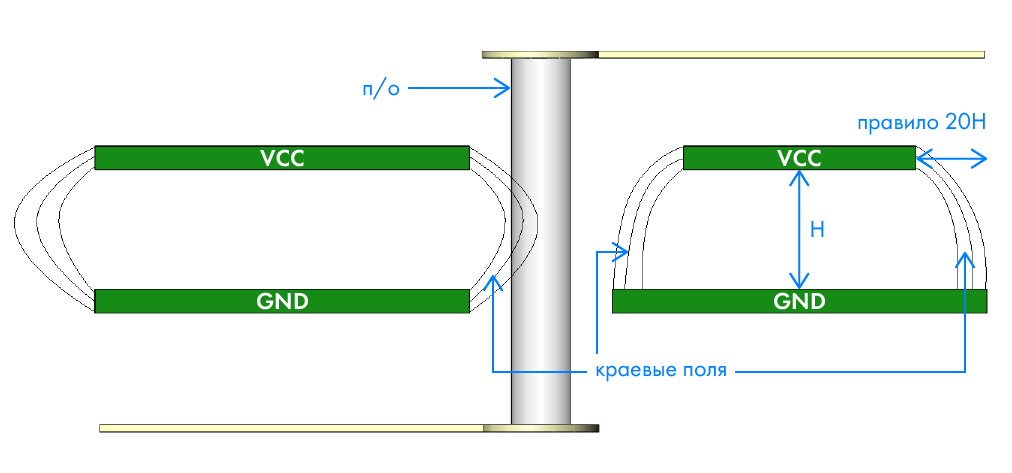

大电流可能会流过食品测试现场。 由于多边形边缘处电感的增加,流动的电流沿着多边形的所有边界(包括切口)形成了边缘场(英语为Fringing场)。 边缘场是进入太空的电磁辐射源(边缘发射的自然辐射)。 为了减少电磁辐射的发射,应用了20H规则(图8),该规则在于缩小相对于陆地多边形的功率范围。

图8. Edge字段和20H规则。

图8. Edge字段和20H规则。为了保护p / o不受干扰,有必要在食品范围内增加防粘垫。 p / o的20H规则很难提供,因此不必要地建议使用直径约2 mm的抗摔落(图9)。

图9.增强食品层的抗跌落能力

图9.增强食品层的抗跌落能力单通孔阻抗计算

基于有关p / o元素对阻抗影响的知识,我们可以设计理想的p / o。 一个很好的开始就是在计算器中计算阻抗。

PCB设计工程师喜欢

Saturn PCB Design Toolkit和

Polar Instruments Si9000e等计算器。 它们都允许您快速计算单个p / o的阻抗。

在这些计算器中获得的结果彼此非常不同。 这是由于这些工具采用了不同的方法。

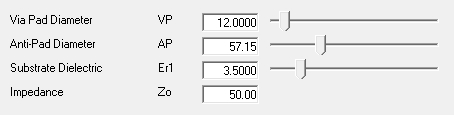

Polar在电源线越过功率范围的二维平面中计算阻抗。 没有给出计算公式。 实验确定,计算是根据同轴电缆的阻抗公式进行的:

图10.来自polarinstruments.com的图像

图10.来自polarinstruments.com的图像与标准相比,该图显示的介电常数Er1相当低。 这是由于介电结构的异质性造成的:它由树脂(Er 3.2)和玻璃纤维丝(Er 6.1)组成,因此平均介电常数约为4.1。 此值可能会在局部变化。 因此,树脂在次表面附近占主导地位,因此,介电常数向下重新计算[7]。

土星PCB通过以下公式计算阻抗:

当p / o长度改变时,电感和电容值会不成比例地改变,阻抗也会改变。 完全相同的p / o长度1.6 mm的阻抗,Saturn PCB计算为128欧姆! (图11)

图11. Saturn PCB设计工具包中的软件计算。

图11. Saturn PCB设计工具包中的软件计算。问题立即出现:谁相信?

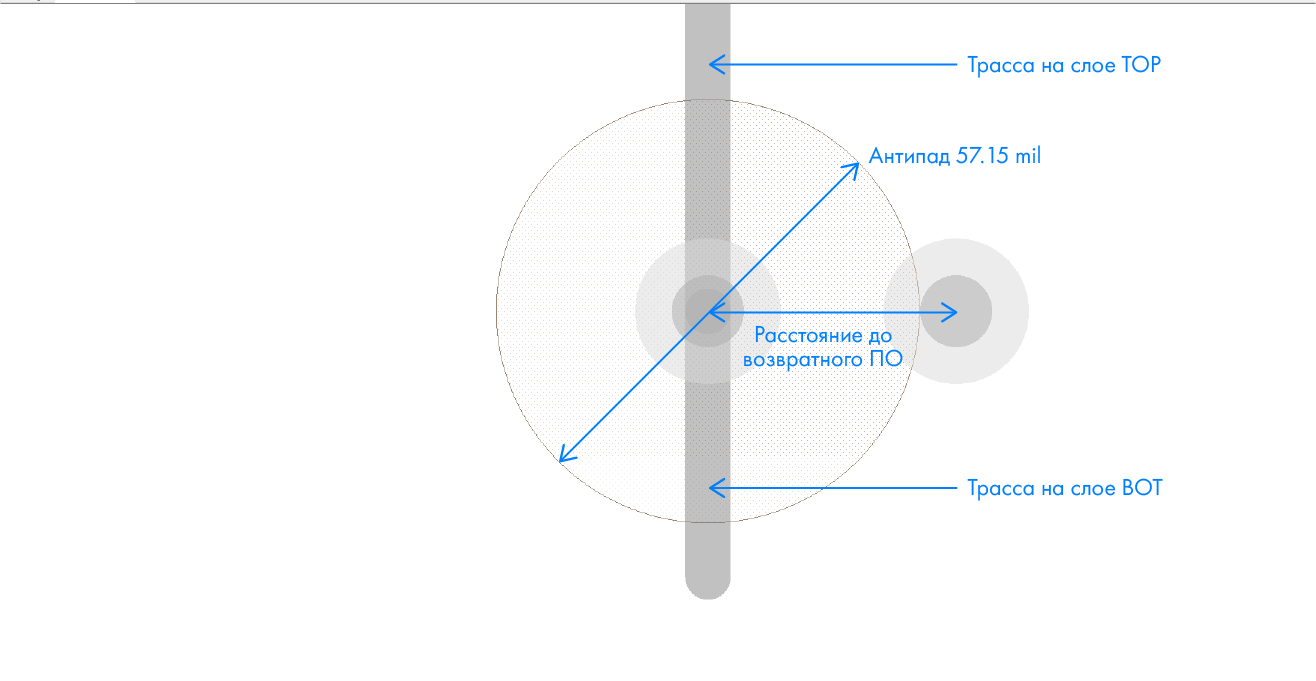

我们在三维电磁场求解器(英语3D Solver)中进行仿真,以模拟它在1.6毫米厚的真实8层板上的外观(图12)。

图12.各层之间的过渡结构,带有一个用于返回电流的孔。

图12.各层之间的过渡结构,带有一个用于返回电流的孔。在我们的情况下,阻抗约为70欧姆。 通过近似返回p / o,您可以再降低5欧姆。 在“发挥”了打击垫的大小之后,您可以非常准确地将阻抗调整为目标值(图13)。

图13.时间图中半波电路的阻抗。

图13.时间图中半波电路的阻抗。在频域中,“最佳”参数用来自输入的反射系数的较低值表示(图14)。

图14.频域中单个p / o的参数

图14.频域中单个p / o的参数计算极坐标更接近结果。 也许,为了在Saturn PCB上获得足够的结果,需要进行校正。 如果有人对在土星中计算阻抗有积极的经验,请分享评论!

差分过孔阻抗计算

差分p / o的计算类似于单次计算,只是现在我们没有计算器:上述工具没有考虑差分p / o。 另外,现在我们可以另外更改微分中的p / o步长。 一对。

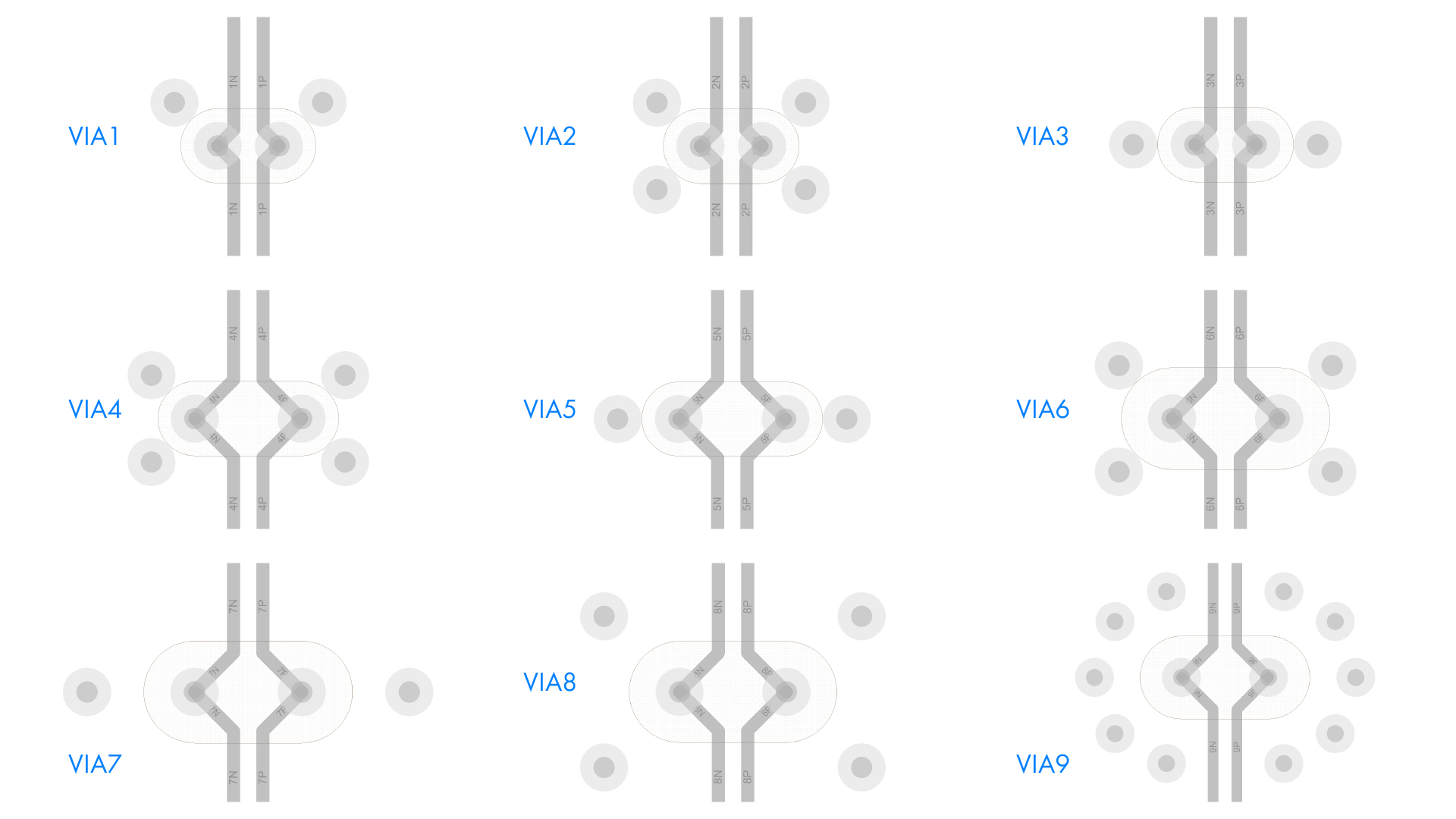

采取相同的结构:一块1.6毫米厚的8层板。 考虑该软件的9种配置(图15)。

前三个p / o的间隙为0.125 mm,仅在返回电流的孔位置不同。 从4开始的所有p / o的间距均为1 mm。 从6开始,P / o的抗跌落能力增加(0.250 mm),并以用于返回电流的孔的凹痕为特征。

图15.通孔

图15.通孔考虑阻抗图(图16)。

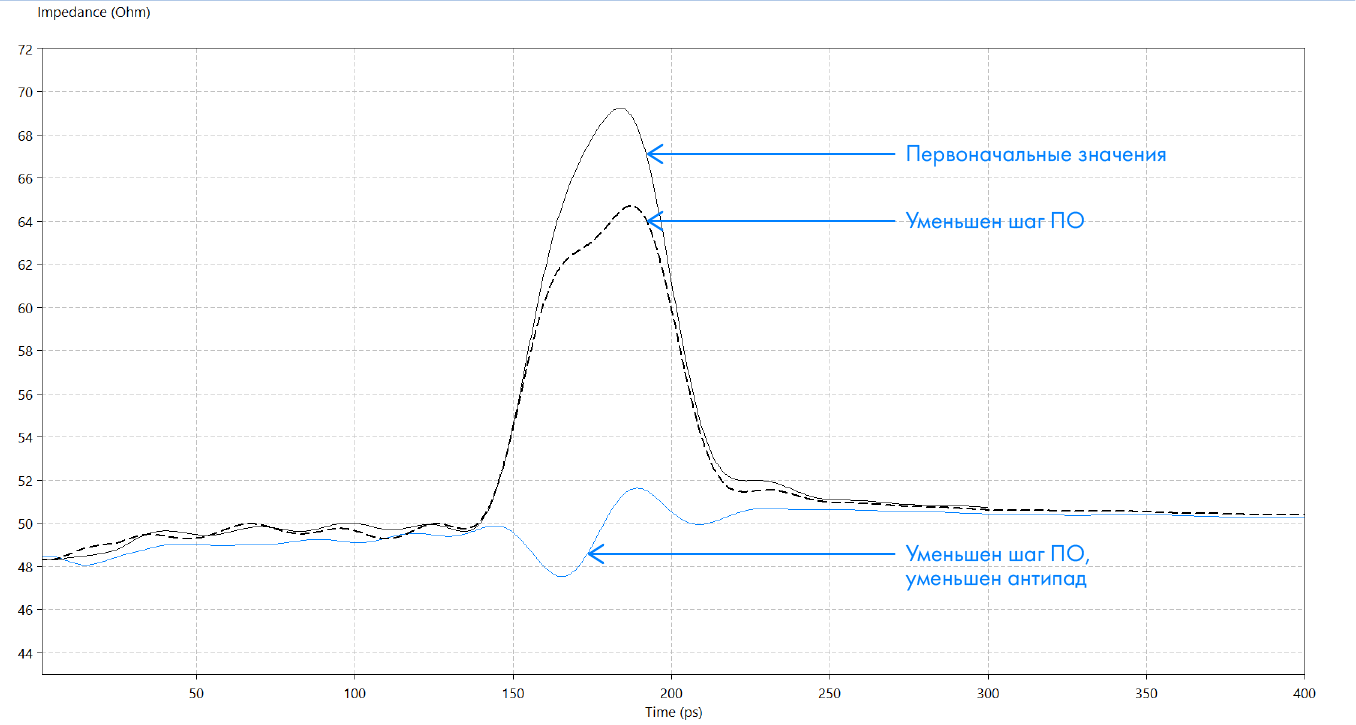

图16.时域中的阻抗p / o。

图16.时域中的阻抗p / o。在图中,“驼峰”清晰可见,它对应于半壳的垂直截面-“玻璃”(英制通孔)。

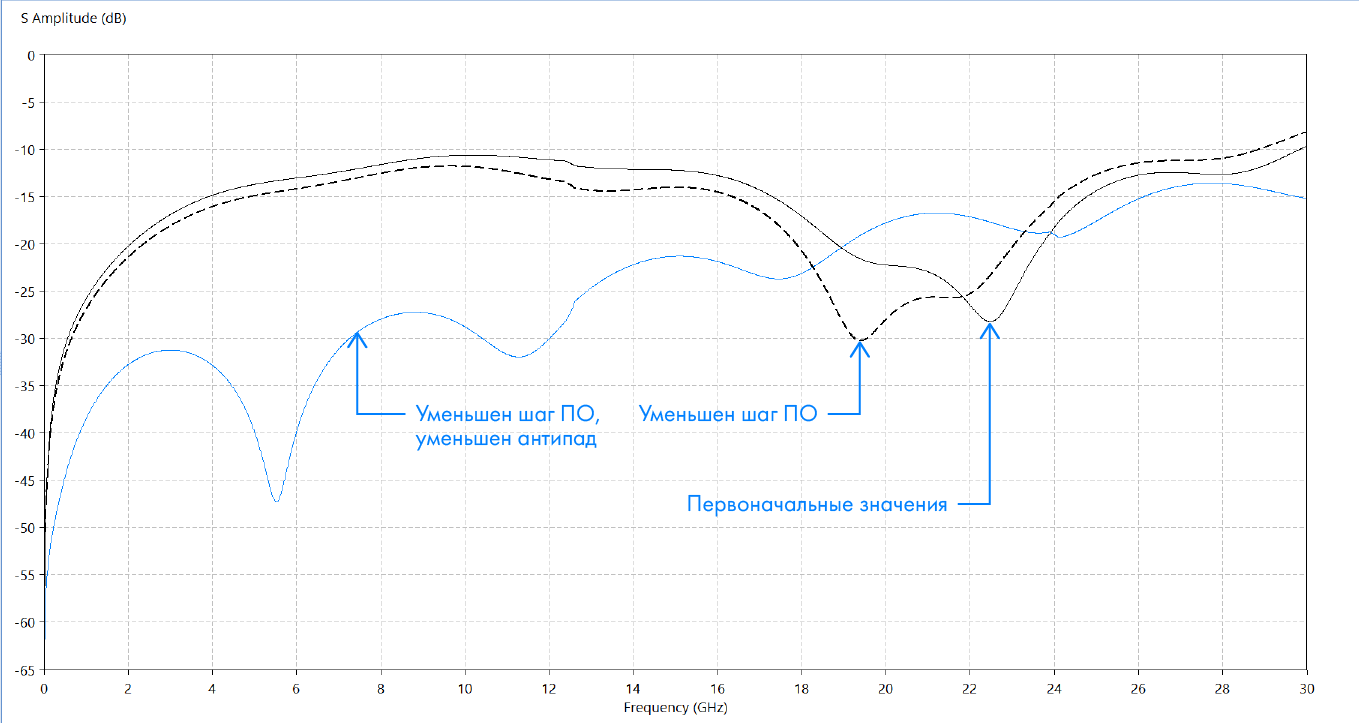

检查了反射系数VIA1-3的频率依赖性(图17)后,我们看到,尽管在6 GHz的目标频率下性能良好,但在较低频率下仍会产生谐振。 最好对via7-9进行改进,如果无法解决,则对via4-5进行改进,以减少由于曲线图向右移动造成的“驼峰”。

图17.输入p / o的反射系数。

图17.输入p / o的反射系数。减少VIA9的抗跌落以获得0.125毫米的间隙。 对于VIA4,我们将p / o步长减小到0.75 mm,并考虑获得的结果(图18)。

图18.修改后的p / o的阻抗比较。

图18.修改后的p / o的阻抗比较。在频域中,反射系数图从输入到右移是可见的(图19)。

图19.修改后的软件的反射系数的比较。

图19.修改后的软件的反射系数的比较。最终建议

印刷电路板上的通孔是一个复杂的异构结构。 为了正确计算参数,需要昂贵的3D求解器,能力和大量的时间成本。

如果无法避免使用关键信号到其他层的过渡,则首先必须评估所产生的不均匀性对信号完整性的影响程度。 如果异质性在电气上很短(延迟时间小于前端的1/6),则短截线会在通带之外的频率产生谐振-在优化上浪费时间和金钱是没有意义的。

首先,使用数据表或先前开发板中的现成结构很方便,但要记住当前项目的功能。

计算器使您可以快速评估软件的参数,但是它们使用高度简化的模型,会对结果产生负面影响。