如今,有不止一种类型的内存,每种类型的内存都用于特定任务。 他们可以很好地处理任务,但是存在许多缺点,因此无法将这些内存选项中的任何一个称为通用。 如果我们在这里添加全世界范围内庞大的数据增长以及人类对节能的渴望的问题,那么就必须创造出全新的东西。 今天,我们将进行一项研究,科学家在研究中介绍了一种结合了闪存和DRAM存储器优点的新型存储器。 这种创新具有哪些“优点”,使用了哪些技术来创造它,前景如何? 我们从研究小组的报告中了解到这一点。 走吧

学习基础

内存的类型很多,所有这些都是针对特定任务创建的:用于高速缓存的SRAM(静态随机存取存储器),用于活动内存的DRAM(动态随机存取存储器),用于数据存储的闪存等等。 但是,正如预期的那样,上述每种类型的内存都有其自身的缺陷。

例如,闪存是具有浮动栅极(FG)的MOS晶体管(金属氧化物半导体)的集合,用于存储电荷。 在这样的实施例中,将数据表示为FG中保持的电荷量,其被氧化物层隔离。

根据科学家的缺点,对于记录和擦除,需要足够高的电压以通过控制快门(CG)进行控制,通常约为±20 V

2 。 此过程很慢,并且由电涌引起的故障机制会导致设备寿命缩短。

尽管有这个负号,但还有一个令人印象深刻的优点-通过检查通道电导率读取数据,该通道电导率几乎不需要。 因此,数据保持完整,这称为非破坏性读取。

反过来,DRAM比闪存快得多,这就是为什么它可用于主动计算过程。 DRAM的缺点是,数据在读取时会从单元中丢失。 此外,还会发生用于存储数据的电容器的电荷泄漏。

SRAM也是一种相当快的存储器类型,并且数据丢失的程度不如DRAM中的那样。 但是,通常每个单元使用6个晶体管,也就是说,芯片上需要很大的面积。

在介绍了经典类型的内存的上述缺点之后,科学家们强调了找到一种可以避免此类问题的替代方案或混合方案的重要性,同时还要结合其前辈的所有优势。

在这项工作中,研究人员将注意力集中在新型存储器上,即一种新型的,低压,半导体,基于电荷的紧凑型非易失性存储设备,可在室温下运行。 研究人员称他们的后代为“普遍记忆”(简单但有品味)。

该器件是具有浮栅的存储器,基于InAs / AlSb / GaSb异质结构创建,其中InAs既用作浮栅又用作没有过渡的沟道。

科学家已经为单细胞原型提供了仿真和实际测试结果。

研究成果

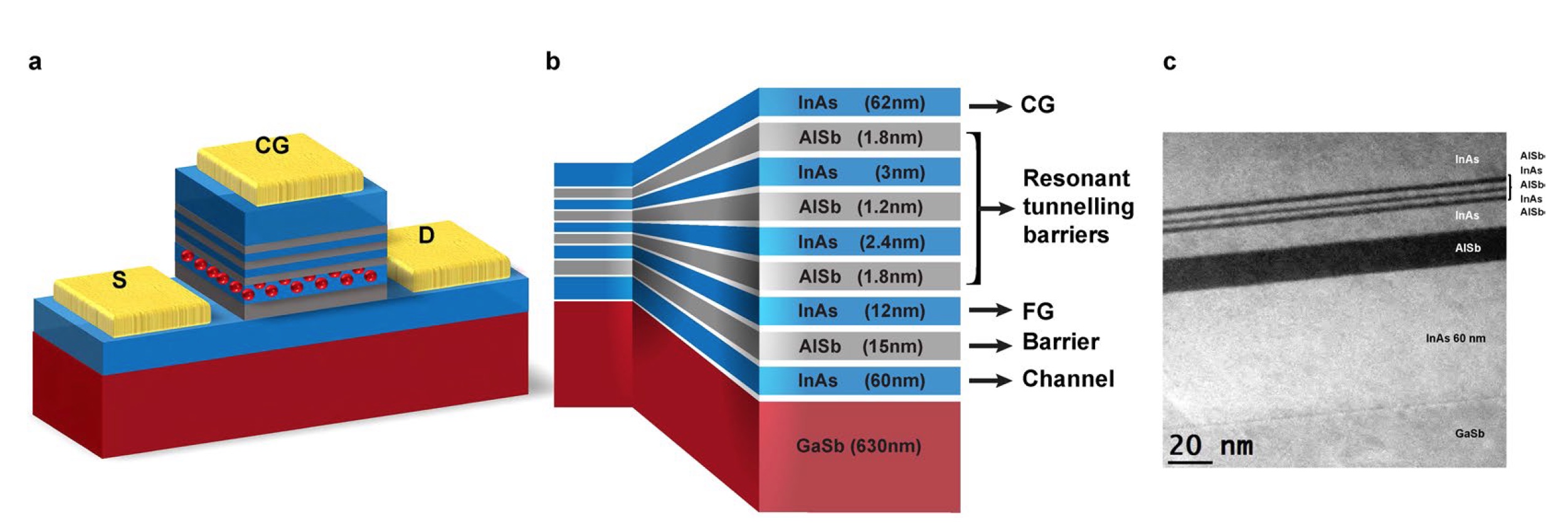

图片编号1

图片编号1上图显示了设备的示意图和PREM(透射电子显微镜)的图像。

与闪存一样,此设备中的电荷存储在FG中,但同时没有氧化物阻挡层。 相反,在所谓的6.1-Å系列半导体中使用了导带的移动。 也就是说,存储单元下面的器件比MOS晶体管更像高电子迁移率晶体管(HEMT)。 InAs构成不包含过渡的通道。 但是,使用n掺杂是为了补偿无意的背景掺杂并使Ga空位保留在下面的GaSb中。 这两个任务自然会形成p型层。

pn结*是两种具有不同导电类型的半导体的接触面积-p(空穴)和n(电子)。

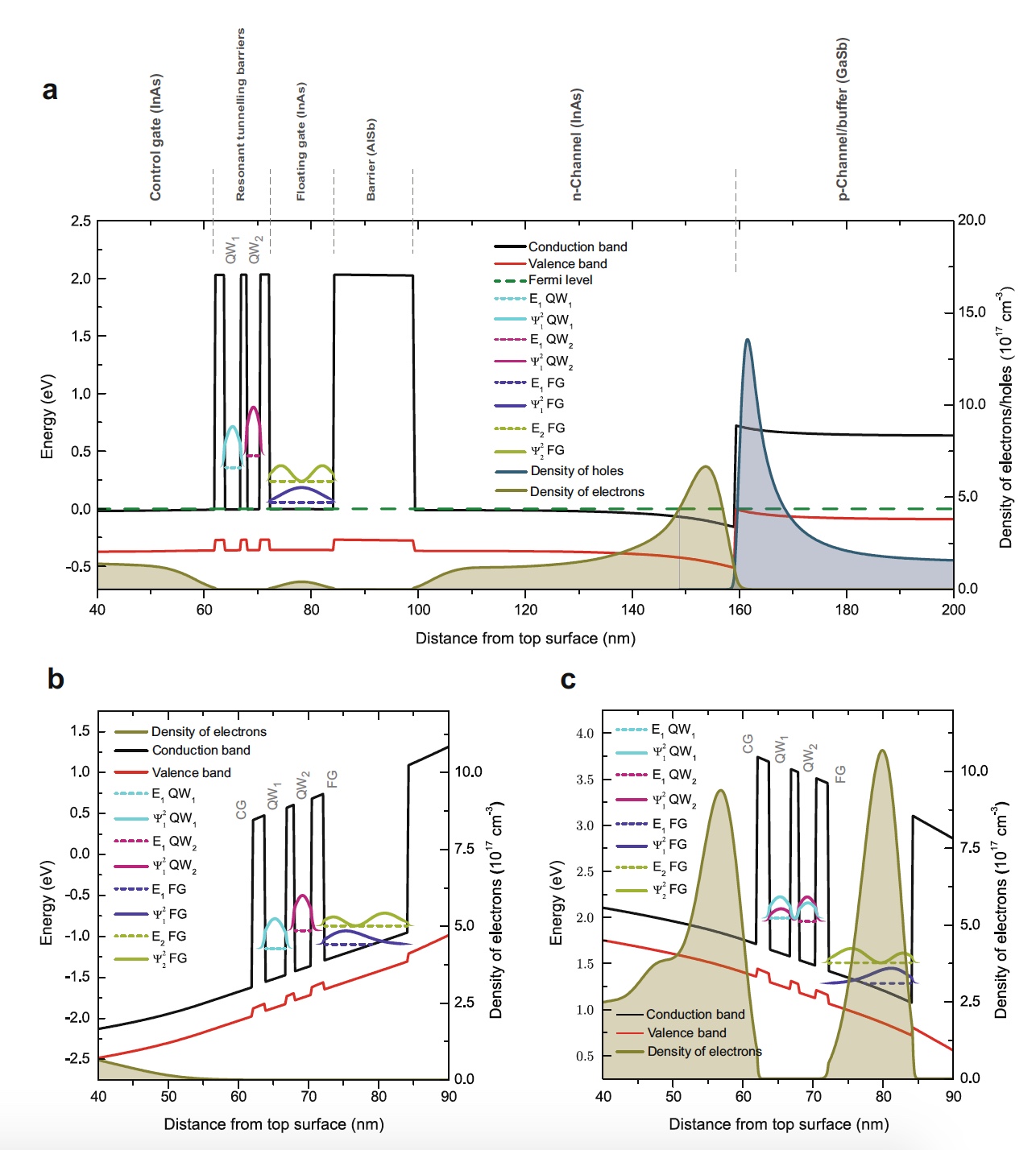

图片编号2

图片编号2曲线

2a显示了在没有偏置的情况下能带的模拟排列以及层中电子和空穴的密度。 理论数据和仿真结果表明,InAs和GaSb界面处的InAs导带低于GaSb价带。 并且这导致电子从GaSb层转移到InAs层,此后空穴保留在GaSb中。

空穴*是未填充的价键,表现为与电子电荷相等的正电荷。

在InAs和GaSb之间的界面处可以看到累积的电子/空穴,但是InAs通道中的电子未连接到InAs / GaSb界面,并且在整个InAs中都可以观察到它们的密度。 整个通道的电导率由InAs中的电子控制,与GaSb中的空穴相比,InAs中的电子具有更高的迁移率和密度。

InAs层的内部FG通过AlSb势垒(15 nm)与InAs通道隔离。 同时,双

* InAs

量子阱和三个AlSb势垒充当FG和CG InAs之间通过n掺杂的共振隧穿势垒。

量子阱* -限制了粒子在二维(而不是三维)中的运动,因此,它们只能在平坦的层中运动。

因此,在所研究的器件中,InAs层的FG中存储的电子被AlSb导带中的异常大间隙所隔离。 这意味着您可以获得一个限价系统,该系统在室温下的存储时间等于1014年。

所研究设备的操作最重要的方面是以下事实:三重共振隧穿势垒中的两个量子阱(QW1和QW2)具有不同的厚度,即,出现了具有不同能量的受限状态(

2a )。 由于QW2比QW1薄,因此QW2中电子的唯一可用能级比QW1中的等效能级高。 另外,QW1中的状态具有比相邻CG区域中的状态高得多的能量。 这样可以防止CG和FG之间直接发生电子隧穿,并且从CG到FG的电子传输势垒(反之亦然)由InAs / AlSb导带的2.1 eV偏移确定,即电荷不会流入FG /从FG流出。

浮栅(FG)中的基态和初级激发态位于两个QW内部的能量态之下。 因此,当不施加电压时,电子被锁定在FG内部,即电子被锁定在FG内部。 对于进入/离开FG的电子,三重共振隧穿势垒变得不可逾越。 因此,实现了非挥发性。

如果向控制栅极(CG)施加了微不足道的电压,则可以调节共振隧穿势垒内部的能量状态耦合,这将使电子自由地从(

2b )或(

2c )浮栅通过。

在实验过程中,所有读取,写入和擦除操作均在一个暗盒中的几个单元中进行(快门尺寸为10 x 10μm),该暗盒在室温下受到静电保护。 研究人员强调,包括记录和擦除在内的所有操作均在≤2.6 V的偏移量下进行,该偏移量比闪存单元的完整操作所需的偏移量低约一个数量级。 通过在CG和源极之间将控制栅极(V

E CG-S )偏移+2.5或+2.6 V来执行擦除操作,从而导致状态为“ 0”。

图

2b显示了擦除电压为+2.6 V时获得的能带的模拟对准。在这种情况下,QW1中计算出的电子能级低于QW2中的能级,而两者均低于第一个激发态并接近能级。 FG中的基态。 结果是擦除,即从FG到CG的电子通量,然后是FG耗尽。 相同的原理适用于写操作:V

W CG-S = -V

E CG-S以增加FG中的电荷(状态“ 1”)。

曲线

2c是当控制栅极偏移用于数据记录时的模拟能量区:V

W CG-S = -2.6V。在这种情况下,QW1和QW2中的能级实际上重合,这导致这些状态,共振隧穿和流的强耦合电子从CG到FG。

由于电容耦合,沟道电导率取决于FG中存储的电荷量,因此,通过在固定的栅源电压下测量栅源电流来读取数据。

FG的费用增加,即 状态“ 1”降低了沟道中的电荷,这导致其电导率降低。 在状态“ 0”的情况下,发生相反的过程。 可以读取数据而不会对CG产生任何偏见,但是电压对于单个选择单元阵列中的设备是必需的。 此外,电压应通过谐振隧穿势垒产生电场,这将使电荷从FG转移到FG成为可能。 为了实现这些任务,仅需要〜2.5V。

通用内存功能

在实际测试中,以CG和V

SD = 1.0 V的零偏移量进行读取。但是,根据科学家的说法,可以施加较小的电压来成功读取。

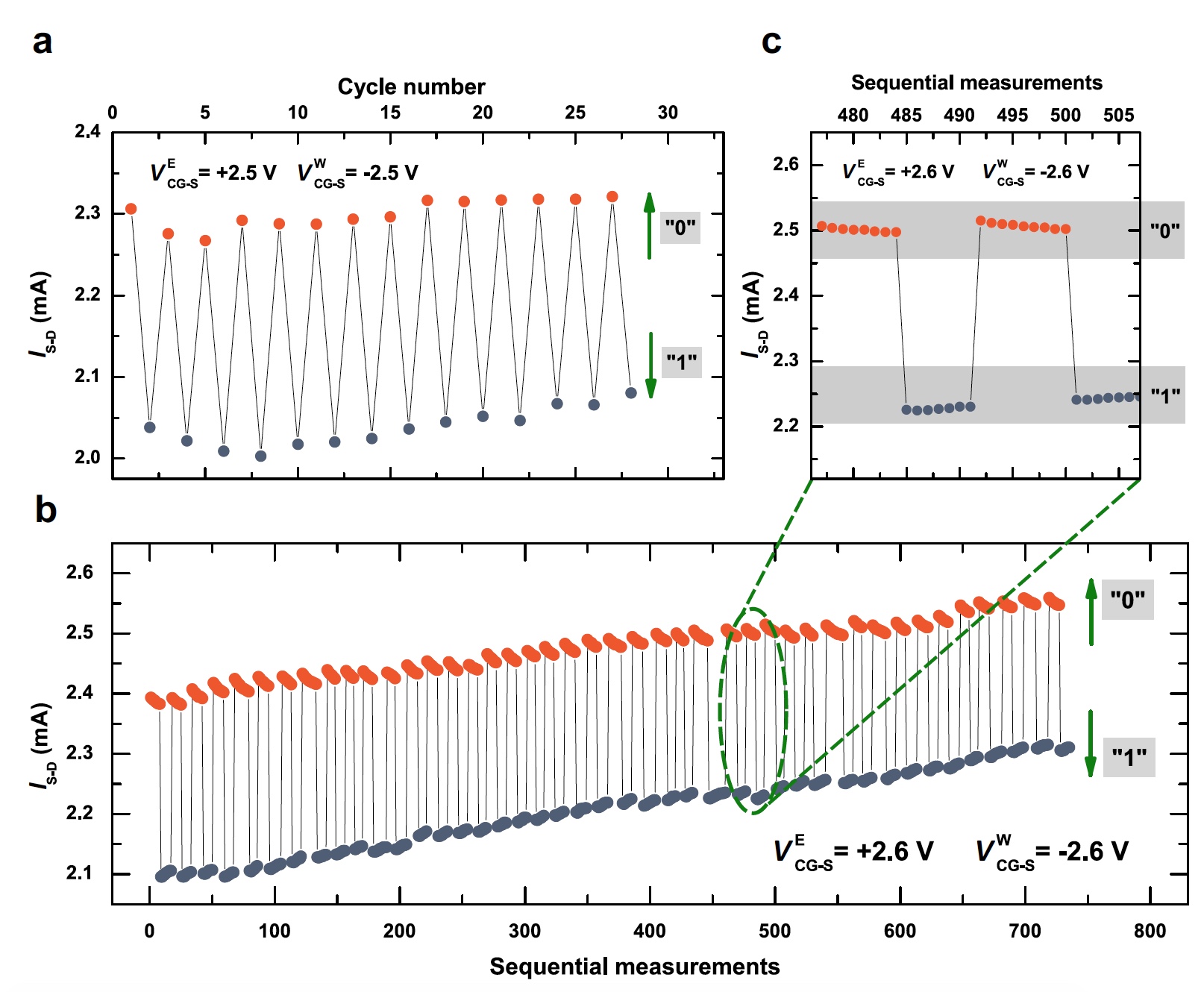

图片编号3

图片编号3图

3a显示了擦除-读取-写入-读取过程。 该序列的主要特征是在每个擦除或写入步骤之后的读取操作。

图

3b显示了一个更复杂的序列,其中在每个擦除和写入操作之后,没有一个读取操作,而是多个读取操作。 通过这种方式,研究人员证明了读取操作是无损的。

在状态“ 0”和“ 1”之间,所有序列都有明显的区别。 但是,在

3b上,随着操作次数的增加,有迹象表明I

SD会对称向上移动。 尽管这种行为的原因尚不清楚,但科学家打算在进一步的工作中探索这一方面。 但是在

3a上没有观察到这点,因为擦除/写入的电压略低。

经过几百次写入和擦除操作以及数次实际测试中的许多读取操作后,科学家们没有发现任何损坏设备的迹象。

基于电荷存储的所有类型的存储器的重要特征是开关能量取决于电容器的充电能量。

闪存技术的基本原理与正在研究的通用存储器的相似性表明,这两种类型的存储器进行了比较。 如果我们假设这两种类型的两个设备具有相同的容量和相同的快门尺寸,那么通用存储器的开关能量将比闪存的开关能量小64倍。 这些惊人的数字也显示了通用内存优于DRAM。

根据理论估算,对于尺寸为10 x 10μm的器件,CG-FG电容约为10

-12 F,开关能量约为2 x 10

-12J 。减小器件的物理尺寸,对于尺寸为20的器件,开关能量会急剧降低至10

-17 J纳米,这比DRAM小100倍,比闪存小1000倍。 根据研究人员的大胆声明,这是非常独特的特征。

图像

3c显示了来自

3b的一些写-擦除操作,其中状态“ 0”和“ 1”之间的差异可见:擦除后的连续读取测量为状态“ 0”提供了稍低的I

SD 。 记录后通过顺序读取测量观察到相反的情况,或者说I

SD稍大。

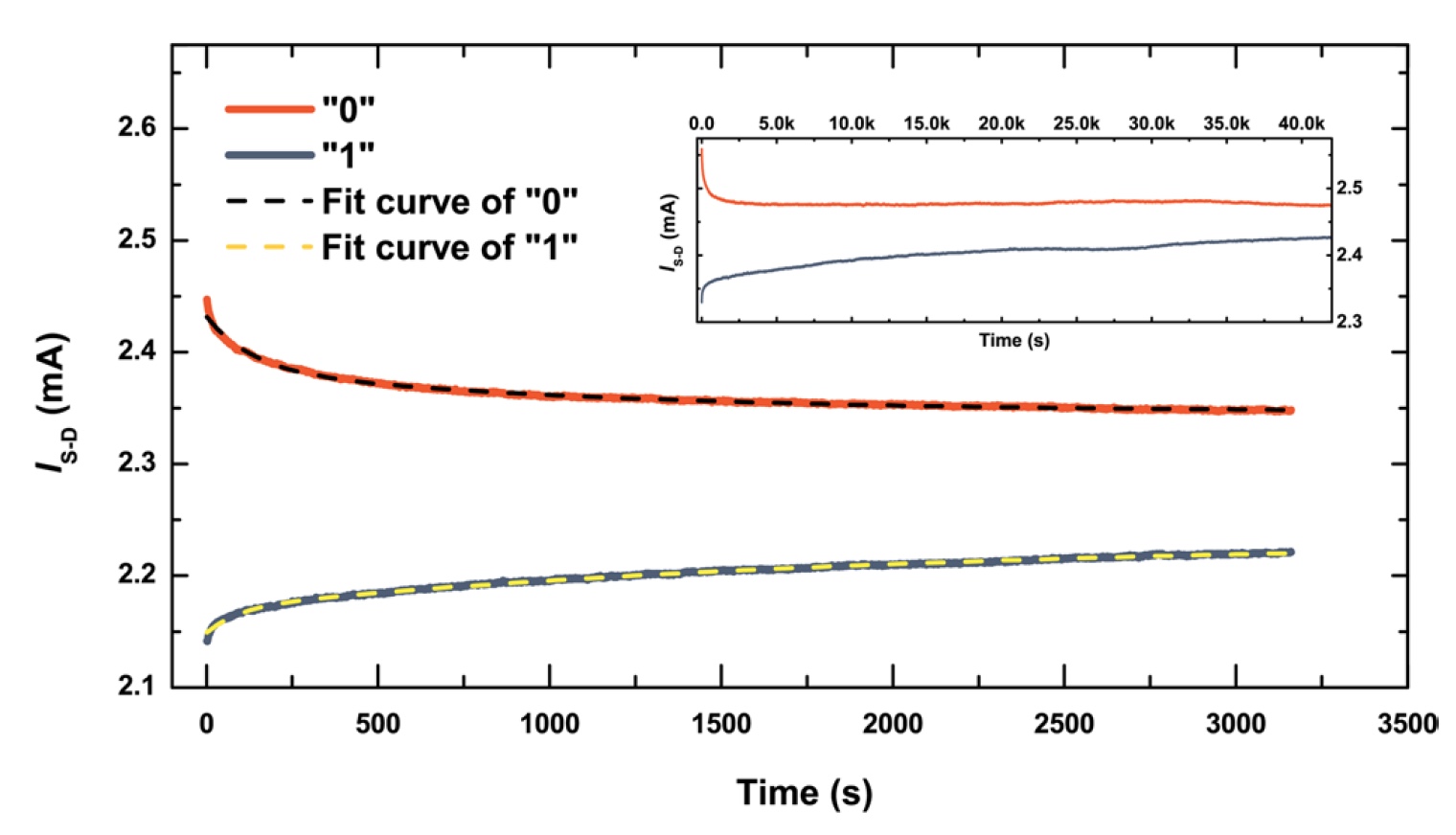

科学家将这种影响归因于数据的可变性(波动性)。 为了研究这一点,科学家在很长一段时间内针对每种记忆状态进行了一系列读取操作(图4)。

图片编号4

图片编号4状态“ 0”和“ 1”都显示了初始快速衰减,这与

3s所见一致。 但是此后,发生的变化要慢得多,因此在整个观察期间,可以清楚地区分对应的状态“ 0”和“ 1”。

还进行了另一个实验(插入第4号图像),该实验显示了指数衰减的极限饱和度以及时间上可区分的状态“ 0”和“ 1”。

双指数衰减的存在意味着几种机制可以立即降低状态。 在可能的选择中,科学家可以区分出穿过AlSb势垒中缺陷状态的隧穿,穿过狭窄的InAs带隙的电子的热激发以及与热产生的空穴的复合。

评估设备的电容和记录/擦除所施加的电压表明,在写入和擦除操作期间,大约107个电子从/向浮置栅极转移。 这很多,但实际上没有观察到负面影响。

要更详尽地了解这项研究的细微差别,建议您查看

研究小组的

报告 。

结语

科学家不仅设法开发出一种新型的存储器,而且还成功地在室温下对紧凑型非易失性,基于电荷的设备进行了成功的首次实用测试。 科学家还通过非对称三重共振隧穿势垒的量子力学特性,将非易失性和低压开关相结合。 研究人员说,他们的设备可以缩放而不失其尊严。

时代在变化,技术也在变化。 闪存,SRAM和DRAM长期以来一直在存储设备中占据主导地位,但是如果通用存储器的开发继续取得与本研究相同的成功,这种情况可能会改变。 该技术将大大降低配备该技术的设备的功耗,并延长其使用寿命并提高生产率。

作者计划进行的进一步研究将显示革命性记忆是如何被科学家自豪地称为普遍性的。

谢谢大家的关注,保持好奇心,祝大家工作愉快!

感谢您与我们在一起。 你喜欢我们的文章吗? 想看更多有趣的资料吗? 通过下订单或将其推荐给您的朋友来支持我们,为我们为您开发

的入门级服务器的独特模拟,为Habr用户提供

30%的折扣: 关于VPS(KVM)E5-2650 v4(6核)的全部真相10GB DDR4 240GB SSD 1Gbps从$ 20还是如何划分服务器? (RAID1和RAID10提供选件,最多24个内核和最大40GB DDR4)。

戴尔R730xd便宜2倍? 只有我们有

2台Intel TetraDeca-Core Xeon 2x E5-2697v3 2.6GHz 14C 64GB DDR4 4x960GB SSD 1Gbps 100电视在荷兰起价199美元 ! 戴尔R420-2x E5-2430 2.2Ghz 6C 128GB DDR3 2x960GB SSD 1Gbps 100TB-$ 99起! 阅读有关

如何构建基础架构大厦的信息。 使用价格为9000欧元的Dell R730xd E5-2650 v4服务器的上等课程?