我决定用俄语和英语在哈布雷(Habré)上写此笔记,以便在英语和俄语论坛和小组中分发指向该链接的链接。 俄语文本不是英语的翻译,反之亦然-我只是写了两次便条(我讨厌翻译)。 那些想批评我的英语的人将被立即发送到该帖子的末尾,在那里,他们将在长达数小时的视频中对我的口音感到震惊。 我认为我的强调不是错误,而是功能。 我们都知道许多美国人发现,例如,鼻咽的英国口音很有吸引力。 现在该给予严肃的俄罗斯口音相同的地位了。 为此,尽可能多的俄罗斯人需要在各种国际活动中发表演讲。 我们的密码是“从五月哈特说话的年英里”。

但是首先是关于展览。

全球数以百万计的小工具消费者正在观看1月在拉斯维加斯举行的消费电子展(CES)。 他们从来不知道D触发是什么,他们重要地指出,在AMD和高通公司最新的处理器中,四GHz优于三GHz。 但是有一个展览不是针对消费者,而是针对电子开发商。 该展览称为设计自动化会议(DAC),并且在某些年内它还在拉斯维加斯举行,但不是在12月,而是在6月。

每年都有数以百万计的小玩意儿观看1月在拉斯维加斯举行的消费电子展(CES)。 那些从未学习过D触发器功能以及如何计算静态定时的人,在阅读了他们认为是技术出版物的《连线》杂志上的最新文章之后,讨论了千兆赫兹频率。 但是,还有另一次会议,不是针对消费者,而是针对电子产品的创造者。 该会议称为设计自动化会议(DAC),它也在拉斯维加斯举行,虽然不是每年,不是在1月,而是在6月。

电子设计自动化(EDA)行业为硬件设计师提供软件。 EDA由三大公司控制:Synopsys,Cadence和Mentor Graphics(现在是Siemens的一部分)。 Synopsys和Cadence都有完整的产品集,这些产品是设计和仿真多级别数字芯片所必需的。 设计流程称为RTL2GDSII,从规格说明开始,并使用硬件描述语言(Verilog或VHDL)对电路的循环行为进行编码,然后继续将该描述合成为逻辑元素图(网表),然后继续将网表放入物理芯片的设计图和用于连接标准单元的路由芯片上布线,这些标准单元是ASIC(专用集成电路)的组成部分。

三大公司主导着电子设计自动化行业:Synopsys,Cadence和Mentor Graphics(西门子几年前收购了)。 Synopsys和Cadence已创建了涵盖整个RTL2GDSII设计路线的软件。 我在四年前的

上一篇DAC文章中简要描述了这条路线:

在过去的25到 30年中,微电路的设计通常是用设备描述Verilog的语言编写的(在欧洲和军事领域-VHDL),之后,一个特殊的程序(逻辑综合)将设计变成电线和逻辑图元的图形,另一个程序(静态时序分析)告诉设计者是否适合速度预算,第三个程序(布局布线)将这种设计布置在芯片上。

当设计经过所有阶段时:在面纱上进行编码,调试,验证,综合,静态时序分析,布局规划,n布线,寄生物提取等。 -结果是一个名为GDSII的文件被发送到工厂,然后工厂烘烤芯片。 这种类型的最著名的工厂由台积电或台积电拥有。

John Sanguinetti,自1980年代起担任Verilog专家。 John是一家名为Chronologic Simulation的公司的创始人,该公司早在1990年代就创建了VCS,这是Verilog编译代码模拟器。 该模拟器现在是Synopsys的属性。 大多数大型电子公司都使用VCS。 VCS为Synopsys带来了数十亿美元的收入。

陈列室旁边是约翰·桑吉内蒂(John Sanguinetti),他是1980年代的早期语言大师,也是Chronologic Simulation的创始人。 该公司向全世界提供了快速的Verilog编译代码模拟器(VCS)模拟器,该模拟器现在是Synopsys的财产。 大多数主要的芯片开发人员都使用此模拟器。 VCS为Synopsys带来了数十亿美元的收益:

Mentor Graphics现在是第三大EDA公司西门子的一部分。 与Synopsys和Cadence不同,Mentor Graphics没有完整的RTL2GDSII工具系列。 它最受认可的两个收入来源来自一套物理设计验证工具Calibre和一个硬件仿真器Veloce。 口径包括例如检查芯片最终“设计图”上的几何设计规则(宽度,间距,外壳)的工具。 Veloce使用类似于FPGA的芯片,可以非常快速地仿真Verilog设计。

Mentor Graphics是EDA行业的第三大公司,于2016年底成为Siemens的一部分。 与Synopsis和Keydens不同,Mentor并不具有覆盖RTL2GDSII路由的整个程序链。 Mentor的两个主要收入来源是Caliber软件包和Veloce仿真器,该软件包在微芯片设计的最后阶段进行检查。 Calibre验证的一个示例是芯片上的迹线之间的最小距离

,这样就不会产生天线效应 。

UPD:根据专家意见修正 :天线通常是另一根。 当一条轨道变得如此之大以至于它开始像天线一样工作时,就会发生这种情况,它会以等离子振荡的频率接收信号,以便在生产期间进行蚀刻。Veloce仿真器使用FPGA形的ASIC来快速仿真逻辑上描述的电路仿真,即在Veril上。

除了利润丰厚的Calibre和Veloce项目外,Mentor总是有大量其他项目,产品,服务,培训和教育计划。 例如,Mentor正在培养功能验证领域,这是数字设计工作流程中至关重要的一部分。

除了诸如Calibre和Veloce之类的高利润项目外,Mentor还拥有许多其他项目,产品,服务,研究项目和教育计划。 例如,在Mentor,他们从事功能验证,这是生产过程的关键部分:

包括Doulos,Willamette HDL和Sunburst Design在内的许多小型公司向大中型电子公司出售硬件验证培训。 之所以存在这样的利基市场,是因为数十年来,大学没有在其课程中适当地教授功能验证的技巧,并且未采用新技术,例如System Verilog,UVM,使用并发断言的形式验证,Portable Stimulus等。 据我从与毕业生的交谈中得知,就连斯坦福大学也没有课程。

功能验证提供了一些小公司,这些小公司以令人耳目一新的高价向大公司出售SystemVerilog和UVM培训,例如每人几千美元。 其中包括Doulos,Willamette HDL,Sunburst Design等:

另一个名为Verific的小公司。 他们只有少数人,但在利基市场上非常成功。 Verific出售由重要的EDA公司(无论大小)采用的SystemVerilog解析器。

这是另一个很小的公司,只有几个人,但却是一家非常成功的同类公司,称为Verific。 她出售Verilog的解析器,许多EDA公司都使用该解析器:

Verific的创始人接受了一个流行的EDA网站EDA Cafe的采访。 还有其他一些受欢迎的EDA网站,包括John Cooley的deepchip.com,但这次我没有在DAC地板上遇到John Cooley。

以下是Verific创始人对行业流行网站EDA Cafe的采访:

现在让我们谈谈FPGA。

现在让我们谈谈FPGA,它们是PPVM(现在他们会纠正我),它们是FPGA。

这是什么,我在四年前的

上一篇DAC文章中也做了简要介绍:

在最简单的版本中,FPGA由同质单元矩阵组成,可以使用连接到配置存储器位的多路复用器将每个均质单元转换为功能。 一个单元可以成为一个具有四个输入和一个输出的“与”门,另一个单元可以是一个单比特寄存器等。 我们将一系列位从存储器中加载到配置存储器中-给定的电子电路在FPGA中形成,它可以是处理器,显示控制器等。

FPGA / FPGA不是处理器,通过“编程” FPGA(填充在FPGA配置存储器中)可以创建电路(硬件),而在对处理器(固定硬件)进行编程时,可以滑入一串顺序的程序指令(软件)。

FPGA的两个最大生产商是Xilinx和Altera,它们现在已成为Intel的一部分。

生产FPGA的两家最大的公司是Xilinx和Altera,它们现在是Intel的一部分:

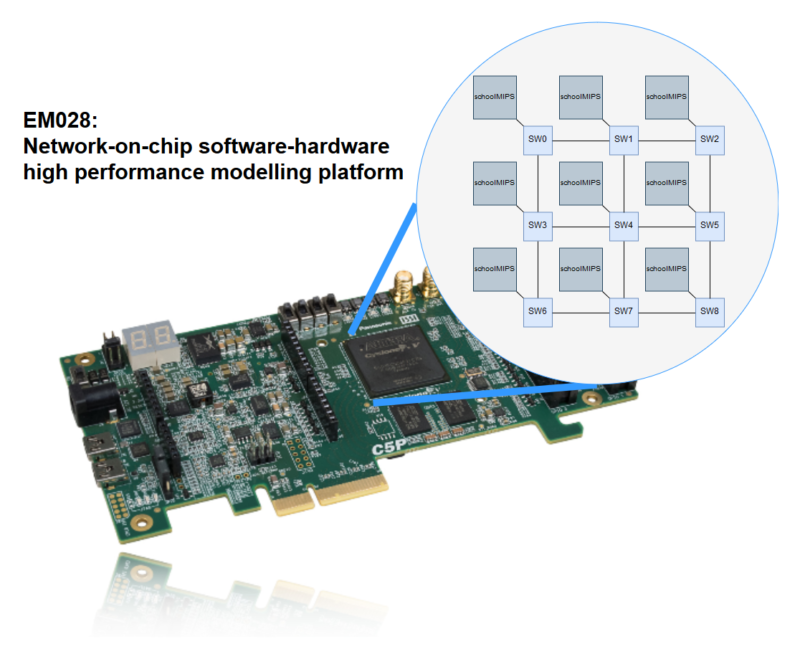

英特尔本周收集了第一轮Innovate FPGA竞赛的选票。 俄罗斯的参赛作品之一使用了微小的schoolMIPS处理器内核网格。

schoolMIPS实现了MIPS体系结构的子集。 它存在多种变体,包括无数据存储器的单周期(最简单的周期),具有中断的版本,流水线版本等:

顺便说一下,英特尔本周将在Innovate FPGA竞赛中投票,

俄罗斯团队也将参加。 一个项目是

基于NoC的多处理系统原型 。 这是一个基于Stanislav Zhelnio

sparf (基于Harris和Harris的书“ Digital Synthesis and Computer Architecture”的书)基于处理器的,具有大量节点的芯片上的原型网络,

网址为https://github.com/MIPSfpga/schoolMIPS 。 在MIEM NRU HSE招收4年制学生:

FPGA的领域不仅限于Xilinx和Altera / Intel。 有几家规模较小的供应商,例如Lattice和Microsemi / Actel,甚至没有自行设计终端芯片的小型公司也将ASIC公司的FPGA单元模块设计许可给了公司。 一个有用的应用程序是创建连接到固定高频CPU内核的可重新配置的协处理器。 另一个应用程序是安全性:一些公司希望将其秘密隐藏在可重新配置的逻辑中,而不是将其固定逻辑的布局展示给有动力的电子显微镜研究人员,并花费大量时间。

但是,FPGA领域的参与者较少,例如,有两家公司获得了可嵌入多路固定电路以提高灵活性的FPGA模块设计许可。

每个DAC都有几个FPGA板供应商。 不是不是像Digilent和Terasic这样的廉价学生板供应商的价格从55美元开始,而是用于ASIC原型设计的FPGA板的价格可能在30,000美元,100,000美元或更高。

传统上,FPGA板的制造商会参加DAC。 他们不会以55美元的价格出售便宜的学生卡,而是以55美元-千美元甚至更高的价格出售FPGA板卡。 他们的客户不是学生,而是一个认真的ASIC开发团队,该团队使用大型开发板进行原型设计。

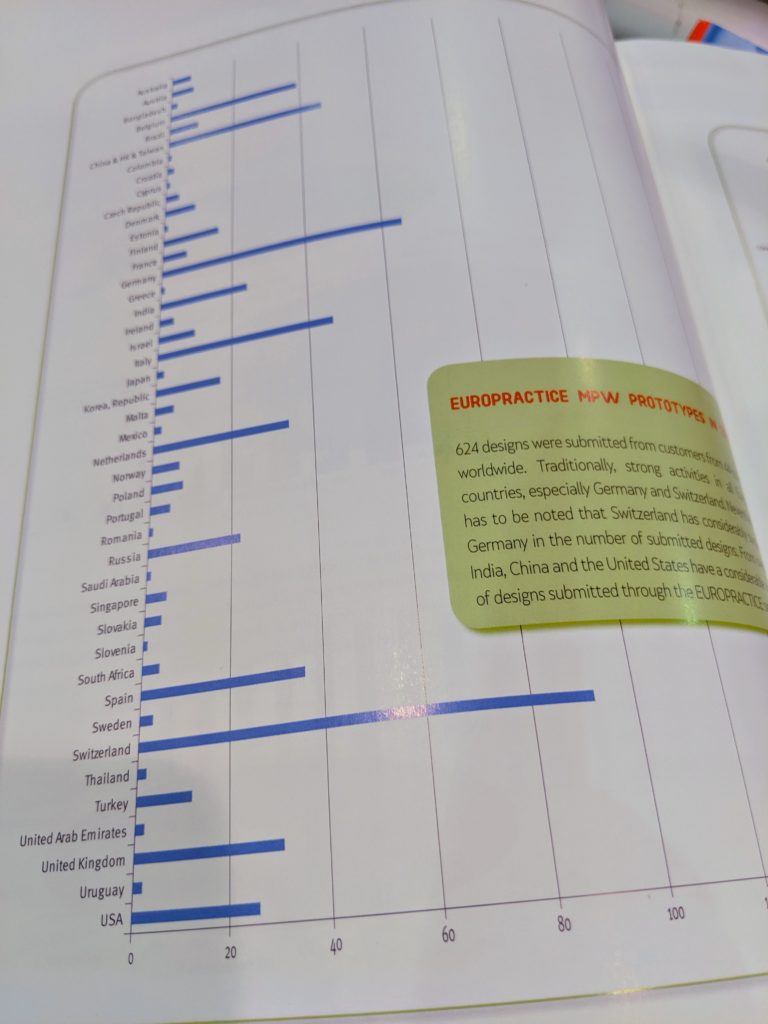

如果研究人员使用FPGA进行了概念验证并现在想制造自己的ASIC,该怎么办? 制造ASIC的典型商业订单通常需要约30万美元至3,000,000美元的初始付款,具体取决于工艺技术。 但是,有一些专门的公司(欧洲的Europractice和美国的MOSIS)出售少量的“班车”服务或多项目晶圆(MPW)服务,其180nm技术的起价仅为3000美元,而现代产品的起价仅为1万美元。 28纳米

但是,如果一个学生或一家苛刻的公司想要在工厂中生产真正的ASIC,而却几乎没有钱怎么办? 或者,如果不后悔,它是测试芯片还是一小批? 为此,在美国设有MOSIS公司,在欧洲设有Europractice公司。 几千美元-您将掌握为180纳米等技术设计的芯片。 数以万计的-您可以掌握最新技术(例如28纳米)的芯片,例如第五款iPhone。 我注意到,对于大规模商业化生产,工厂的初始付款是从旧技术的数十万美元到新技术的两三百万美元。

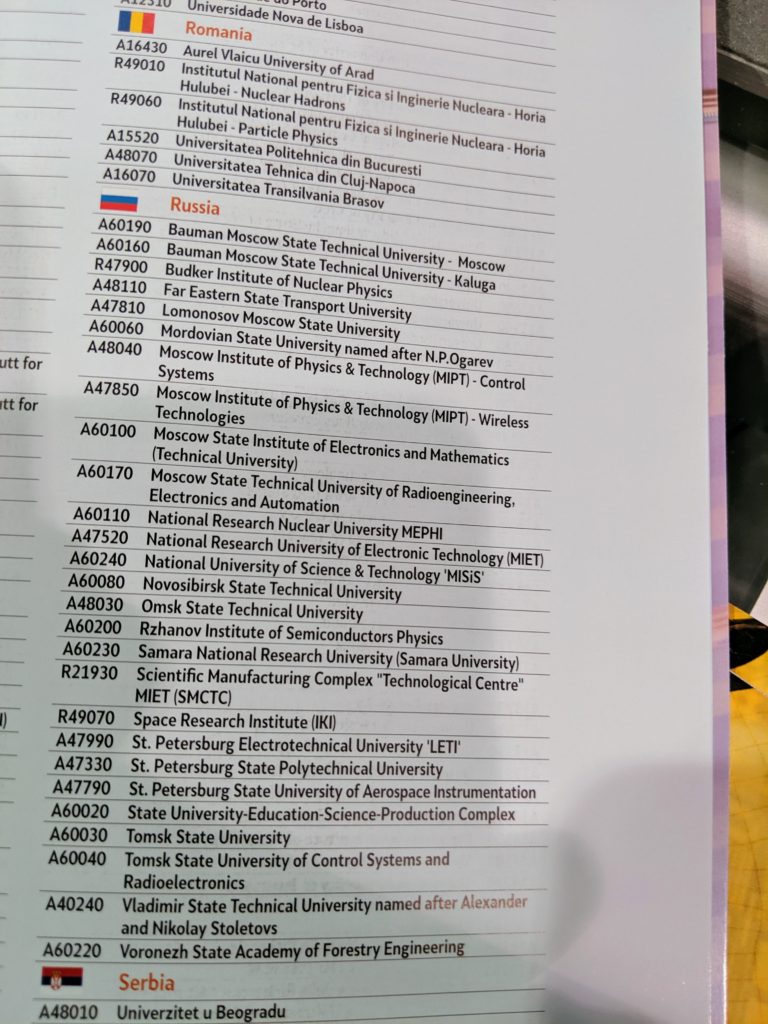

有趣的是,Europractice在俄罗斯甚至在鄂木斯克都有客户。 承认谁在鄂木斯克设计ASIC。

Europractice有许多俄罗斯公司,包括鄂木斯克的某人:

有些公司的商业模式对我来说有些神秘。 例如,我不明白下面的这家公司如何在利基Eclipse插件中生存。 我想他们通过出售一些咨询服务可以获得最大的收益。

有些公司我不了解他们的收入。 例如,这是一个非常利基的Eclipse插件。 当然,他们不是靠他生活,而是依靠某种咨询。

另一家业务模式不明确的利基公司。 他们将软件可见寄存器的描述转换为Verilog胶合逻辑和其他接口文件。 我猜这家公司可能有一些思科类型的大客户,他们很早以前就迷上了他们的技术并从那时起就向他们付款。

另一个利基公司,业务模式不明显。 它们将可供程序员使用的寄存器描述转换为Verilog和接口文件。 他们可能有一些主要客户,例如Cisco,它在多年前就迷上了他们的工具,并且由于聘请客户来管理他们的工程师实在太可惜了,因此一直在付款。

来自华为的一位忧郁先生介绍了他们在网络芯片方面的成就。 显然,华为对美国EDA工具的依赖程度甚至超过了Android市场和ARM CPU内核。 在我看来,与为ARM内核设计高端竞争产品所需的资源相比,开发同等Synopsys IC编译器所需的资金和技术专家的数量要大得多。

华为代表也参加了展览,脸上带着悲伤的表情。 我注意到,如果美国政府强迫美国EDA公司禁止中国人使用,那么中国人的情况将比现在更糟,因为克隆Synopsys IC编译器在技术上比ARM和Android Market处理器内核更加困难。

自1998年以来,每个DAC都有至少一家公司开发另一种C到Verilog编译器。 早在1998年,那是

我自己的创业公司 。 今年是其他人:

自1998年以来,至少有一家使用DAC在Verilog中编译C的公司。 1998年,这样的公司是我自己的创业公司。 今年其他人:

这位绅士靠出售与所谓的“ Zakladki”(俄语术语,是“ Zakladka”的复数)相反的解决方案来谋生。 我向他解释了该词的含义,他同意这就是他的产品。

这是一个在处理器中制作活的分析器书签的同伴:

我将我的学生女儿带到DAC,以便她可以看到爸爸如何谋生:

我将女儿带到拉斯维加斯,以便她可以看到人们在电子工业这个严酷的工业世界中是如何赚钱的,并意识到爸爸的钱并没有长在树上:

展览后的聚会:

展览后的聚会上:

展览结束后,我与Wave Comnputing的同事们一起举办了MIPS开放开发人员日。 我们有一些上述公司的人,还有来自俄罗斯硅谷混合信号设计服务公司

VivEng的俄罗斯朋友,在俄罗斯硅谷Zelenograd也有一些客户。 首先,我们进行了

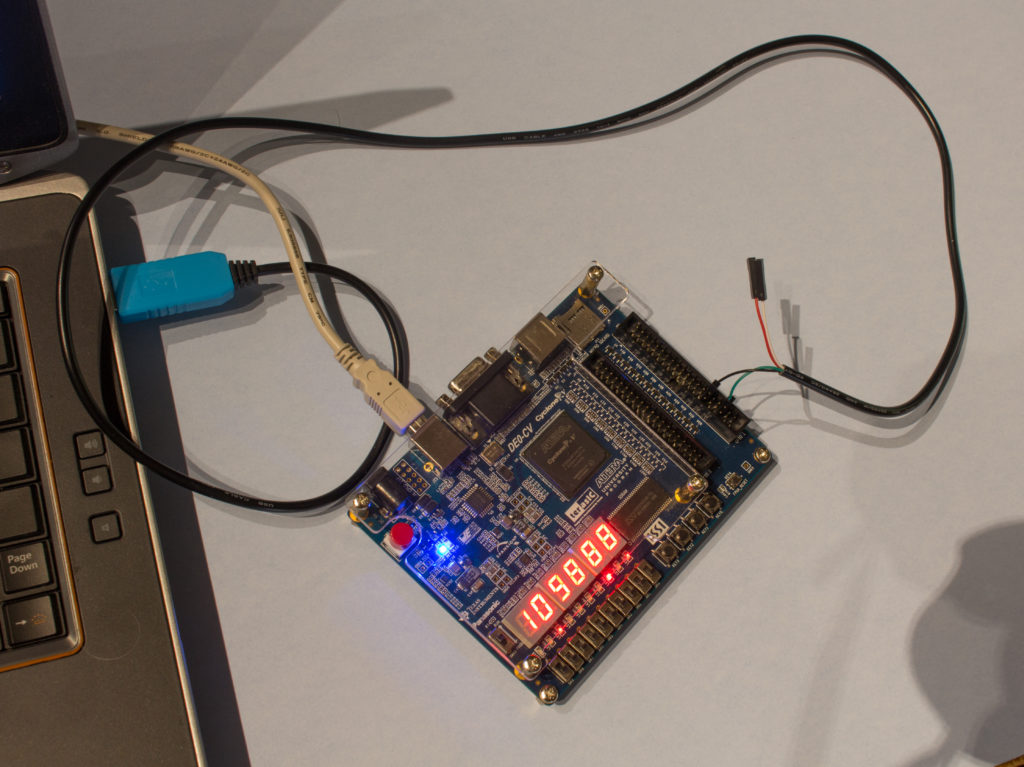

介绍 ,然后,参与者在Digilent Nexys4 DDR和Terasic DE10-Lite FPGA板上进行了一些练习。

然后,我与同事一起举办了MIPS Open研讨会。 所描述的一些公司的同志参加了此次会议,其中包括那些授权嵌入式FPGA和EDA工具,销售生产服务,进行验证培训以及制造芯片的同志。 还有我来自俄罗斯公司

VivEng的老朋友 。 我和我的同事展示了

这些幻灯片 ,然后参与者在FPGA Digilent Nexys4 DDR和Terasic DE10-Lite上试用了示例。

要重复结果,可以下载并合并两个软件包:

如果要重现结果,可以执行以下操作:

- 转到https://www.mipsopen.com/mips-open-components/mips-open-fpga-getting-started-guide 。

- 下载标准的MIPSfpga 2.0软件包。

- 转到https://github.com/MIPSfpga/mipsfpga-plus 。

- git克隆github.com/MIPSfpga/mipsfpga-plus.git

- 将核心RTL文件从MIPS Open FPGA软件包复制到MIPSfpga +软件包的核心子目录-请参阅https://github.com/MIPSfpga/mipsfpga-plus/tree/master/core中的说明

必须在计算机上安装Intel FPGA Quartus Prime Lite Edition或Xilinx Vivado,以及Codescape GCC裸机工具链。 之后,您可以按照幻灯片中的说明进行操作:

您需要在系统上安装Intel FPGA Quartus Prime Lite Edition或Xilinx Vivado,以及Codescape GCC Bare Metal Toolchain。 之后,您可以按照幻灯片中的说明进行操作:

- cd your_git_directory /木板/ board_directory(例如de10_lite或nexys4_ddr)

- 使所有负载

- 按复位键(或某些板上的KEY 0)以复位处理器。

- 默认的硬编码程序应开始工作。

- cd your_git_directory /程序/ 00_counter(或其他程序)

- 使程序记录uart

- 如果计算机使用的不是ttyUSB0(默认值),则使用串行连接,则:

- 使程序记录UART = 1(或2、3等)

- 通过USB至UART上传的程序现在正在运行。

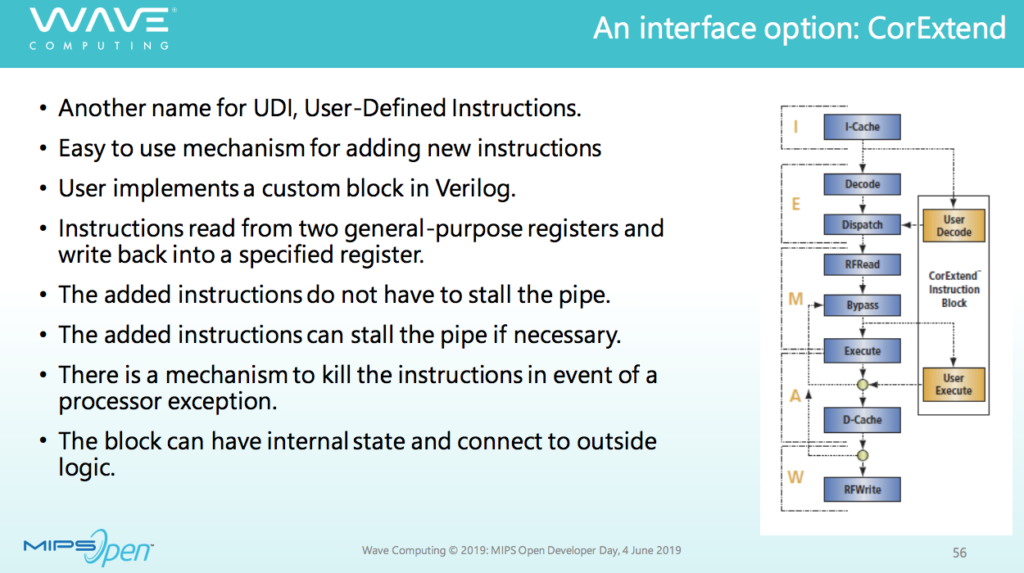

在演示中,我展示了如何在处理器中嵌入一个块,该块可以解码并执行主系统命令的其他指令,这些指令可由系统设计人员在芯片上确定。 该模块可以合成并成为微电路的一部分,或者在FPGA / FPGA中进行配置。

附加指令与主要指令一起沿处理器管线移动。 它们从程序员可见的通用寄存器接收数据,并将结果返回到寄存器。 这些指令还可以将某些状态保存在协处理器中。 如果发生异常,它们可以被异常杀死,例如,在此指令之后的管道中:

演示文稿有详细的解释,说明如何向MIPS microAptiv UP CPU内核添加用户定义的处理器指令,以及如何将其与一些用于FPGA板的简单SoC合成在一起:

示例文本中的Verilog硬件代码段。 该代码在寄存器传输级别(RTL)上实现了用于计算卷积神经网络的专用指令:

自定义CorExtend模块的一个片段,该模块为神经网络计算的特殊情况实现了用户定义的指令(UDI):

明天我将飞往俄罗斯,为另一个研讨会提供帮助,不是针对电子和EDA专业人士,而是针对有兴趣探索数字微电子设计职业的孩子。 为此,我创建了一个与MIPS Open FPGA内核集成的简单2D视频处理器,以及一个用于VGA的纯硬件(无CPU或软件)游戏的示例。 孩子们喜欢游戏,我将使用游戏设计来教他们RTL方法论的基础:

接下来的

7月8日(周一)

,我将为Zelenograd的学童讲授开发数字电路的基础知识 。

我为他写了一些在FPGA上实现简单子画面图形的示例。 由Verilogue合成的电路在VGA屏幕上绘制精灵。

这是一个干净的硬件中的工作示例(

github上的源代码 )。 海军作战的一种变体,其中红色鱼雷卫星搜寻敌方的蓝色十字架:

这是硬件和软件结合的一个例子-来自精灵的致敬。

硬件部分和

软件部分 :

是的,我答应在拉斯维加斯演讲。 这是一块:

天黑了但还没有人拥挤的时候,观看拉斯维加斯大道的景色:

晚上已经是傍晚,但没有人流的时候,在大道上的街景:

在拉斯维加斯的两天里,我没有赌博的机会,所以当我们返回圣何塞的飞机在拉斯维加斯机场登机时,我花了1美元玩:

这段时间里,我从来没有在拉斯维加斯玩过,因为我在展览周围走来走去,谈论电子话题,然后我举办了一个研讨会。 但是,尽管如此,我仍然指出,登机时损失了1美元: