中间制造工艺,不同类型的晶体管以及许多其他选择会给电子制造工艺增加不确定性。

电子制造商正在为下一波尖端制造工艺做准备,但是他们的客户会困惑于一堆令人困惑的选择-是使用5 nm工艺技术开发芯片,等待3 nm还是在两者之间进行选择。

与3 nm不同,到达5 nm的路径定义明确。 此后,随着工厂增加中间制造工艺(如6 nm和4 nm),情况变得混乱。 切换到这些技术过程中的任何一个都是非常昂贵的,并且收益并不总是显而易见的。

另一个令人担忧的原因是制造基础的萎缩。 在最先进的技术流程中,制造商的选择很少。 该行业有几家领先的制造商,但随着时间的流逝,由于成本的急剧增加和用户群的减少,该领域已经缩小。 通常,制造商越少,技术和价格标签的选择就越少。

如今,三星和台积电是

仅有的两家采用7纳米或更小工艺工艺的

制造商 ,尽管这可能会改变。 英特尔和中国公司中芯国际正在开发先进的制造工艺。 英特尔不是商业生产领域的最大参与者,但是10纳米制程技术的发展却遇到了问题。 尚不清楚中芯国际是否能够提供7纳米,因为该主题仍处于研发阶段(采用10纳米制程技术的英特尔公司也会发生同样的事情)。

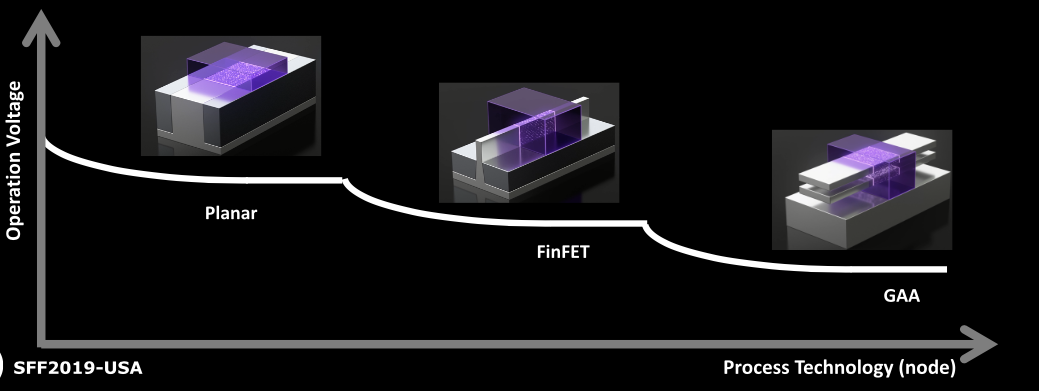

至于更先进的制造工艺,三星和台积电使用finFET晶体管工作于7纳米工艺,两家制造商都将继续在5纳米工艺。 与传统的平面晶体管不同,finFET是具有更好性能和更少泄漏的三维结构。

然后,在3 nm时,三星将从finFET转移到新的nanosheet FET晶体管架构,这是finFET技术的发展。 台积电尚未透露其3 nm的计划,使许多客户陷入困境。 消息人士称,TSMC权衡了各种选择,包括纳米层,纳米线和强制finFET。 英特尔,台积电和其他公司也正在研究新的高级封装形式,以作为缩小规模的可能选择。

但是,晶体管技术的尺寸在3 nm时可以朝不同的方向发展。 finFET仍然可以发挥作用,但是这项技术需要一些突破。 显然,根据一个从事该领域工作的组织的发展计划,业界必须为过渡到3 nm工艺技术的新体系结构和下一代2 nm中间工艺技术做准备。

Imec程序总监director口直人说:“ 5 nm仍然是finFET。” -假设在3 nm,我们将进入从finFET到其他架构的过渡期。 我们相信这些将是纳米层。”

纳米层FET与环绕栅晶体管(GAA)的体系结构有关。 这不是唯一的选择。 “这个行业非常保守。 Horiguchi表示,其参与者将竭尽所能,从finFET到极限。 -在3纳米制造工艺中,我们有机会使用finFET。 但是我们将需要进行一些finFET创新,并总体上进行改进。”

芯片制造商会继续使用7 nm工艺技术,迁移到5 nm,3 nm还是中间产品? 7 nm可为几乎所有应用程序提供足够的性能,因此此过程将持续很长时间。 外面有几个高性能的选择,而且它们的价格都更高。 我们将看看这些技术是否有时间准时出现。

各种制造工艺的工作电压是平面晶体管,finFET和纳米层FET。

各种制造工艺的工作电压是平面晶体管,finFET和纳米层FET。生产废墟

该芯片由许多充当开关的晶体管组成。 几十年来,集成电路的发展与摩尔定律保持一致,根据摩尔定律,器件上晶体管的密度在18到24个月内翻了一番。

制造商以类似的节奏引入了具有更高密度的晶体管的新技术工艺,这使业界可以从晶体管数量上降低芯片成本。 在每个制造过程中,制造商将晶体管规格缩放0.7倍,从而使该行业在相同的能耗和面积减少两倍的情况下将生产率提高40%。

集成电路行业遵循了这一公式并蓬勃发展。 自1980年代以来,它为打折的快速PC铺平了道路。

据IBS称,到2001年,已经有至少18家制造商的工厂可以生产130nm的芯片,这在当时是一种先进的技术工艺。 同时,又出现了一些新的制造商,在其他人的工厂生产定制芯片。 此外,芯片制造是为开发它们但没有自己的产品的实验室进行的。

到本世纪末,生产和制造过程的成本猛增。 由于无法应对价格上涨,许多芯片制造商转而使用fab lite模式。 他们在家中生产了一些芯片,其余的则外包了。

随着时间的流逝,越来越少的芯片制造商在自己的工厂生产先进的设备。 有些人完全摆脱了生产或放弃了这项业务。

但是,在2000年代,出现了硅车间的商业模式。 研讨会落后于英特尔和其他技术公司,但使设计公司可以使用各种流程。

下一个主要变化发生在20 nm阶段,这是传统的平面晶体管碰壁并遇到

短沟道效应 。 作为回应,英特尔于2011年改用22 nm的下一代晶体管技术finFET。 研讨会改用16/14 nm的finFET。

FinFET与平面晶体管相比具有多个优势。 “在该方案中,整个晶体管垂直延伸,从而使沟道上升至基板上方,并且阀门围绕鳍片的三个侧面缠绕。 阀门增加的接触面积可以更好地控制泄漏电流,”应用材料公司的Matt Kogorno和宫下俊彦写道。 Kogorno是全球产品管理总监,Miyashita是首席技术专家。

FinFET也是更复杂的设备,因此很难为每个后续技术流程生产和定型它们。 结果,研发成本上升到了天堂。 因此,如今,全面的流程变更节奏已从18个月增长到2.5年甚至更长。

集成电路价格也继续上涨。 据Gartner称,开发28nm平面器件的成本从1000万美元到3500万美元不等。 相比之下,设计7 nm单芯片系统(SoC)的成本从1.2亿美元到4.2亿美元不等。

Gartner的分析师Samuel Wen说:“开发成本在很大程度上取决于SoC的复杂性。” -三分之二用于芯片开发。 剩下的就是潜艇的开发,口罩的成本和产量的提高。 随着时间的流逝,设计成本也会下降。”

但是,价格趋势已经改变了集成电路世界的格局。 随着时间的流逝,越来越少的公司有能力为最先进的制造工艺支付芯片设计费用。 他们中的许多人依靠车间来解决生产问题。

客户数量的减少以及生产成本的增加影响了生产高级芯片的车间的格局。 例如,在16/14纳米市场上剩下五个制造商/生产车间:GlobalFoundries,英特尔,三星,台积电和联电。 中芯国际还与finFET一起使用14纳米制程技术。

在7 nm处发生了另一个过渡。 技术过程和生产成本持续增长,投资回报率已经成为问题。 结果,GlobalFoundries和UMC去年停止尝试开发7 nm制程技术。 两家公司都继续在16/14 nm市场上运营。

为了进一步发展,三星和台积电全速奔向7纳米及以上。 在经历了几次延迟之后,英特尔计划在2019年中期以10 nm的速度开始生产,到2021年以7 gm的速度开始生产。 同时,中芯国际不承诺任何截止日期。

但是,并非所有车间客户都需要先进的制造工艺。 28纳米芯片市场蓬勃发展。 “这完全取决于产品的特性,” Gartner的Ven说。 -有些产品要求最高性能。 开发人员仍然可以使用过时的技术流程。 对于不需要高性能的应用,芯片可以在N-1和N-2制造工艺中使用。”

其他人呼应他。 “从经济角度来看,有多少公司可以负担得起当今最新的硅? 他们的人数正在减少。 在要求极高性能的市场中,这种需求将永远存在。 但是在供应链中,就数量而言,中间会形成破裂。 要求最苛刻的客户需要7、5,甚至有一天3 nm的工艺流程。 联电企业管理副总裁沃尔特·恩(Walter Eun)说,但其他所有人都放慢了脚步。

但是在某些情况下,需要最先进的芯片-这些是服务器和智能手机。 也有大量与AI芯片相关的新创业公司。 许多公司设计用于机器学习和深度学习的芯片。

“没有人争辩说,即使是在非技术市场中,计数速度要比今天快10倍总是有商业价值和竞争优势的。 深度学习技术的所有这些独特成就就是证明。 D2S主管藤村明(Aki Fujimura)说,对不断提高的计算机功能的要求几乎没有止境。

“对计算能力的需求已经经历了几次重大转变,起初是GPU,后来是深度学习,” Fujimura说。 -深度学习是找到合适模式的一项大规模技术,而训练神经网络是持续优化的任务。 现在,世界已经提出了一种处理大量数据并将其转化为有用逻辑结论的程序形式的有用信息的机制,所需的计算量随可用数据量的增加而增加。 而且,由于所有领域的数据量都呈指数级增长,因此至少在深度学习领域,保证了对计算能力的要求显着增长。”

尚不清楚AI芯片是否需要5 nm或更大的技术工艺,但是肯定需要提高计算能力。 但是,迁移到这些技术过程并不会变得更容易或更便宜。

5纳米和3纳米

同时,在2018年初,台积电又达到了一个里程碑,成为世界上第一家使用7纳米制程技术的制造商。 三星后来加入了7纳米竞赛。 根据IC Knowledge和TEL的信息,制造7 nm芯片的过程主要基于finFET,并且包括制造栅极步长为56至57 nm,最小放置金属导体(金属间距)为40 nm的芯片的芯片。

在第一个7 nm版本中,TSMC使用193 nm

浸没式光刻和多次图案化。 台积电今年承诺使用极紫外光刻(EUV)发布7 nm的新版本。 EUV简化了工艺步骤,但它是一项昂贵的技术,并且有其自身的一系列困难。

台积电正在准备其新的5纳米制程技术,计划于2020年上半年发布。 台积电在5 nm处的新技术将比7 nm快15%,能耗降低30%。 明年推出的第二种5纳米制程技术将提高7%。 两种版本都将使用EUV。

台积电已经获得了5纳米的订单。 IBS主管汉德尔·琼斯(Handel Jones)说:“预计苹果,海思和高通公司将获得大笔订单。 “到2020年第四季度,衬底的数量将达到每月40,000-60,000。”

对于TSMC,在5 nm处的跃迁速度小于7 nm。 首先,5nm是一个全新的过程,具有更新的EDA工具和专利。 另外,它更昂贵。 据Gartner称,平均而言,开发5nm器件的成本从2.1亿美元到6.8亿美元不等。

一些芯片制造商希望摆脱7nm而不花5nm的钱。 因此,台积电最近推出了一种新的6纳米制程技术,该技术较便宜,但存在一些折衷。

台积电董事在上次会议上说:“数字N6和N5似乎没有什么不同,但实际上差距很大。” -在N5处,与N7相比,逻辑密度增加了80%。 N6相比N7仅18%。 如您所见,晶体管的逻辑密度和效率之间存在很大差异。 结果,N5芯片的总功耗较低。 切换到N5有很多好处。 但是N5是一个成熟的技术流程,客户需要花费一些时间为其开发新产品。 N6的优点在于,如果他们已经在N7下拥有一个项目,那么他们将只需花费很少的精力。 他们可以升级到N6并获得某些好处。 而且,根据产品和市场的特征,客户将决定该怎么做。”

同时,三星推出了5纳米技术,该技术将于2020年上半年面世。与7纳米技术相比,三星在finFET上采用的新型5纳米工艺技术可将逻辑压缩率降低25%,功耗降低20%,速度提高10%。

三星还推出了新的6纳米制程技术,为客户提供了另一种选择。 “ 6nm具有7nm的可扩展性和知识产权的重复利用优势,”三星工厂研讨会营销副总裁Ryan Lee说。 三星计划已经开发了4纳米制程技术finFET。 到目前为止,关于该技术几乎没有公开信息。

5 nm之后,许多成熟的制造工艺成本为3 nm。 但是3 nm不是for夫。 据IBS称,开发用于3纳米工艺技术的设备的成本从5亿美元到15亿美元不等。 开发过程的成本从40亿美元到50亿美元不等,生产成本从15美元到20美元不等。 IBS的琼斯说:“ 3纳米晶体管的成本应该比同等可用性的5纳米高20-25%。” “我们预计与5 nm finFET相比,效率提高15%,能耗降低25%。”

三星是唯一宣布计划开发3纳米制程技术的公司。 为此,研讨会将切换到圆形晶体管,纳米层的体系结构。 台积电尚未透露计划,这就是为什么有人认为该公司落后的原因。 琼斯说:“三星采用3nm工艺,很可能在2021年投入量产。” “ TSMC通过与三星保持同步来加快开发速度。”

台积电在3 nm处检查纳米层FET,纳米线FET甚至finFET。 扩展finFET技术的方法之一是在通道(即德国)中使用高迁移率材料。 当今的finFET器件在通道中使用硅或硅锗(SiGe)。 通过增加锗的混合量,可以增加通道的迁移率,即电子通过设备的速度。 这里的问题是缺陷管理。

扩展finFET技术很有意义。 3 nm的finFET提供了从5 nm的过渡路径。 但是,有问题。 从理论上讲,当鳍片宽度达到5 nm(接近当前状态)时,finFET技术将陷入死胡同。 Imec的Horiguchi说:“今天,我们在标准单元中为NMOS使用两个鳍,为PMOS使用三个鳍。” -3 nm的重要方面之一是我们需要切换到标准设计的单鳍架构。 一条鳍应该足够好。 为了将finFET技术扩展到N3,我们需要一种特殊的技术来提高单个鳍的功率并减少背景杂散现象。”

除了finFET的高迁移率之外,下一个选择是GAA。 2017年,三星推出了3 nm的多桥沟道FET(MBCFET)。 MBCFET-纳米层FET。 三星的MBCFET试用版将于2020年上市。

纳米层芯片优于finFET。 在finFET中,快门从三个侧面围绕鳍片弯曲。 在纳米层中,快门位于鳍片的四个侧面,从而可以更好地控制电流。

与5 nm相比,三星的纳米层FET的逻辑区域效率提高了45%,功耗降低了50%,速度提高了35%。 三星三星表示:“由于无法将电源电压降低到0.75 V以下,因此finFET结构在可扩展性方面有其自身的局限性。我们通过使用纳米层的创新将电压降至低于0.7 V,” Samsung Samsung说。

GAA技术有几种类型,包括纳米层FET和纳米线FET。 GAA本身是继finFET之后的下一步。 在该系统中,finFET位于其侧面,然后分成水平部分。 件形成通道。 快门材料包裹着每一层。

与纳米线FET相比,这种电路具有更宽的通道,即更高的生产率和激励电流。 “纳米层具有更有效的宽度,” Imec Horiguchi说。 “纳米线在静电方面做得更好。” 但是它们的横截面很小。 就有效通道宽度而言,这将不会带来优势。”

GAA体系结构有几个问题。 通常,与5nm的finFET相比,它们的增加非常小。 使用这种技术制造芯片非常困难。

« GAA 3 , — , -

Lam Research . – , , finFET. , GAA , finFET».

– SiGe . « , -, . », — , Applied Materials. « , ».

电池组至少应由三层SiGe和三层硅组成。然后将微小的薄片结构应用于包装。之后,形成带有凹槽的绝缘层,然后形成内部隔板。然后,从超晶格中去除SiGe层,使硅层之间留有空白。每个硅层形成器件中片或通道的基础。然后,您需要应用介电常数高的材料来创建快门。纳米线之间存在最小距离。很小问题是要把工作厚度的金属放在那里。多年来,业界一直致力于创建GAA技术,但是仍然存在一些问题。“主要电容之一是寄生电容,”金说。-如果您问我GAA技术的主要问题是什么,那么其中有两个。内部分隔器和基板绝缘。”接下来是什么?

GAA ? « - . N3. . , , . », — Imec.

GAA finFET . GAA finFET. , Imec 42 , – 21 . , finFET 5 48 28 .

Imec p- GAA . , Imec 25 . . , 9 .

finFET 5 . Imec Ge nFinFET Gmsat/SSsat PBTI. .

我们还将看到finFET技术是否可以扩展到3 nm。还不清楚纳米层芯片是否会按时出现。在这种不断变化的格局中,存在许多未知数和不确定性,也没有时间表来澄清这种情况。