如果您认为英特尔的“帮派”是

摩尔定律的最忠实拥护者,那么您可能还没有听说菲利普·黄(Philip Wong)在这个问题上如何传播。 台积电(TSMC)公司研究副总裁Wong在最近的Hot Chips会议上作了一次演讲,指出摩尔定律不仅活着而且很好,而且具有相当多种技术技巧,但事实并非如此。不到三十年。

“他还没死,”他对在Hot Chips出席的人们说。 “他不放慢脚步,甚至不咳嗽。”

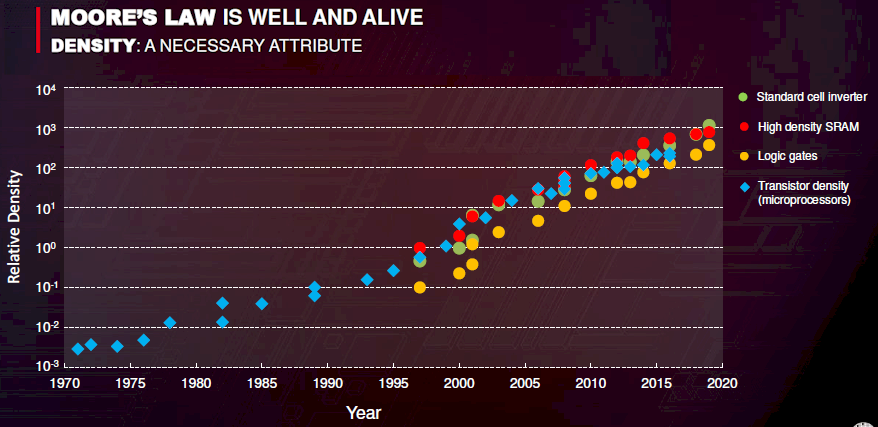

听黄先生的话,维持摩尔定律的唯一必要措施就是提高密度。 尽管他承认时钟频率已经达到

极限 ,标志着

丹纳德缩放定律的终结,但他说,晶体管的密度可以提高速度和能效。

摩尔定律还活着

摩尔定律还活着最终,密度提高多少都没有关系。 Wong认为,主要的问题是,公司可以将更多的晶体管填充到更小的体积内,从而提高能源效率。 在短期内,这可以通过古老的,行之有效的方式来实现,即通过改进CMOS的制造技术,从而最终生产出具有较短栅极长度的晶体管。

台积电已经掌握了7纳米制程技术,并正在向5纳米迈进。 Wong表示5 nm制程技术开发生态系统已经准备就绪,该公司已经开始生产有风险的样品-也就是说,制程技术和开发工具已经准备就绪,并且正在生产工作基板。 在最近一次的股东大会上,台积电宣布计划在2020年上半年开始大规模生产5 nm芯片。 事实证明,该公司的计划已经包括3纳米制程技术。

但是所有这些技术都是基于

平面 [flat]芯片的,Wong承认这种方法最终将停止扩展。 他解释说:“如果我们遵循二维增加的道路,那么我们已经达到了数百个原子,很快我们所有的原子都将耗尽。”

但这并不意味着密度增加的结束。 他指出,即使在丹纳德(Dennard)扩大规模的末期,半导体行业的一些创新也支持密度图的上升。 尤其是

出现了应变硅和

高k电介质技术,然后是三维结构技术FInFet(Fin场效应晶体管)。 现在,为了超越7 nm,正在研究DTCO(设计技术协同优化)技术。

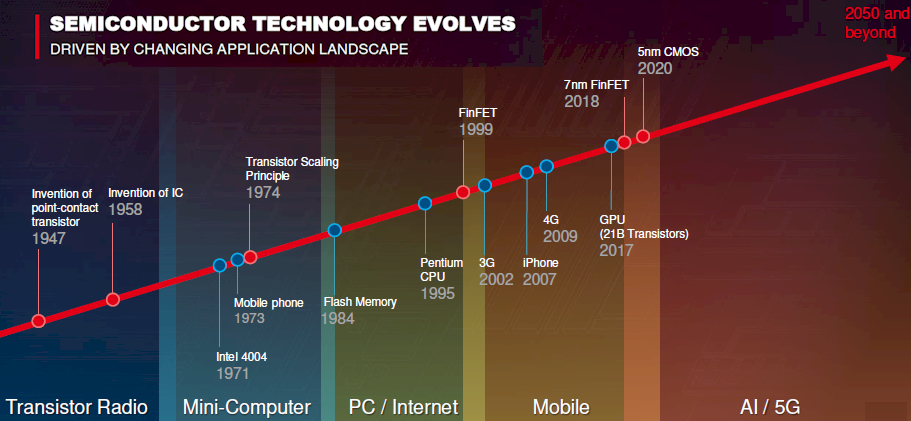

所有这些创新的发生是因为有必要开发需要更快,更节能的硬件的新计算平台。 这种发展催生了1970年代的微型计算机,1980年代的PC,1990年代的互联网以及当今的移动设备。 每个阶段都需要通过改进半导体制造来提高密度。 Wong认为,以下需求将来自人工智能和5G。

半导体技术演进

半导体技术演进为了确保摩尔的执政党不会停止,需要进行哪些创新?

在短期内,即使芯片本身没有变得更密集,总体计算密度和存储密度也将增加用于创建2.5D结构的多芯片盒的芯片组的使用。 Wong表示,与将这些组件集成到单个封装中相比,这种工艺已经使单个小芯片的特定工艺技术变得不那么重要了。

台积电拥有自己的2.5D机箱版本,该芯片具有晶片上晶圆上晶片(CoWoS)技术(英特尔的嵌入式多管芯互连桥或EMIB与该技术竞争)。 CoWoS允许您创建多芯片机箱,在插入器上固定芯片组和合适的内存,并使用TSV垂直触点连接它们。 CoWoS的最有趣实现是Nvidia Tesla V100 GPU加速器,其中GV100 GPU装有高带宽内存(HBM)。 英特尔,AMD和赛灵思正在集成更多芯片组。

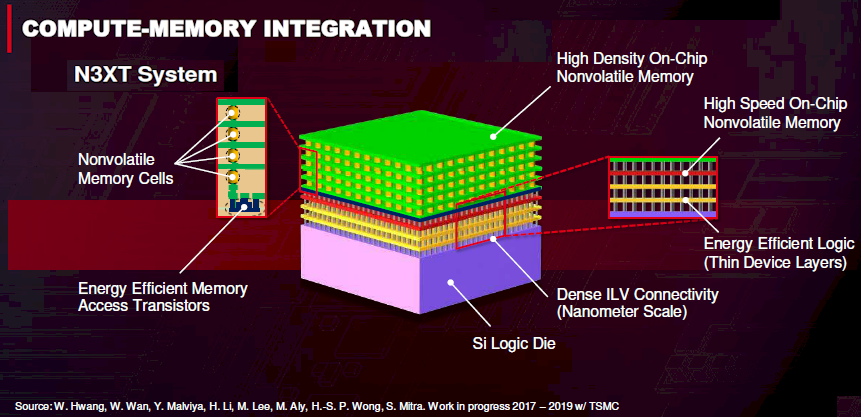

但是2.5D增加密度的可能性不是无限的。 更具可扩展性的解决方案将需要真正的三维晶体管放置技术。 Wong认为,为此,单片三维N3XT技术最适合基于新材料以及内存与逻辑的紧密集成。 N3XT是“计算系统的纳米工程技术”,自2015年以来一直在学术界进行讨论,但是现在诸如台积电(TSMC)等公司已经开始认真对待它,它有很大的商业化机会。

Wong展示了带有此类设备外观示意图的幻灯片。 它由高能效逻辑层(黄色),高速存储器(红色)和高容量非易失性存储器(绿色)组成,这些层交替排列。 所有这些都位于普通的硅逻辑晶体(紫色)上。

N3XT系统

N3XT系统这里的主要内容是通过ILV,Inter-Layer-Via(层间垂直访问)来组合各个层。 与微米级TSV不同,ILV可以纳米级形成。 尽管这是N3XT技术的一个极其重要的组成部分,但Wong对此却知之甚少。 但是很明显,台积电正在紧密合作,并且已经注册了与之相关的多项专利。

在三维芯片中,内存和逻辑的交织非常重要,因为它允许您缩短它们之间的距离,从而确保高吞吐量和低信息传递延迟,这对于AI和5G之类的应用而言是必需的。 在CMOS中,内存和逻辑不能交错,因为逻辑晶体管的蚀刻需要1000摄氏度左右的温度,这会破坏生产中的相邻层。 它需要可以在400度左右的温度下制造的东西。

事实证明,在过去的几年中,研究人员研究了似乎适用于在相对较低温度下生产高速晶体管的新材料。 与当今生产中使用的硅材料不同,在那里使用基于二硫化钼过渡金属(TMD)的单层,其中包括钼,钨和硒等元素。

TMD材料显示出载流子的高迁移率-电子很容易通过狭窄的通道通过它们。 方便的是,仅需要具有这样的特性即可制造尺寸小于2-3 nm的晶体管。 Wong说,台积电实验室正在测试基于二硫化钨的实验性TMD基板。

纳米材料的另一候选者是碳纳米管。 Wong说他们做了实验性的变化,显示出作为半导体的良好材料性能。 基于碳纳米管的逻辑和SRAM的工作原型已经组装好,其中包括来自MIT研究人员的RISC-V变体。

关于存储器,Wong认为,最可能进行三维集成的将是:SST-MRAM(自旋转移矩磁阻随机存取存储器,使用电子自旋动量转移进行记录的磁阻随机存取存储器); PCM

相变存储器 ;

随机存取电阻式存储器 ReRAM; 基于CBRAM单元可编程金属化的存储器; FERAM

铁电随机存储器 。 所有这些都是具有随机访问权限的非易失性存储器,它不需要在向其写入新信息之前擦除单元的操作。 市场上已经有一些选件-Everspin MRAM,Samsung MRAM,Crossbar ReRAM和Intel 3D XPoint(大多数情况下是PCM的变体)。

新型内存

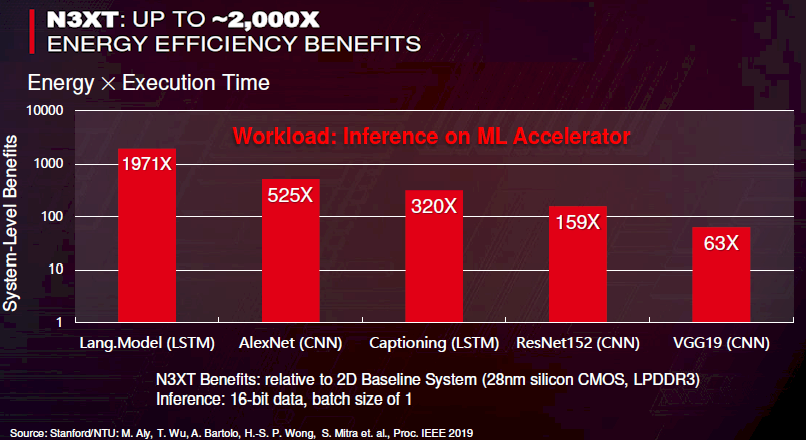

新型内存研究人员模拟了N3XT设备的性能,并将它们与逻辑和存储容量大致相同的传统二维芯片进行了比较。 根据他们的研究,在使用各种测量机器学习算法速度的方法的情况下,N3XT技术的设备效率是二维设备的63-1971倍。

N3XT相对于二维系统的优势

N3XT相对于二维系统的优势听起来很有希望。 但是Wong并没有传播这些技术在未来30年内将如何保持摩尔定律所必需的技术改进的速度。 例如,向新的纳米材料的过渡将使我们相对于二维组件,晶体管密度增加一倍。 但是最终,我们将遇到原子限制。

从理论上讲,如果每18个月可以使三维设备的高度加倍,则可以提高每平方表面积的密度。 当然,对于移动和嵌入式设备,这种方法将很快变得太麻烦了,七到八代之后用于数据中心计算机的芯片将放置在4米的天花板内。

为了使一切能够持续工作数十年,并使密度不断适应摩尔定律,需要开发Wong未提及的其他技术创新。 但是,如果您生产TSMC之类的芯片,则必须接受研究人员将不断为您提供新的技术候选人,这些技术仅需要来自新的,要求更高的任务的请求就可以进入市场。 而且,如果您回想起这个故事,那么肯定会出现这样的任务。