引言

一旦我需要实现一小块CAM (关联存储器)。 在阅读了Xilinx如何在BRAM (静态存储块)或SRL16 (16位移位寄存器)上执行此操作后,我有些难过,因为它们的实现占用了大量空间。 我决定尝试自己做。 第一种选择是实施额头。 展望未来,它几乎马上就传到了我,而且,设计的目标频率仅为125 MHz。

建筑学

首先,请考虑问题的陈述。 因此,我们需要一个小型的CAM,其字宽为8-64位,深度为16-1024个字。 我需要在CAM中进行二进制搜索,但后来发现,使用TCAM (三态关联内存)制作资源非常便宜,并且会稍微影响时序。 Kintex7系列的下限频率为125 MHz。 让我们开始吧! 我们的CAM将由以下几行组成,每行将对应一个地址并存储一个字:

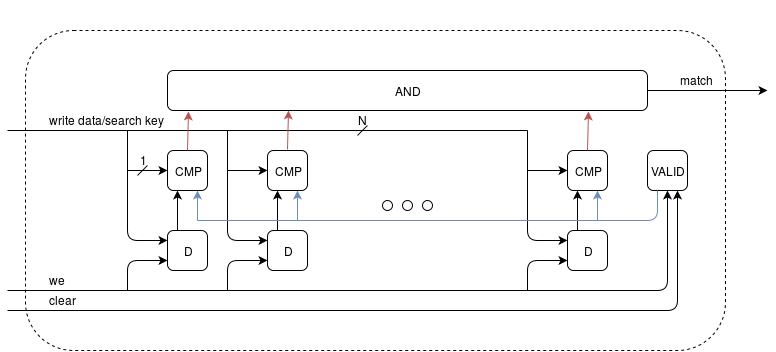

图1.一行CAM的结构

在图1中, D是用于存储数据的常规D触发器;行中这些触发器的数量与CAM中输入数据字的宽度相对应。 有效 -D触发器,如果该行中的数据相关,则存储“ 1”。 CMP是一个比较器,如果VALID ='1',则会比较相应搜索关键字总线位的值。 写入数据 -用于按位写入的数据总线连接到相应的D( N-字宽CAM), 我们 -写入标志, 清除 -复位VALID(数据线无效)。 AND-比较器的N个输出进行逻辑AND,如果该行中的搜索成功,则match-标志变为1。

因此,我们只有一行可以搜索。 现在将它们结合起来:

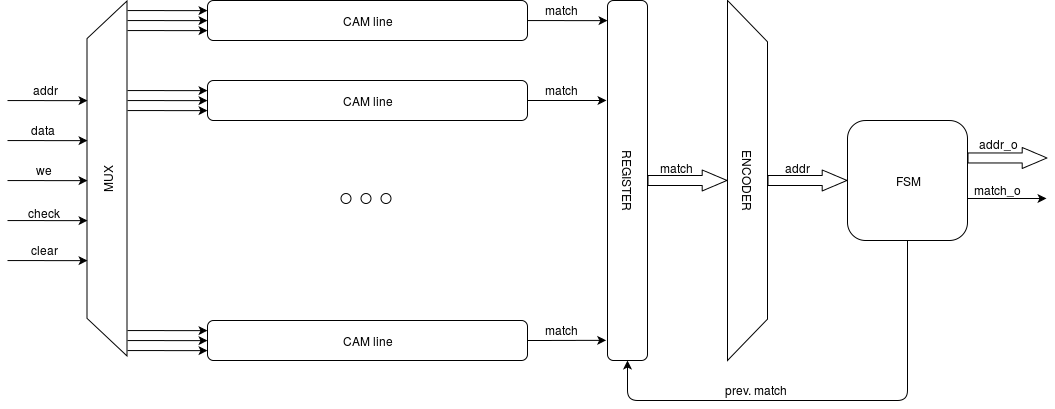

图2. CAM结构

在图2中, CAM_line是图1中的实际CAM行, MUX是输入地址多路复用器, MATCH REGISTER是存储匹配标志值的寄存器, ENCODER是将匹配总线转换为找到的最低匹配地址的解码器。 FSM是一个控制有限状态机,以前有。 match从MATCH REGISTER 中删除与已发送地址相对应的位,以便ENCODER切换到下一个找到的地址。 CAM的界面如下:

表1. CAM接口

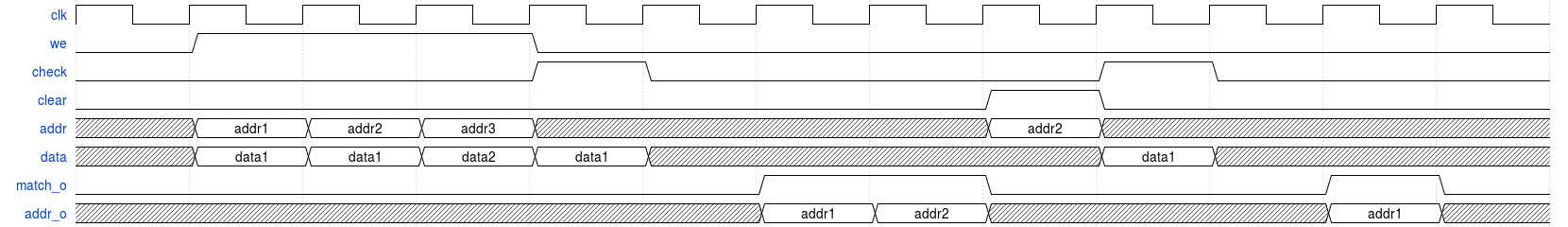

下面的图3是此接口操作的时序图,它首先显示了在CAM中记录三个单词,然后显示了成功的搜索,擦除和再次搜索:

图3. CAM接口的时序图

因此,我们对CAM进行了描述,让我们继续进行综合。

综合性

我们将在Xilinx ISE中进行合成,以将结果与XAPP1151中获得的结果进行比较。

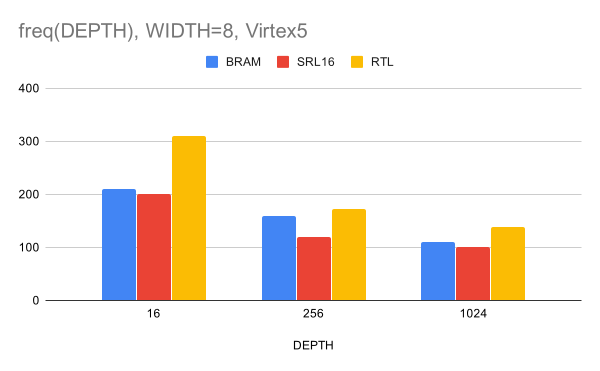

图4.对于8位数据总线宽度, XST (合成器作为ISE的一部分)对CAM深度的频率依赖性

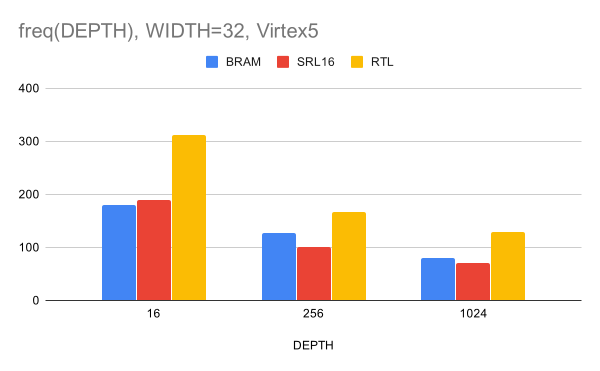

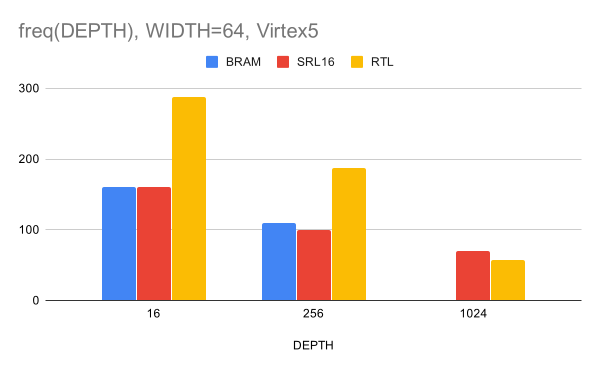

图5.对于32位数据总线宽度,XST之后的频率与CAM深度

图6.对于64位数据总线宽度,XST之后的频率与CAM深度

在图6中,没有Virtex5的数据,因为这种大小的CAM不适合现有的BRAM。 我们还注意到,对于64位的宽度和1024的深度,我们的结果比SRL16上的实现稍差。 现在,让我们继续进行XC7K325T的 Vivado合成。 结果如下:

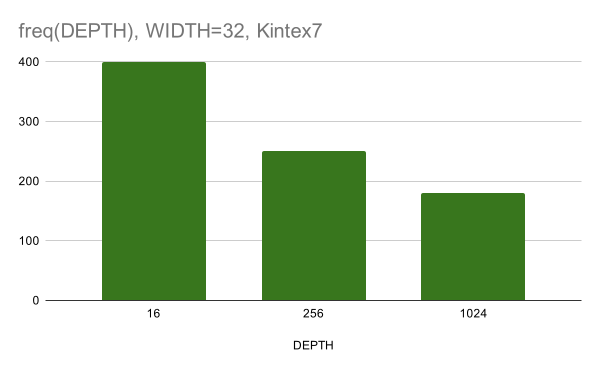

图7.对于32位数据总线宽度, PnR (芯片上块的放置和信号跟踪)对CAM深度的频率依赖性

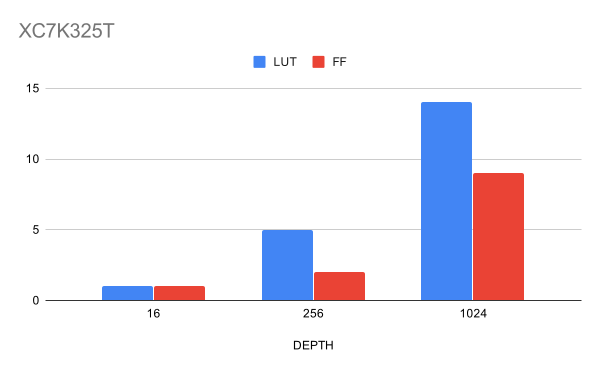

图8. 32位数据宽度(%)中各种CAM深度的资源利用率

重要的是要注意,在Vinado上获得的结果是在PnR之后获得的,这意味着该设计在跟踪方面没有困难。

TCAM

如上所述,从CAM TCAM获得这种方法并不是一个特别的问题。 只需为数据位添加一个屏蔽总线,然后将其逐位分配到比较器中,以便在将数据与密钥进行比较时,它们会考虑其值。 这样的变化不会导致频率降低或资源消耗的严重增加,因此我们免费获得了TCAM。

结论

因此,我们能够完成任务。 最终的设计使第7个Xilinx FPGA系列可以接收足够大的CAM,且其频率高于目标125 MHz。 与XAPP1151的比较结果对我来说是出乎意料的,我以为BRAM上的实现尽管在资源上非常昂贵,但在频率上将超过前面的实现。 但是,不要这么早就庆祝胜利, 本文描述了Xilinx CAM IP内核,例如,它允许基于BRAM获得深度为32K单元,频率为155 MHz的CAM。 通过添加管线的阶段,或通过从小型管线中收集大型CAM,可以在本文提出的版本中实现此结果,但是我无法立即预测它是否适合芯片。 将来,我将尝试在BRAM上实现类似的功能,但现在,感谢您的关注。