最近,我们参与了阿波罗(Apollo)机载控制计算机

的修复工作 ,该计算机负责控制,导航和监视飞向月球的阿波罗飞行任务。 这台历史悠久的计算机是最早使用集成电路(IC)的计算机之一,其处理器完全基于NOR阀构建(第二种类型的IC,即读出放大器,用于计算机的内存中)。 在本文中,我将描述CPU的体系结构和设计。

阿波罗控制计算机架构

Apollo控制计算机的分开的托盘。 左托盘包含基于“或非”门的逻辑。 在右侧-内存和辅助组件。

Apollo控制计算机的分开的托盘。 左托盘包含基于“或非”门的逻辑。 在右侧-内存和辅助组件。阿波罗制导计算机(AGC)于1960年代开发,允许阿波罗飞行任务飞向月球。 在大多数计算机占用一台全尺寸冰箱到整个房间的空间的时候,AGC是独一无二的-它足够小,可以装在阿波罗号飞船上,重32公斤,占用的空间不超过0.03 m

3 (30升)。

AGC计算机为15位。 遇到一个不是2的幂的单词大小,这很奇怪,但是在1960年代,甚至在字节流行之前,计算机就使用了各种单词大小。 15位提供了登陆月球的足够精度(并在必要时以两倍和三倍精度使用了数据),因此16位只会不必要地增加计算机的尺寸和重量。

AGC指令位于一个15位字中,由3位(指示操作代码)和12位(指示内存中的地址)组成。 不幸的是,这些数量仍然不够,因此计算机使用了许多技巧和变通办法,并且该体系结构相当笨拙。 一个12位的存储器地址只能访问4K字。 同时,AGC在主RAM中有2K个字,在核心存储器中有36K个字。 为了访问所有存储器,AGC使用了复杂的存储器组交换系统和多个寄存器。 换句话说,只能以256个字的块来访问存储器,而以稍大一些的ROM来访问。

操作码的3位不足以直接指示34条可能的指令,因此AGC使用了一些技巧,其中包括扩展指令值以及某些指令仅对某些存储单元有意义的事实。 此外,还使用了诸如存储器中的“魔术”地址之类的技巧-例如,写入“右移寄存器”单元执行了按位移位,因此不需要单独的“右移”指令。 也有指令同时组合多个动作。

即使按照1960年代的标准,AGC架构也非常简单。 尽管它是在复杂而强大的大型机时代创建的,但AGC的功能却非常有限。 在功率和架构方面,它可以与早期的微处理器相媲美。 它的优势在于其紧凑的尺寸和强大的功能,可提供实时数据输入和输出。

下面的架构图显示了AGC的主要组件。 我用彩色突出显示了我更详细介绍的部分。 AGC有一小组寄存器,还有一个仅处理加法的简单算术模块。 他只有ROM 36K字和RAM 2K字。 “写总线”是在组件之间传输数据的主要方式。 解码指令和序列发生器为AGC生成控制脉冲。

AGC框图

AGC框图该图的大约一半被内存占用,这反映了一个事实,即AGC架构在许多方面都是围绕其内存开发的。 像1960年代的大多数计算机一样,AGC也使用核存储器,将每个位存储在缠绕在丝网上的微小铁氧体环(核)中。 由于每个位都需要一个单独的物理核心,因此这种内存的数量从根本上少于现代半导体的数量。 内核上内存的一个显着特征是从内存中读取一个单词将其删除,因此在每次访问后都必须重写该值。 AGC还具有固定的ROM存储器,即著名的

缝合核 -它们用于存储程序,并通过电线进行物理缝合(请参见下文)。

针芯上的特写存储器

针芯上的特写存储器NOR阀

AGC是最早使用IP的计算机之一。 这些第一批IP的可能性非常有限; 在AGC芯片上(下面),只有六个晶体管和八个电阻,它们一起实现了一个具有三个输入的NOR门。

双NOR阀,AGC提供三个输入。 晶体外部的十根线连接到IC的外部触点。

双NOR阀,AGC提供三个输入。 晶体外部的十根线连接到IC的外部触点。NOR阀的示意图表示如下。 这是最简单的逻辑门:如果所有输入均等于零,则输出等于1。 您可能会感到惊讶,但是一个或非门足以创建一台计算机。 NOR是通用阀:可以在其基础上制造任何其他逻辑阀。 例如,当组合所有NOR输入时,我们得到一个反相器。 将逆变器放置在NOR的输出端后,我们得到一个OR阀。 通过将反相器放置在NOR门的输入端,我们得到一个AND门。 从这些门,您可以构建更复杂的逻辑:触发器,加法器和计数器。

NAND阀具有相同的多功能性。 在现代电路中,由于技术原因,与非门相比,与非门的使用更多。 在热门课程“

从NAND到Tetris ”中,介绍了如何从NAND阀创建计算机,直至实现“ Tetris”游戏。 首先,由NAND(NOT,AND,OR,XOR,多路复用器,多路分解器)构成一组逻辑门。 然后,从它们(触发器,加法器,计数器,ALU,寄存器)以及从它们(计算机)创建更大的构建块。

如果“或非”门在所有输入上都为0,则“或非”门为1;如果至少一个输入为1,则“或非”门为0。

如果“或非”门在所有输入上都为0,则“或非”门为1;如果至少一个输入为1,则“或非”门为0。在AGC中,通常会遇到诸如RS触发(设置-重置,设置/重置)之类的组件。 该电路由两个或非门组成,并存储一个数据位。 位1存储在设置输入中,位0存储在复位输入中,即,施加到设置输入的脉冲1,关闭上阀并打开下阀,因此输出1变为输出。施加到复位输入的脉冲1,执行相反的操作。 如果两个输入都设为0,则触发器会记住其先前的状态,起到驱动器的作用。 在下一节中,我们将展示如何从触发器中创建寄存器。

两个或非门的RS触发器。 一个阀在打开时会关闭另一个。 其中一个输出上方的线表示它是另一输出的补充。

两个或非门的RS触发器。 一个阀在打开时会关闭另一个。 其中一个输出上方的线表示它是另一输出的补充。寄存器

AGC有一小组寄存器,用于将值临时存储在主存储器之外。 主寄存器是许多算术运算中使用的驱动器(A)。 它还有一个计数器寄存器Z,算术块寄存器X和Y,缓冲区B,返回地址Q以及其他一些寄存器(在现代计算机中,堆栈用于调用例程并从例程中返回,但是在那个时代,程序员需要自己编写堆栈以进行递归) 为了访问存储器,有一个存储器地址寄存器S,对于数据有一个存储器缓冲寄存器G。而且,AGC在主存储器中有寄存器-例如,输入/输出计数器。

下图显示了AGC寄存器方案,针对只有一位和两个寄存器的情况进行了简化。 每个寄存器位都有一个使用前述方案(蓝色和紫色)的触发器。 数据通过写总线(红色)在寄存器之间来回传输。 要写入寄存器,触发器将通过清除信号(CQG或CZG,绿色)复位。 然后,“写”信号(WQG或WZG,橙色)允许沿写总线传输的数据设置相应的寄存器触发。 要读取寄存器,读取信号(RQG或RZG,青色)将触发输出通过记录放大器传递到记录总线,并在AGC的其他部分中使用。 全寄存器方案比较复杂,它具有几个16位寄存器,但是基本方案如下。

简化的AGC寄存器操作

简化的AGC寄存器操作记数表说明了三个关键点。 首先,寄存器电路由“或非”门构建。 其次,围绕写总线建立数据移动。 最后,寄存器的动作取决于在正确的时间到达的某些控制信号。

算术模块

大多数计算机都有执行算术和布尔运算的

算术逻辑设备 。 与现代计算机相比,AGC的算术模块非常有限:它仅执行16位量的加法运算,因此它被称为算术模块,而不是算术逻辑模块(其余操作通过各种技巧执行;例如,通过加法执行减法,然后再进行加法运算)对于其中一个自变量,位将反转,依此类推)。

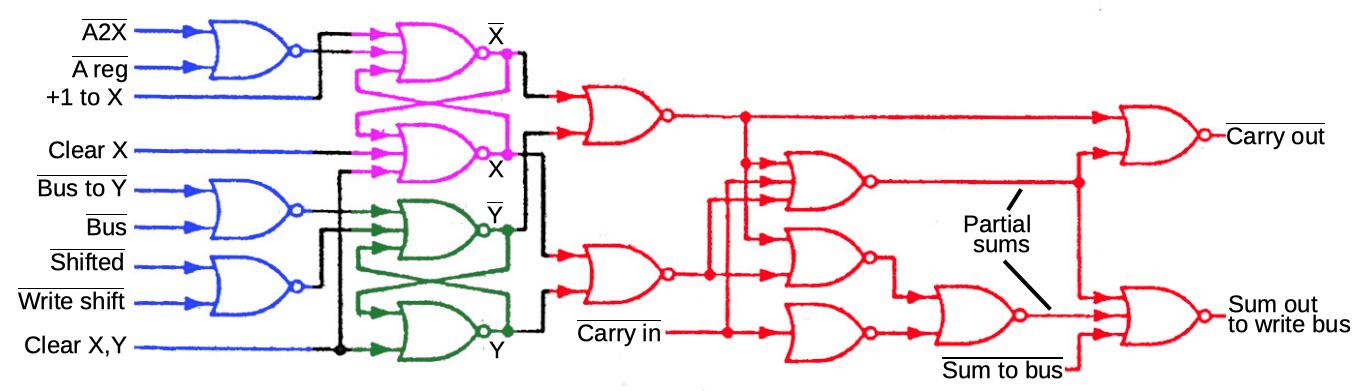

下图显示了AGC算术模块的一位。

全加法器 (红色)计算两位的总和并进位。 传输被传输到下一个加法器-通过这种方式,它们可以组合起来以添加更长的单词(以加快传输的传输速度,例如111111111111111 + 1,AGC使用带

传输跳过的加法器)。

寄存器X和Y(紫色和绿色)为加法器提供两个输入位。 它们是使用NOR阀上已经描述的触发器来实现的。 蓝色循环根据控制信号将值写入X和Y寄存器。 该方案非常复杂,因为它允许您通过在寄存器中进行移位来存储常量和值,但是我将不讨论该主题。 注意控制信号A2X,该信号将寄存器A的值传送到寄存器X。 我们待会儿再找他。

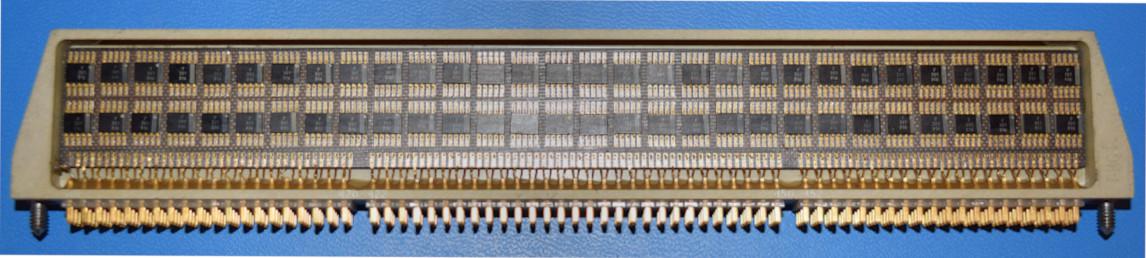

下图显示了AGC电路的物理实现。 该模块为寄存器和一个算术模块实现四个位。 黑色矩形是平面IP。 每个模块有两个板,每个板有60个芯片,以及总共240个NOR门。 算术模块和寄存器由四个相同的模块组装而成,每个模块处理四个位。 这类似于

微处理器部分 。

算术模块和寄存器由四个相同的模块组装而成。 模块安装在A8至A11的插槽中。

算术模块和寄存器由四个相同的模块组装而成。 模块安装在A8至A11的插槽中。指令执行

本节介绍了AGC执行该指令的操作顺序。 特别是,我将展示ADS(添加到存储)指令的工作方式。 该指令从存储器中读取值,并将其添加到驱动器(寄存器A),并将和保存在加法器和存储器中。 这是一条指令,但执行时AGC需要执行几个步骤,并且许多值在此处和此处移动。

指令计时器的实现归功于磁芯上的存储子系统。 特别是,从内存中读取值会擦除存储的值,因此,每次读取后,必须将值写回。 另外,访问存储器时,地址的指定和数据的接收之间存在延迟。 结果,每个时钟周期花费12个步骤进行读取和后续记录。 每个时间间隔(从T1到T12)持续不到一微秒,整个周期持续11.7μs,称为存储周期时间(MCT)。

AGC的可擦写磁芯存储模块。 它存储2公斤,每个位使用单独的微型铁氧体环存储。

AGC的可擦写磁芯存储模块。 它存储2公斤,每个位使用单独的微型铁氧体环存储。MCT是执行指令的基本内存单元。 典型的指令需要两个时钟周期:一个从内存中提取指令,第二个执行操作。 因此,一条典型指令需要两个MCT(23.4μs),每秒可给我们43,000条指令(与现代处理器及其每秒数十亿条指令相比,这非常慢)。

AGC处理指令,将它们分成子命令,每个子命令占用一个内存时钟周期。 例如,一条ADS指令由两个子命令组成:ADS0(加法)和STD2(调用下一条指令)。 下图显示了AGC中数据的移动,以执行ADS0指令。 从左到右有12个小节。

最重要的步骤如下:

T1:操作数地址从指令寄存器B复制到存储器地址寄存器S,以开始从存储器读取。

T4:操作数从存储器读到存储器数据寄存器G。

T5:操作数从G复制到加法器Y。驱动器A的值复制到加法器X。

T6:加法器计算和U,并将其复制到存储器G的数据寄存器中。

T8:程序计数器Z被复制到存储器地址寄存器S,以准备从存储器接收下一条指令。

T10:来自存储器G的数据寄存器的总和被写回到存储器中。

T11:将金额U复制到驱动器A。

尽管这是一条简单的求和指令,但是在此处的12个时隙中,会不断传输大量数据。 并与这些动作的每一个相关联的是特定的控制信号。 例如,间隔T5中的信号A2X将值从驱动器A复制到寄存器X。要将寄存器G复制到寄存器Y,需要两个控制脉冲:RG(读G)和WY(写Y)。 在下一节中,我将解释AGC控制模块如何为每个指令生成必要的控制信号。

控制模块

像大多数计算机一样,AGC控制模块对每条指令进行解码并生成控制信号,以告知处理器的其余部分需要做什么。 AGC使用由NOR阀组成的预编程控制模块来生成信号。 AGC不使用微码; 他没有微指令和控制存储器,因为这会占用过多的物理空间。

AGC控制模块的核心称为交叉点生成器。 它需要一个子命令和一个时间段,并为此组合生成控制信号。 可以想象成格子的形式,子命令在一个方向上传播,子命令在另一个方向上传播,每个交点都有自己的控制信号。

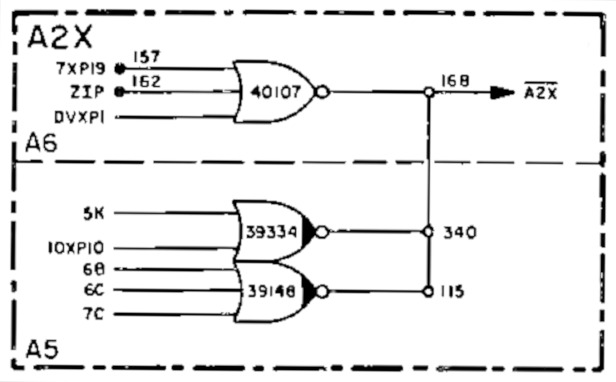

交集生成器需要很多组件,并分为三个模块。 这是A6模块。 注意增加的导线会改变电路。 这是用于地面测试的模块的早期版本; 飞行模块已经没有电线。

交集生成器需要很多组件,并分为三个模块。 这是A6模块。 注意增加的导线会改变电路。 这是用于地面测试的模块的早期版本; 飞行模块已经没有电线。为了提高效率,最终控制模块进行了高度优化。 具有相似行为的指令将由相交生成器组合并一起处理,从而减小了所需电路的大小。 例如,AGC的指令为“添加到具有双精度的驱动器”(DAS)。 由于它大约等于单个单词的两个加法,因此交集生成器中的DAS1和ADS0子命令具有公共逻辑。 下图显示了时间间隔T5的交集生成器电路,并且突出显示了ADS0子命令(使用信号DAS1)的逻辑。 例如,从DAS1和T5的组合生成5K信号。

但是5K和5L信号是什么? 这是另一个优化。 许多控制脉冲通常被馈送在一起,因此相交生成器不是直接生成控制脉冲,而是生成相交的中间信号。 例如,5K产生控制脉冲A2X和RG,5L产生控制脉冲WY。 下图显示了如何生成A2X信号:8个不同信号(包括5K)中的任何一个都生成A2X。 类似的电路会生成其他控制信号。 这些优化使减小交集生成器的大小成为可能,但它仍然很大,并增加到多达三个模块。

综上所述,我们可以说控制模块负责告诉CPU如何执行指令。 首先,指令被分解为子命令。 交集发生器为每个时间间隔和子命令生成必要的控制脉冲,告诉寄存器,运算模块和存储器它们需要做什么。

通常,指令由两个子命令组成,但也有例外。 一些指令(例如乘法或除法)需要使用许多子命令,因为它们包含许多步骤。 相反,TC处的跳转指令只使用一个子命令,因为它只需要调用下一条指令。

其他处理器使用不同的方法来生成控制信号。 6502和许多其他早期的微处理器使用可编程逻辑阵列(PLA)对指令进行解码,该阵列通过只读存储器实现AND / OR逻辑。

微处理器6502。

微处理器6502。结论

这是对Apollo车载控制计算机的一次激动人心的参观。 为了避免过多拉伸,我集中介绍了ADS添加指令和一些控制脉冲(A2X,RG和WY)。 我希望您对如何使用NOR阀这样的原始元素组装计算机有所了解。

架构中最明显的部分是数据路径:算术模块,寄存器和数据总线。 AGC寄存器基于NOR门的简单触发。 尽管AGC算术模块只能执行加法运算,但计算机仍可以处理整个运算集,包括乘法,除法和布尔运算。

但是,数据路径仅是计算机的一部分。 , , . , AGC, , .

, AGC , «», . , 60% 1963. AGC NOR-.

AGC , Tektronix

AGC , Tektronix